CMOS 32-BIT SINGLE CHIP MICROCOMPUTER

**S1C33000**

コアCPUマニュアル

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

CMOS 32-BIT SINGLE CHIP MICROCOMPUTER

## S1C33000 Core CPU Manual

このマニュアルは、32ビットシングルチップマイクロコンピュータS1C33 Family各機種のコアとして使用されるRISC型32ビットCPU S1C33000 の機能と命令セットについて解説しています。

チップ上の周辺回路を含むハードウェアの詳細については、S1C33 Family各機種のテクニカルマニュアルを参照してください。

### データの表記について

本マニュアルでは、データサイズや数値を以下のように記述しています。

#### データサイズ

8ビット: バイト, Byte, B

16ビット: ハーフワード, Half word, H

32ビット: ワード, Word, W

#### 数値の表記

16進数: 0x0000000, 0xFF等

2進数: 0b0000, 0b1111等

その他の数値は基本的に10進数です。ただし、明らかに2進数と判別できるものについては0bを省略している場合もあります。

#### 命 令

命令や記述例は基本的に小文字( a ~ z )を使用しています。実際に記述する場合は大文字も使用することができます。命令のオペランドや機能説明に使用するシンボルについては、"4.1 記号の意味"を参照してください。

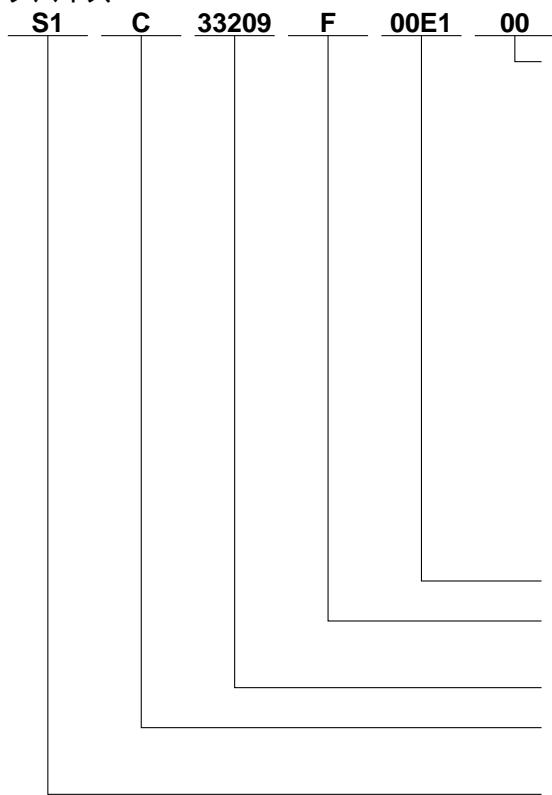

## 製品型番体系

### デバイス

#### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

#### 仕様

[D: ベアチップ、F: QFP]

#### 機種番号

[C: マイコン、デジタル製品]

[S1: 半導体]

### 開発ツール

#### 梱包仕様

[00: 標準梱包]

#### バージョン

[1: Version 1]

#### ツール種類

- Hx : ICE

- Dx : 評価ボード

- Ex : ROMエミュレーションボード

- Mx : 外部ROM用エミュレーションメモリ

- Tx : 実装用ソケット

- Cx : コンパイラパッケージ

- Sx : ミドルウェアパッケージ

#### 対応機種番号

[33L01: S1C33L01用]

#### ツール分類

[C: マイコン用]

#### 製品分類

[S5U1: 半導体用開発ツール]

## - 目 次 -

|        |                                     |    |

|--------|-------------------------------------|----|

| 1      | 概要                                  | 1  |

| 1.1    | 特長                                  | 1  |

| 1.2    | ブロック図                               | 2  |

| 1.3    | 入出力信号                               | 3  |

| 2      | アーキテクチャ                             | 4  |

| 2.1    | レジスタセット                             | 4  |

| 2.1.1  | 汎用レジスタ( <i>R0</i> ~ <i>R15</i> )    | 4  |

| 2.1.2  | プログラムカウンタ( <i>PC</i> )              | 4  |

| 2.1.3  | プロセッサステータスレジスタ( <i>PSR</i> )        | 5  |

| 2.1.4  | スタックポインタ                            | 6  |

| 2.1.5  | 算術演算レジスタ( <i>ALR</i> , <i>AHR</i> ) | 7  |

| 2.1.6  | レジスタの表記とレジスタ番号                      | 8  |

| 2.2    | データの形式                              | 9  |

| 2.3    | アドレス空間                              | 12 |

| 2.4    | ポートアドレス                             | 13 |

| 2.5    | 命令セット                               | 14 |

| 2.5.1  | 命令の種類                               | 14 |

| 2.5.2  | アドレッシングモード                          | 16 |

| 2.5.3  | 即値拡張( <i>EXT</i> )命令                | 18 |

| 2.5.4  | データ転送命令                             | 21 |

| 2.5.5  | 論理演算命令                              | 21 |

| 2.5.6  | 算術演算命令                              | 21 |

| 2.5.7  | 乗算・除算命令                             | 22 |

| 2.5.8  | 積和演算命令                              | 25 |

| 2.5.9  | シフト&ローテート命令                         | 26 |

| 2.5.10 | ビット操作命令                             | 27 |

| 2.5.11 | プッシュ&ポップ                            | 27 |

| 2.5.12 | 分岐命令・ディレインド命令                       | 28 |

| 2.5.13 | システム制御命令                            | 31 |

| 2.5.14 | スキャン命令                              | 31 |

| 2.5.15 | スワップとミラー命令                          | 32 |

| 3      | CPUの動作と処理状態                         | 33 |

| 3.1    | CPUの処理状態                            | 33 |

| 3.2    | プログラム実行状態                           | 34 |

| 3.2.1  | プログラムのフェッチと実行                       | 34 |

| 3.2.2  | 命令の実行サイクル数                          | 34 |

| 3.3    | トラップ(割り込みと例外)                       | 35 |

| 3.3.1  | トラップテーブル                            | 35 |

| 3.3.2  | トラップ処理                              | 36 |

| 3.3.3  | リセット                                | 37 |

| 3.3.4  | ゼロ除算例外                              | 38 |

| 3.3.5  | アドレス不整例外                            | 38 |

| 3.3.6  | NMI(マスク不可能な割り込み)                    | 38 |

| 3.3.7  | ソフトウェア例外                            | 38 |

| 3.3.8  | マスク可能な外部割り込み                        | 39 |

|       |                             |    |

|-------|-----------------------------|----|

| 3.4   | パワーダウンモード .....             | 40 |

| 3.4.1 | HALTモード .....               | 40 |

| 3.4.2 | SLEEPモード .....              | 40 |

| 3.5   | バス権解放状態 .....               | 41 |

| 3.6   | デバッグモード .....               | 42 |

| 3.6.1 | デバッグモードの機能 .....            | 42 |

| 3.6.2 | エリア2の構成 .....               | 42 |

| 3.6.3 | ユーザー モードからデバッグモードへの移行 ..... | 43 |

| 3.6.4 | デバッグ用レジスタ .....             | 43 |

| 3.6.5 | デバッグモード時のトラップ .....         | 45 |

| 3.6.6 | デバッグ例外の同時発生 .....           | 45 |

| 4     | 命令の詳細説明 .....               | 46 |

| 4.1   | 記号の意味 .....                 | 46 |

| 4.1.1 | レジスタ .....                  | 46 |

| 4.1.2 | 即値 .....                    | 46 |

| 4.1.3 | メモリ .....                   | 46 |

| 4.1.4 | ビット・ビットフィールド .....          | 47 |

| 4.1.5 | フラグ .....                   | 47 |

| 4.1.6 | 機能・その他 .....                | 47 |

| 4.2   | 命令コード体系 .....               | 48 |

| 4.3   | 個別命令リファレンス .....            | 52 |

## Appendix

|                           |             |

|---------------------------|-------------|

| S1C33000 クイックリファレンス ..... | Appendix-1  |

| メモリマップとトラップテーブル .....     | Appendix-1  |

| レジスタ .....                | Appendix-1  |

| シンボル .....                | Appendix-2  |

| データ転送命令一覧 .....           | Appendix-3  |

| 論理演算命令一覧 .....            | Appendix-4  |

| 算術演算命令一覧 .....            | Appendix-4  |

| シフト&ローテート命令一覧 .....       | Appendix-5  |

| ビット操作命令一覧 .....           | Appendix-5  |

| 即値拡張命令 .....              | Appendix-5  |

| プッシュ&ポップ命令一覧 .....        | Appendix-5  |

| 分岐命令一覧 .....              | Appendix-6  |

| 積和演算命令 .....              | Appendix-7  |

| システム制御命令一覧 .....          | Appendix-7  |

| その他の命令 .....              | Appendix-7  |

| 即値拡張命令一覧(1) .....         | Appendix-8  |

| 即値拡張命令一覧(2) .....         | Appendix-9  |

| 命令索引 .....                | Appendix-10 |

# 1 概要

S1C33000は32ビットRISC型CPUで、32ビットシングルチップマイクロコンピュータS1C33 Familyの全機種にコアCPUとして使用されます。

S1C33000はセイコーエプソンオリジナルアーキテクチャのもとに、低消費電力、高速動作を要求される組み込み型アプリケーションへの応用を目的として開発され、各種携帯機器からFA/OA機器まで広範囲に対応します。

パイプライン処理とロード・ストア型アーキテクチャにより、動作周波数を上回るMIPS値を達成しました。命令セットはC言語による開発用に最適化されており、Cコンパイラから非常にコンパクトなオブジェクトコードを生成することができます。また、オプションにより搭載可能な乗算器と積和(MAC)命令により、オンチップでDSP機能を実現します。

S1C33000を搭載するS1C33 FamilyマイクロコンピュータはROM、RAM、各種高性能周辺機能ブロックをチップ上に集積し、お客様の必要とするほぼすべての機能を1チップで実現します。

## 1.1 特長

### プロセッサ形式

- セイコーエプソンオリジナル32ビットRISC CPU

- 32ビット長の内部データ処理

### 動作周波数

- DC ~ 33MHz (S1C33 Familyの機種により異なります。)

### 命令セット

- コード長: 16ビット/インストラクション(固定長)

- 命令数: 105命令

- 主要な命令は1サイクルで実行

- 即値拡張命令によりコード内の即値を32ビットまで拡張可能

### 積和演算機能

- 64ビットの積和演算(MAC命令)が可能(16ビット×16ビット + 64ビット)

### レジスタセット

- 32ビット汎用レジスタ 16本

- 32ビット特殊レジスタ 3本

- 32ビット積和演算用レジスタ 2本

### メモリ空間、外部バス

- 命令、データ、I/O混在型のリニア空間

- 最大256MB(28ビット)のメモリ空間をアクセス可能

- 8、16ビットの外部デバイスに対応可能

- 外部グローロジックを不要とする、19エリアのセレクト信号を出力可能

- DRAM等を直接駆動可能(S1C33 Familyの機種により異なります。)

- ハーバードアーキテクチャ

- リトルエンディアン形式

### 割り込み

- リセット、NMI、128本の外部割り込みに対応

- ソフトウェア例外 4本、命令実行例外 2種

- トラップテーブルからベクタを読み込み各処理ルーチンへ直接分岐

### リセット

- コールドリセット(すべてをリセット)

- ホットリセット(バスとポートの状態を保持)

### パワーダウンモード

- HALTモード(コアCPUのみ停止)

- SLEEPモード(コアCPUと高速発振回路を停止)

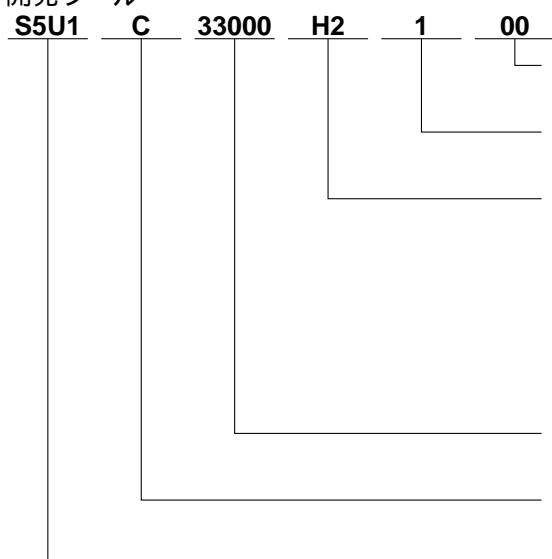

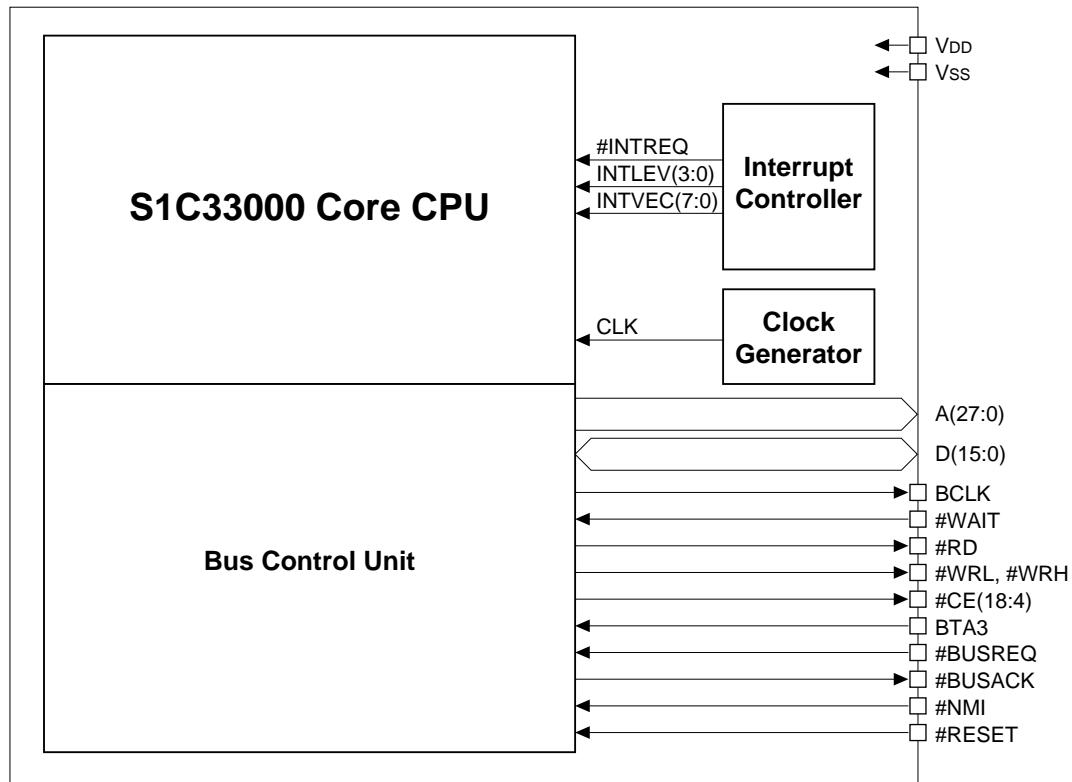

## 1.2 ブロック図

図1.2.1 ブロック図

図は主要なブロックと信号の概要で、実際の回路構成を示すものではありません。

実際のS1C33 Familyの各機種は、上記ブロックを中心に周辺回路ブロックをチップ上に内蔵します。

## 1.3 入出力信号

表1.3.1にS1C33000コアの動作に関する主要な入出力信号を示します。

表1.3.1 入出力信号

| 信号名                     | I/O | 説明                                                                                                                                                                      |

|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>         | I   | + 電源( 電源電圧は機種により異なります。 )                                                                                                                                                |

| V <sub>SS</sub>         | I   | - 電源( GND )                                                                                                                                                             |

| CLK( 内部信号 )             | I   | 入力クロック( クロック周波数は機種により異なります。 )                                                                                                                                           |

| BCLK                    | O   | バスクロック<br>バスサイクルのクロックが出力されます。                                                                                                                                           |

| D(15:0)                 | I/O | データバス<br>双方向の16ビットデータバスです。                                                                                                                                              |

| A(27:0)                 | O   | アドレスバス<br>28ビットのアドレスバスです。                                                                                                                                               |

| #WAIT                   | I   | ウェイトサイクル要求信号<br>低速デバイスがCPUに対して出力する信号で、CPUはこの信号がアクティブな間バスサイクルを延長し、デバイスの入出力終了を待ちます。                                                                                       |

| #RD                     | O   | リード信号<br>データバスからデータを読み込むときに出力されます。バス上の選択されたデバイスは、この信号がアクティブな間にデータをデータバスに出力します。                                                                                          |

| #WRL<br>#WRH            | O   | ライト信号<br>バス上のデバイスにデータを書き込むときに出力されます。この信号がアクティブな間に、選択されたデバイスはデータバスからデータを入力します。<br>#WRLは下位バイト書き込み用、#WRHは上位バイト書き込み用です。<br>S1C33000ではバストローブ方式の信号( #WR/#BSL/#BSH )にも対応しています。 |

| #CE(18:4)               | O   | チップイネーブル信号<br>19エリアに分割されたメモリ領域の外部メモリエリアに個々に対応するチップイネーブル信号です。各エリアのデバイスをアクセスする際にアクティブになります。                                                                               |

| #RESET                  | I   | イニシャルリセット信号<br>Lowレベルの入力でCPUをリセットします。<br>#RESET=0 & #NMI=1: コールドリセット<br>#RESET=0 & #NMI=0: ホットリセット                                                                      |

| BTA3                    | I   | ブートアドレス設定信号<br>ブートアドレスを指定します。<br>BTA3=1: 内蔵ROM( エリア3 )からブート<br>BTA3=0: 外部ROM( エリア10 )からブート                                                                              |

| #NMI                    | I   | NMI要求信号<br>マスクが不可能な割り込み要求信号です。この信号の入力により、CPUはトラップ処理に移行します。また、イニシャルリセットの条件指定にも使用されます。                                                                                    |

| #INTREQ<br>( 内部信号 )     | I   | 割り込み要求信号<br>CPUに対するマスク可能な外部割り込み要求信号です。<br>S1C33 Familyではオンチップ上の割り込みコントローラがこの信号を出力します。<br>割り込み条件が整っていれば、この信号によってCPUはトラップ処理に移行します。                                        |

| INTLEV(3:0)<br>( 内部信号 ) | I   | 割り込みレベル<br>外部割り込みを要求した周辺回路の割り込みレベルが入力されます。この内容は、CPUが割り込みを受け付けた時点でプロセッサステータスレジスタ( PSR )のILフィールドにセットされ、それ以降の低いレベルの割り込みを禁止します。                                             |

| INTVEC(7:0)<br>( 内部信号 ) | I   | 割り込みベクタ番号<br>外部割り込みを要求した周辺回路のベクタ番号が入力されます。CPUは割り込みを受け付けると、トラップテーブルの指定ベクタを読み込んで割り込み処理ルーチンに分岐します。                                                                         |

| #BUSREQ                 | I   | バスリクエスト信号<br>外部バスマスターが出力するバス権解放要求信号です。                                                                                                                                  |

| #BUSACK                 | O   | バスアケノリッジ信号<br>CPUが外部バスマスターのバス権解放要求を受け付けたことを示す信号です。この信号がアクティブな間、CPUはバスをハイインピーダンスにして外部バスマスターに解放します。バス権は外部バスマスターがバス動作を終了して#BUSREQをインアクティブにした段階でCPUに戻ります。                   |

信号名の#はLowアクティブを示します。

実際の入出力信号/端子についてはS1C33 Family各機種のテクニカルマニュアルを参照してください。

# 2 アーキテクチャ

## 2.1 レジスタセット

S1C33000は16本の32ビット汎用レジスタおよび5本の特殊レジスタを内蔵しています。

| 汎用レジスタ | 特殊レジスタ                |

|--------|-----------------------|

| R15    | PC プログラムカウンタ          |

| R14    | PSR プロセッサステータスレジスタ    |

| R13    | SP スタックポインタ           |

| R12    | ALR 算術演算ローレジスタ（オプション） |

| R11    | AHR 算術演算ハイレジスタ（オプション） |

| R10    |                       |

| R9     |                       |

| R8     |                       |

| R7     |                       |

| R6     |                       |

| R5     |                       |

| R4     |                       |

| R3     |                       |

| R2     |                       |

| R1     |                       |

| R0     |                       |

図2.1.1 レジスタセット

### 2.1.1 汎用レジスタ(*R0～R15*)

16本のレジスタR0～R15はデータ演算、データ転送、メモリのアドレッシング等、使用目的が固定されていない32ビット長の汎用レジスタです。IC内部では、これらのレジスタの内容はすべて32ビットデータまたはアドレスとして扱われ、それ以下のビット長のデータはレジスタへのロード時に符号拡張またはゼロ拡張されます。また、アドレスとして用いる場合はアドレスバスが28ビットのため、上位4ビットは無効となります。なお、実際の有効アドレスは各機種のメモリ構成によって異なります。イニシャルリセット時、汎用レジスタの内容は不定となりますので、使用する前にプログラムによる初期化が必要です。

### 2.1.2 プログラムカウンタ(PC)

| 31 | 28 27 | 有効アドレス | 1 0 | PC |

|----|-------|--------|-----|----|

| 無効 |       |        | 0   |    |

図2.1.2.1 PC

プログラムカウンタ(以降PCと記述)は、実行命令のアドレスを保持する32ビット長のカウンタです。S1C33000命令セットではすべての命令が16ビットの固定長のため、PCの最下位ビット(bit 0)は常に0に固定されます。また、アドレスバスが28ビットのため、上位4ビットは無効となります。なお、実際の有効アドレスは各機種のメモリ構成によって異なります。

PCはプログラムによって直接アクセスすることはできません。PCが変更されるのは以下の場合に限られます。

#### (1)イニシャルリセット時

イニシャルリセットによりPCにはブートアドレスがロードされ、そのアドレスから命令の実行を開始します。ブートアドレスを格納する番地はBTA3端子の設定により内蔵ROMの0x0080000番地、または外部ROMの0x0C00000番地となります。

#### (2)各命令の実行時

PCは1命令の実行ごとにインクリメント(+2)され、常に実行中のアドレスを示します。

#### (3)プログラムの分岐時

ジャンプ、サブルーチンコール、割り込みなどのトラップ処理、あるいはサブルーチンからのリターン等、プログラムの分岐時にはPCに分岐先アドレスがロードされます。

また、サブルーチンコールやトラップ処理等、リターンが必要な処理への分岐時は分岐前にPCの内容がスタックにセーブされ、リターン命令実行時にPCに戻されます。

### 2.1.3 プロセッサステータスレジスタ(PSR)

プロセッサステータスレジスタ(以降PSRと記述)はCPUの状態を保持する32ビットレジスタで、実行した命令によって変化します。ロード命令による読み出し、書き込みも可能です。

PSRはプログラムの実行にも影響を与えるため、割り込みや例外の発生時は処理ルーチンへの分岐前にPSRの内容がスタックにセーブされ、リターン( RETI )命令実行時にPSRに戻されます。

イニシャルリセット時、PSRの各ビットは0に設定されます。

各ビットの機能を以下に説明します。

| 31 | 30 | 13  | 12 | 11 | 10      | 9  | 8  | 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|-----|----|----|---------|----|----|---|----|---|---|---|---|---|---|

| -  | -  | ... | -  | -  | IL(3:0) | MO | DS | - | IE | C | V | Z | N |   |   |

図2.1.3.1 プロセッサステータスレジスタ

"-"は未使用ビットを示します。書き込みは無効で、読み出しは常に0となります。

#### N( bit 0 ) ネガティブフラグ

正・負の符号を示します。論理演算・算術演算、シフト命令の実行結果(ディスティネーションレジスタ)の最上位ビット( bit 31 )がNフラグにコピーされます。ステップ除算の実行時には除数の符号ビットがNフラグにセットされ、除算の実行に影響を与えます。

#### Z( bit 1 ) ゼロフラグ

結果がゼロ(0)であることを示します。論理演算・算術演算、シフト命令の実行結果(ディスティネーションレジスタ)がゼロの場合に1にセットされ、ゼロ以外の場合に0にリセットされます。

#### V( bit 2 ) オーバーフローフラグ

オーバーフローまたはアンダーフローが発生したことを示します。加算命令または減算命令において演算値を符号付き32ビット整数として扱う場合に、命令の実行によりオーバーフローまたはアンダーフローが発生すると1にセットされます。加算・減算結果が符号付き32ビット範囲内の場合は0にリセットされます。Vフラグがセットされる条件は以下のとおりです。

- (1)負の整数と負の整数を加算した場合に結果の符号ビット(結果の最上位ビット)が0(正)になった場合

- (2)正の整数と正の整数を加算した場合に結果の符号ビットが1(負)になった場合

- (3)正の整数から負の整数を減算した場合に結果の符号ビットが1(負)になった場合

- (4)負の整数から正の整数を減算した場合に結果の符号ビットが0(正)になった場合

#### C( bit 3 ) キャリーフラグ

キャリーまたはボローを示します。加算命令または減算命令において演算値を符号なし32ビット整数として扱う場合に、命令の実行結果が符号なし32ビット整数の範囲を越えると1にセットされます。結果が符号なし32ビット整数の範囲内の場合は0にリセットされます。Cフラグがセットされる条件は以下のとおりです。

- (1)加算命令で、演算結果が符号なし32ビット整数の最大値0xFFFFFFFFよりも大きい値となる加算を実行した場合

- (2)減算命令で、演算結果が符号なし32ビット整数の最小値0x00000000よりも小さい値となる減算を実行した場合

#### IE( bit 4 ) 割り込みイネーブルビット

マスク可能な外部割り込みを受け付けるか禁止するか制御します。IEビットが1のとき、CPUはマスク可能な外部割り込みを許可します。IEビットが0のときはマスク可能な外部割り込みを禁止します。IEビットの詳細については"3.3.8 マスク可能な外部割り込み"を参照してください。

#### DS( bit 6 ) 被除数符号フラグ

ステップ除算の実行時には被除数の符号ビットがDSフラグにセットされ、除算の実行に影響を与えます。

#### MO( bit 7 ) 積和演算オーバーフローフラグ

積和演算によるオーバーフローを示します。積和( mac )演算実行中に途中結果が符号付き64ビットの有効範囲を越えると1にセットされます。演算はオーバーフローの発生にかかわらず最後まで実行されますので、演算終了後にMOフラグを読み出して結果が有効かどうかを判断します。MOフラグは一旦セットされると、イニシャルリセットかプログラムによって明示的にリセットするまで1を保持します。

## IL( bit 8 ~ bit 11 ) 割り込みレベル

CPUの割り込みレベルを示します。マスク可能な外部割り込み要求は、その割り込みレベルがILビットフィールドに設定されたレベルより高い場合にのみ受け付けられます。また、1つの割り込みを受け付けるとILビットフィールドがその割り込みのレベルに設定され、それ以降はILビットフィールドを再設定するか、割り込み処理ルーチンをreti命令で終了するまで、同じレベルの割り込み要求が再度発生してもマスクされます。

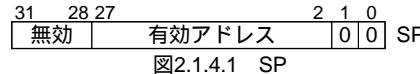

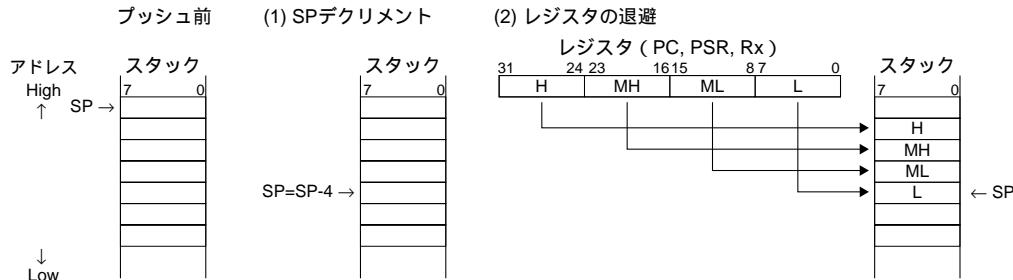

## 2.1.4 スタックポインタ

スタックポインタ( 以降SPと記述 )はスタックの先頭アドレスを保持する32ビットレジスタです。スタックはRAM上に任意に配置可能な領域で、SPで初期設定したアドレスからセーブ( プッシュ )したデータの数に従って低いアドレスの方へ拡大していきます。データをスタックにプッシュする際、SPは書き込みの前に減算( ワード単位、-4 )され、データを書き込む領域を確保します。逆にデータをスタックから取り出す( ポップ )場合は、SPの示すアドレスからワード単位でデータが取り出されます。その後、SPには4が加算され、取り出したデータの領域を解放します。

## A. スタックへのプッシュ動作

## B. スタックからのポップ動作

スタックにプッシュされるのはすべて32ビットの内部レジスタデータのため、SPの下位2ビットはワード境界を示す0に固定されます。また、アドレスバスが28ビットのため、上位4ビットは無効となります。なお、実際の有効アドレスは各機種のメモリ構成によって異なります。

スタックデータのプッシュとポップは以下の場合に行われます。

## ( 1 )call命令実行時

callはサブルーチンコール命令で、スタックを1ワード使用します。call命令はサブルーチンに分岐する前にPCの内容( リターンアドレス、callの次の命令アドレス )をスタックにプッシュします。プッシュされたアドレスはサブルーチン内のRET( リターン )命令によってPCにポップされ、プログラムの実行は呼び出し元のルーチンに戻ります。

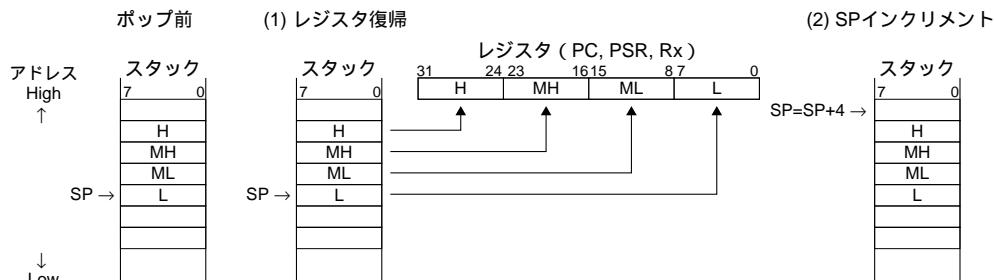

## (2) 割り込みまたは例外の発生時

割り込み、int命令によるソフトウェア割り込みあるいは例外等、トラップが発生すると、CPUはそれぞれの処理ルーチンに分岐する前にPCとPSRの内容をスタックにプッシュします。これはトラップによって、この2つのレジスタの内容が変更されるためです。PCとPSRのデータは図2.1.4.3のようにスタックにプッシュされます。

処理ルーチンからのリターンにはPCとPSRの内容をポップするreti命令を使用します。

図2.1.4.3 トランプ発生時のスタック操作

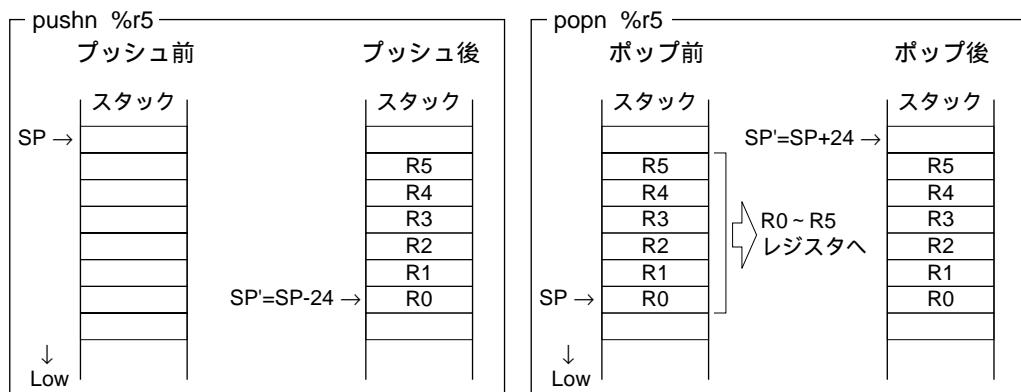

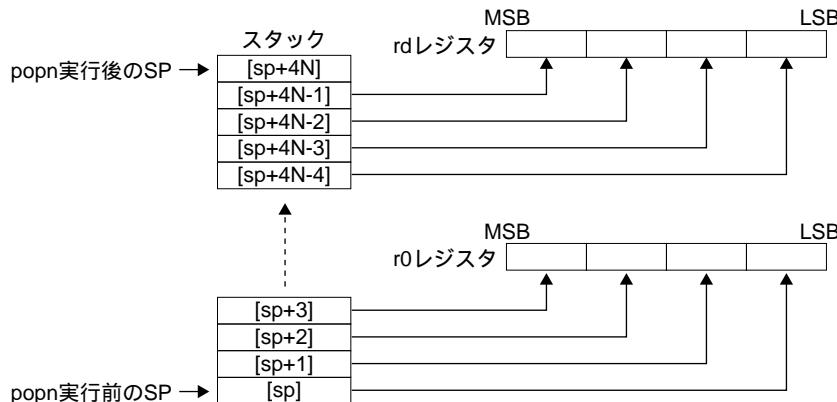

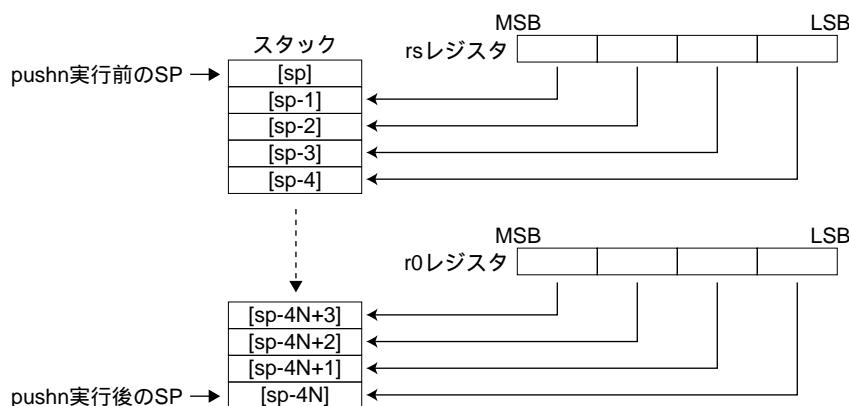

## (3) pushn命令、popn命令実行時

pushn命令によってr0から指定の汎用レジスタまでをスタックに退避させることができます。プッシュしたデータはpopn命令によって各レジスタに戻ります。

スタックとして使用可能な領域サイズは、RAMのサイズと通常のRAMデータが占有する領域サイズによって制限されます。両者が重複しないように注意が必要です。

また、SPはイニシャルリセットにより不定となりますので、初期化ルーチン内の先頭部分でアドレス(スタックの最終アドレス+4、下位2ビットは0)を書き込んでください。アドレスの書き込みはロード命令で行えます。スタック設定前に割り込みや例外が発生すると、PCやPSRが不定の位置にセーブされ、プログラムの正常な動作が保証できません。このため、ソフトウェア制御が不可能なNMIIは、SPが初期化されるまでハードウェアによってマスクされるようになっています。

## 2.1.5 算術演算レジスタ(ALR, AHR)

特殊レジスタには、乗除算、積和演算に使用する算術演算ローレジスタ(以降ALRと記述)と算術演算ハイレジスタ(以降AHRと記述)があります。

それぞれ、32ビットのデータ用レジスタで、ロード命令によって汎用レジスタとのデータ転送が行えます。乗算命令および積和演算命令はALRに演算結果の下位32ビットを、AHRに演算結果の上位32ビットを置きます。

除算命令はALRに商を、AHRに余りを置きます。

イニシャルリセット時、ALRおよびAHRは不定となります。

なお、ALRとAHRはオプションの乗除算回路を内蔵した機種でのみ使用可能です。

### 2.1.6 レジスタの表記とレジスタ番号

以下にS1C33000命令セットのレジスタ表記とレジスタ番号を示します。命令コード中ではレジスタの指定に4ビットのフィールドを使用しており、そこにレジスタ番号が入ります。なお、ニーモニック中では、レジスタ名の前に "%" を付けて指定します。

#### (1)汎用レジスタ

- %rs rsは演算や転送のソースデータを保持している汎用レジスタを示すメタシンボルです。実際には %r0 ~ %r15 と記述します。

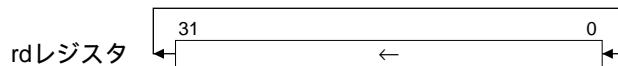

- %rd rdはディスティネーションとなる(演算が行われる、あるいはデータがロードされる)汎用レジスタを示すメタシンボルです。実際には %r0 ~ %r15 と記述します。

- %rb rbはアクセスするメモリのベースアドレスを保持している汎用レジスタを示すメタシンボルです。この場合の汎用レジスタはインデックスレジスタとして機能します。

実際の表記は、レジスタ間接アドレッシングを示す [ ] で囲み、 [%r0] ~ [%r15] のように記述します。レジスタ間接アドレッシングでは、連続したメモリアクセスのためのポストインクリメント機能を使用することができます。その場合は [%r0] + ~ [%r15] + のように "+" を後置します。ポストインクリメントを指定すると、メモリアクセスの後にベースアドレスがアクセスしたデータサイズに従ってインクリメントされます。

- rbはcall命令やjp命令の分岐先アドレスを保持しているレジスタを示すシンボルとしても使用しています。この場合は [ ] が不要で、 %r0 ~ %r15 と記述します。

汎用レジスタのレジスタ番号は、実際のレジスタ名の番号と同じです。コード中のレジスタビットフィールドには指定したレジスタの0~15(0b0000~0b1111)が入ります。

#### (2)特殊レジスタ

- %ss ssは汎用レジスタに転送するソースデータを保持している特殊レジスタを示すメタシンボルです。特殊レジスタをソースとする命令は "ld.w %rd, %ss" のみです。

- %sd sdは汎用レジスタからデータをロードする特殊レジスタを示すメタシンボルです。特殊レジスタをディスティネーションとする命令は "ld.w %sd, %rs" のみです。

特殊レジスタ番号と、実際の記述方法は表2.1.6.1のとおりです。

表2.1.6.1 特殊レジスタ番号と記述方法

| 特殊レジスタ名        | レジスタ番号 | 記述方法 |

|----------------|--------|------|

| プロセッサステータスレジスタ | 0      | %psr |

| スタックポインタ       | 1      | %sp  |

| 算術演算ローレジスタ     | 2      | %alr |

| 算術演算ハイレジスタ     | 3      | %ahr |

レジスタビットフィールドの上位2ビットに0b00、下位2ビットにレジスタ番号0~3(0b00~0b11)が入ります。

## 2.2 データの形式

S1C33000は8ビット、16ビット、32ビットのデータを扱うことができます。

本書ではそれぞれのデータサイズを次のように記述します。

8ビット: バイト( Byte, B )

16ビット: ハーフワード( Half word, H )

32ビット: ワード( Word, W )

16ビットをワード( Word ) 32ビットをロングワード( Long word ) 等と記述している一般の書籍もありますので注意してください。

データサイズは、メモリと汎用レジスタ間、および汎用レジスタ間のデータ転送( ロード命令 )においてのみ選択可能です。

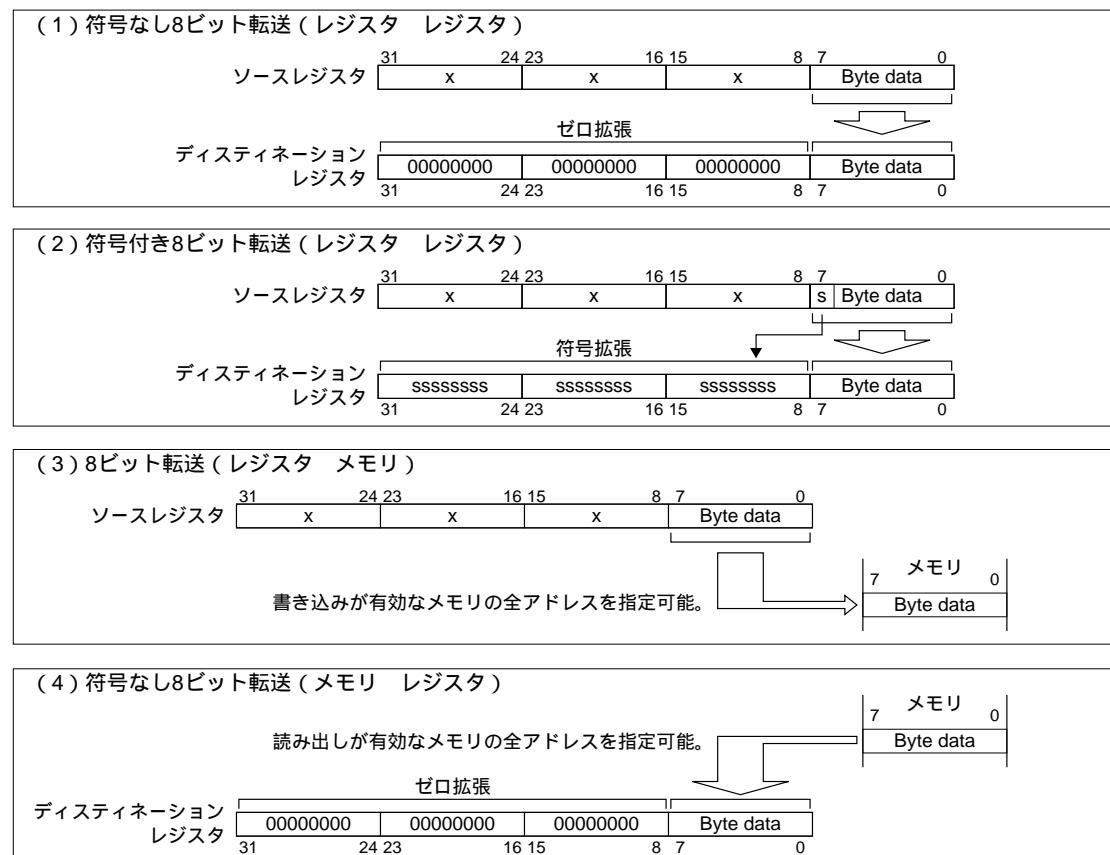

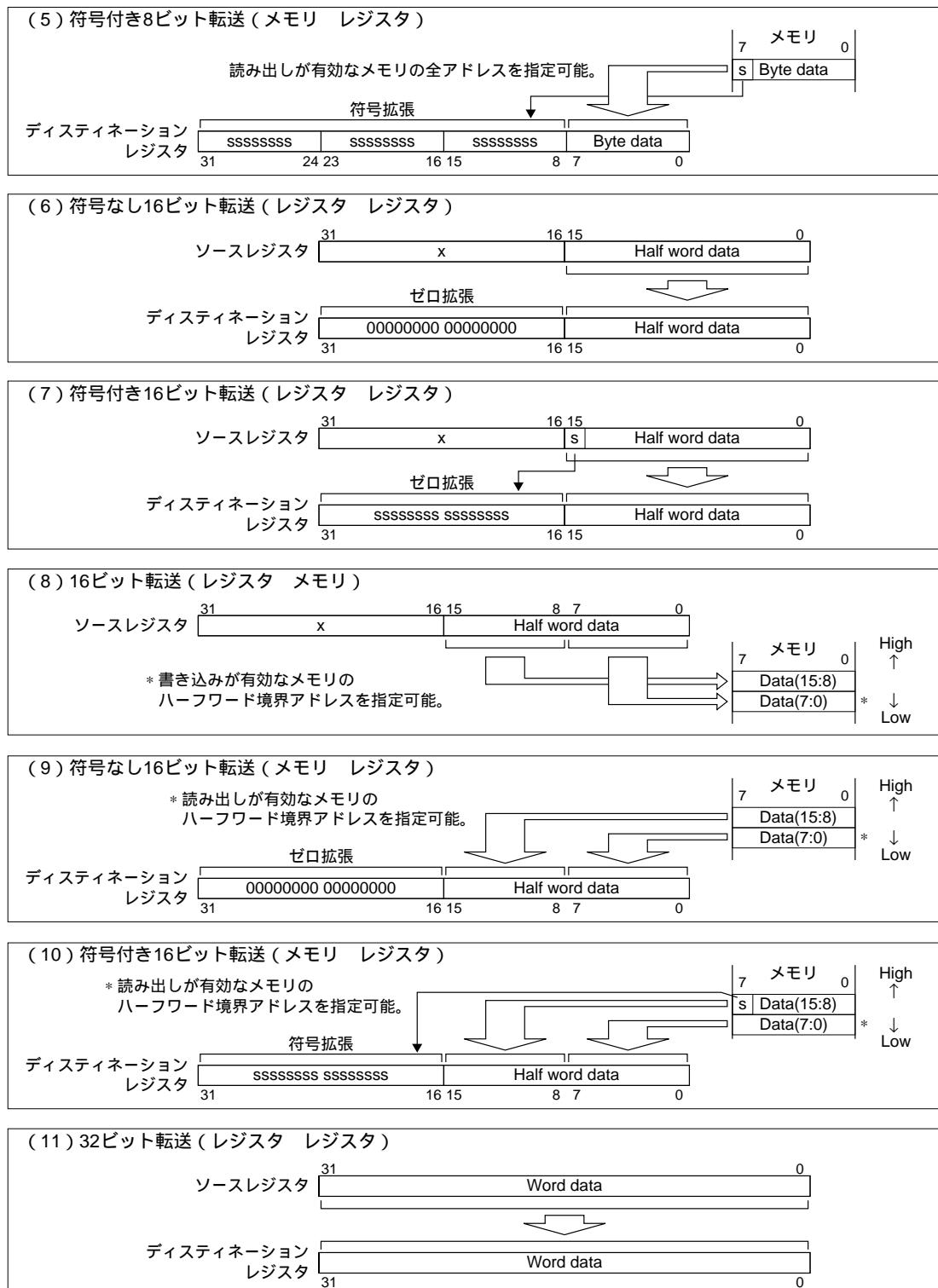

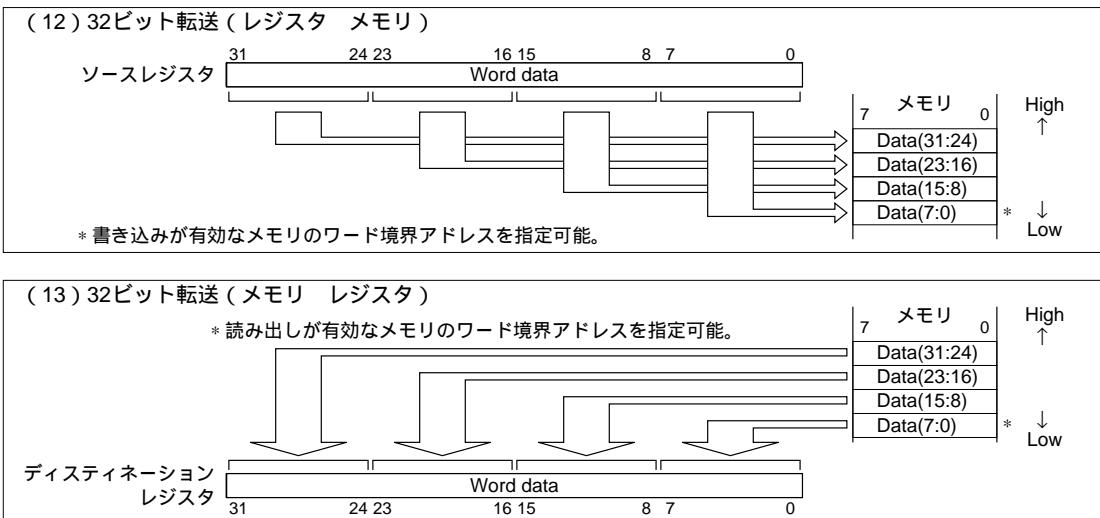

CPUの内部処理はすべて32ビットで行われますので、汎用レジスタをディスティネーションとする16ビットデータ転送および8ビットデータ転送では、レジスタにロードする際に32ビットに符号拡張またはゼロ拡張されます。符号拡張とゼロ拡張は使用するロード命令によって決まります。

汎用レジスタをソースとする16ビットデータ転送または8ビットデータ転送では、ソースレジスタの下位ハーフワードまたは下位1バイトが転送データとなります。

メモリはバイト、ハーフワード、ワード単位にリトルエンディアン形式でアクセスされます。なお、ハーフワード単位およびワード単位のアクセスは、指定するベースアドレスがそれぞれハーフワード境界( アドレスの最下位ビットが0 )、ワード境界( アドレスの下位2ビットが0 )であることが必要で、この条件を満たしていないアクセスに対してはアドレス不整例外が発行されます。

図2.2.1にデータ転送の種類を示します。

図2.2.1 データ転送の種類

## 2.3 アドレス空間

S1C33000は28ビット(256Mバイト)のアドレス空間を持ちます。

すべてのメモリはこの空間内に配置されます。また、メモリマップドI/O方式により、I/Oモジュールの制御レジスタ等もこの空間に配置され、通常のメモリと同様にアクセスできます。

図2.3.1に基本的なメモリマップを示します。

| エリア番号 | アドレス                     | エリアサイズ               |

|-------|--------------------------|----------------------|

| エリア18 | 0xFFFFFFF<br>0xC000000   | 外部メモリ<br>64Mバイト      |

| エリア17 | 0xBFFFFFF<br>0x8000000   | 外部メモリ<br>64Mバイト      |

| エリア16 | 0x7FFFFFF<br>0x6000000   | 外部メモリ<br>32Mバイト      |

| エリア15 | 0x5FFFFFF<br>0x4000000   | 外部メモリ<br>32Mバイト      |

| エリア14 | 0x3FFFFFF<br>0x3000000   | 外部メモリ<br>16Mバイト      |

| エリア13 | 0x2FFFFFF<br>0x2000000   | 外部メモリ<br>16Mバイト      |

| エリア12 | 0x1FFFFFF<br>0x1800000   | 外部メモリ<br>8Mバイト       |

| エリア11 | 0x17FFFFFF<br>0x1000000  | 外部メモリ<br>8Mバイト       |

| エリア10 | 0x0FFFFFF<br>0x0C00000   | 外部メモリ<br>4Mバイト       |

| エリア9  | 0x0BFFFFFF<br>0x0800000  | 外部メモリ<br>4Mバイト       |

| エリア8  | 0x07FFFFFF<br>0x0600000  | 外部メモリ<br>2Mバイト       |

| エリア7  | 0x05FFFFFF<br>0x0400000  | 外部メモリ<br>2Mバイト       |

| エリア6  | 0x03FFFFFF<br>0x0300000  | 外部I/O<br>1Mバイト       |

| エリア5  | 0x02FFFFFF<br>0x0200000  | 外部メモリ<br>1Mバイト       |

| エリア4  | 0x01FFFFFF<br>0x0100000  | 外部メモリ<br>1Mバイト       |

| エリア3  | 0x00FFFFFF<br>0x0080000  | 内蔵ROM<br>512Kバイト     |

| エリア2  | 0x007FFFFFF<br>0x0060000 | ICE用予約エリア<br>128Kバイト |

| エリア1  | 0x005FFFFFF<br>0x0040000 | 内蔵周辺回路<br>128Kバイト    |

| エリア0  | 0x003FFFFFF<br>0x0000000 | 内蔵RAM<br>256Kバイト     |

図2.3.1 メモリマップ

図のようにS1C33000はアドレス空間全体を19個のエリアに分割して管理します。それぞれのエリアには接続するモジュールの種類が割り当てられています。特にエリア0はS1C33 Familyの内蔵RAM、エリア1は内蔵周辺回路、エリア3は内蔵ROMに割り当てられています。また、エリア10に外部ROMを接続し、そのROMからブートすることも可能です。

エリア2は内蔵用エリアですが、ICE用に予約されていますので使用しないでください。( "3.6 デバッグモード"参照 )

外部モジュール用のエリアは、決められたエリア範囲ごとに使用するデバイスの種類や、ポートのデータ幅、ウェイトサイクルなどを指定することができます。その内容はS1C33 Family各機種の構成によって異なります。

S1C33000はアドレスデコーダを内蔵しており、この19エリアに対応する19本のセレクト信号を出力可能です。このため、メモリマップの構成に沿ったシステムは外部にグルーロジックを設ける必要がなく、直接デバイスを接続することができます。

内蔵メモリ容量やI/Oメモリ、アドレスバスのサイズはS1C33 Familyの機種により異なります。したがって、図2.3.1に示したメモリマップがすべての機種に適用される訳ではありません。実際のメモリマップについてはS1C33 Familyの各機種に用意されたテクニカルマニュアルを参照してください。

## 2.4 ブートアドレス

S1C33000はBTA3端子の入力レベルによって、トラップテーブルを置くエリアをエリア3( 内蔵ROM )またはエリア1( 外部ROM )の2種類から選択できるようになっています。トラップテーブルはエリアの先頭から始まり、ブート用のリセットベクタがテーブルの先頭に置かれます。したがって、ブートアドレスは選択されたエリアの先頭アドレスに置かれます。

表2.4.1 ブートアドレスの設定

| 端子入力           | 選択されるエリア      | ブートアドレスのロケーション |

|----------------|---------------|----------------|

| BTA3=1( High ) | エリア3( 内蔵ROM ) | 0x0080000      |

| BTA3=0( Low )  | エリア1( 外部ROM ) | 0x0C00000      |

S1C33 Familyの一般的な機種はROMを内蔵しているため、どちらからでもブートできます。

内蔵ROMを持たない機種では、外部ROMからのブートのみとなります。

実際の機種の対応についてはS1C33 Familyの各機種に用意されたテクニカルマニュアルを参照してください。

## 2.5 命令セット

S1C33000命令セットは61の基本命令(全105命令)を持ちます。命令コードはすべて16ビットの固定長で、CPUはパイプライン処理とロード・ストア型のアーキテクチャにより、主要な命令を1サイクルで実行します。また、C言語による開発でも非常にコンパクトなモジュールが生成可能なコード体系になっています。ここではS1C33000命令セットと機能の概要を説明します。

命令個別の詳細については"4 命令の詳細説明"を参照してください。

### 2.5.1 命令の種類

以下に機能別命令一覧表を示します。

表2.5.1.1 命令一覧表

| 分類           | 二モニック   | 機能                                    |

|--------------|---------|---------------------------------------|

| 論理演算         | and     | 汎用レジスタ間の論理積                           |

|              |         | %rd, %rs 汎用レジスタと即値の論理積(即値は符号拡張)       |

|              | or      | %rd, %rs 汎用レジスタ間の論理和                  |

|              |         | %rd, %sign6 汎用レジスタと即値の論理和(即値は符号拡張)    |

|              | xor     | %rd, %rs 汎用レジスタ間の排他的論理和               |

|              |         | %rd, %sign6 汎用レジスタと即値の排他的論理和(即値は符号拡張) |

|              | not     | %rd, %rs 汎用レジスタの論理反転                  |

|              |         | %rd, %sign6 即値の論理反転(即値は符号拡張)          |

| 算術演算         | add     | %rd, %rs 汎用レジスタ間の加算                   |

|              |         | %rd, imm6 汎用レジスタと即値の加算(即値はゼロ拡張)       |

|              |         | %sp, imm10 SPと即値の加算(即値はゼロ拡張)          |

|              | adc     | %rd, %rs 汎用レジスタ間のキャリー付き加算             |

|              | sub     | %rd, %rs 汎用レジスタ間の減算                   |

|              |         | %rd, imm6 汎用レジスタから即値を減算(即値はゼロ拡張)      |

|              |         | %sp, imm10 SPから即値を減算(即値はゼロ拡張)         |

|              | sbc     | %rd, %rs 汎用レジスタ間のボロー付き減算              |

|              | cmp     | %rd, %rs 汎用レジスタ間の比較                   |

|              |         | %rd, sign6 汎用レジスタと即値の比較(即値は符号拡張)      |

|              | mlt.h   | %rd, %rs 符号付き整数乗算(16ビット×16ビット=32ビット)  |

|              | mltu.h  | %rd, %rs 符号なし整数乗算(16ビット×16ビット=32ビット)  |

|              | mlt.w   | %rd, %rs 符号付き整数乗算(32ビット×32ビット=64ビット)  |

|              | mltu.w  | %rd, %rs 符号なし整数乗算(32ビット×32ビット=64ビット)  |

|              | div0s   | %rs 符号付き整数除算の第1ステップ                   |

|              | div0u   | %rs 符号なし整数除算の第1ステップ                   |

|              | div1    | %rs ステップ除算実行                          |

|              | div2s   | %rs 符号付き整数除算結果のデータ補正1                 |

|              | div3s   | %rs 符号付き整数除算結果のデータ補正2                 |

| シフト<br>ローテート | srl     | %rd, %rs 右方向論理シフト(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 右方向論理シフト(即値によるシフト量指定)       |

|              | sll     | %rd, %rs 左方向論理シフト(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 左方向論理シフト(即値によるシフト量指定)       |

|              | sra     | %rd, %rs 右方向算術シフト(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 右方向算術シフト(即値によるシフト量指定)       |

|              | sla     | %rd, %rs 左方向算術シフト(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 左方向算術シフト(即値によるシフト量指定)       |

|              | rr      | %rd, %rs 右方向ローテート(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 右方向ローテート(即値によるシフト量指定)       |

| 分岐           | rl      | %rd, %rs 左方向ローテート(レジスタによるシフト量指定)      |

|              |         | %rd, imm4 左方向ローテート(即値によるシフト量指定)       |

|              | jrgt    | sign8 PC相対条件ジャンプ 分岐条件: !Z & (N^V)     |

|              | jrgt.d  | (".d"によりディレインド分岐指定可)                  |

|              | jrge    | sign8 PC相対条件ジャンプ 分岐条件: !(N^V)         |

|              | jrge.d  | (".d"によりディレインド分岐指定可)                  |

|              | jrlt    | sign8 PC相対条件ジャンプ 分岐条件: N^V            |

|              | jrlt.d  | (".d"によりディレインド分岐指定可)                  |

| jrlt         | jrle    | sign8 PC相対条件ジャンプ 分岐条件: Z   N^V        |

|              | jrle.d  | (".d"によりディレインド分岐指定可)                  |

|              | jrugt   | sign8 PC相対条件ジャンプ 分岐条件: !Z & !C        |

|              | jrugt.d | (".d"によりディレインド分岐指定可)                  |

| jrugt        | jruge   | sign8 PC相対条件ジャンプ 分岐条件: !C             |

|              | jruge.d | (".d"によりディレインド分岐指定可)                  |

| 分類     | ニーモニック          | 機能                                                |

|--------|-----------------|---------------------------------------------------|

| 分岐     | jrult           | sign8                                             |

|        | jrult.d         | PC相対条件ジャンプ 分岐条件: C<br>( ".d"によりディレイド分岐指定可 )       |

|        | jrule           | sign8                                             |

|        | jrule.d         | PC相対条件ジャンプ 分岐条件: Z   C<br>( ".d"によりディレイド分岐指定可 )   |

|        | jreq            | sign8                                             |

|        | jreq.d          | PC相対条件ジャンプ 分岐条件: Z<br>( ".d"によりディレイド分岐指定可 )       |

|        | jrne            | sign8                                             |

|        | jrne.d          | PC相対条件ジャンプ 分岐条件: !Z<br>( ".d"によりディレイド分岐指定可 )      |

|        | jp              | sign8                                             |

|        | jp.d            | PC相対ジャンプ( ".d"によりディレイド分岐指定可 )                     |

|        | %rb             | 絶対ジャンプ( ".d"によりディレイド分岐指定可 )                       |

|        | call            | sign8                                             |

|        | call.d          | PC相対コール( ".d"によりディレイド分岐指定可 )                      |

|        | %rb             | 絶対コール( ".d"によりディレイド分岐指定可 )                        |

| データ転送  | ret             |                                                   |

|        | ret.d           | サブルーチンからのリターン<br>( ".d"によりディレイド分岐指定可 )            |

|        | reti            | 割り込み処理ルーチン、例外処理ルーチンからのリターン                        |

|        | retd            | デバッグ処理ルーチンからのリターン                                 |

|        | int             | ソフトウェア例外                                          |

|        | brk             | デバッグ例外                                            |

|        | ld.b            | %rd, %rs 汎用レジスタ( バイト ) 汎用レジスタ( データは符号拡張 )         |

|        |                 | %rd, [%rb] メモリ( バイト ) 汎用レジスタ( データは符号拡張 )          |

|        |                 | %rd, [%rb]+ "+"はアドレスのポストインクリメント指定                 |

|        |                 | %rd, [%sp+imm6] スタック( バイト ) 汎用レジスタ( データは符号拡張 )    |

|        |                 | [%rb], %rs 汎用レジスタ( バイト ) メモリ                      |

|        |                 | [%rb]+, %rs "+"はアドレスのポストインクリメント指定                 |

|        |                 | [%sp+imm6], %rs 汎用レジスタ( バイト ) スタック                |

|        | ld.ub           | %rd, %rs 汎用レジスタ( バイト ) 汎用レジスタ( データはゼロ拡張 )         |

|        |                 | %rd, [%rb] メモリ( バイト ) 汎用レジスタ( データはゼロ拡張 )          |

|        |                 | %rd, [%rb]+ "+"はアドレスのポストインクリメント指定                 |

|        |                 | %rd, [%sp+imm6] スタック( バイト ) 汎用レジスタ( データはゼロ拡張 )    |

| データ転送  | ld.h            | %rd, %rs 汎用レジスタ( ハーフワード ) 汎用レジスタ( データは符号拡張 )      |

|        |                 | %rd, [%rb] メモリ( ハーフワード ) 汎用レジスタ( データは符号拡張 )       |

|        |                 | %rd, [%rb]+ "+"はアドレスのポストインクリメント指定                 |

|        |                 | %rd, [%sp+imm6] スタック( ハーフワード ) 汎用レジスタ( データは符号拡張 ) |

|        |                 | [%rb], %rs 汎用レジスタ( ハーフワード ) メモリ                   |

|        |                 | [%rb]+, %rs "+"はアドレスのポストインクリメント指定                 |

|        |                 | [%sp+imm6], %rs 汎用レジスタ( ハーフワード ) スタック             |

|        | ld.uh           | %rd, %rs 汎用レジスタ( ハーフワード ) 汎用レジスタ( データはゼロ拡張 )      |

|        |                 | %rd, [%rb] メモリ( ハーフワード ) 汎用レジスタ( データはゼロ拡張 )       |

|        |                 | %rd, [%rb]+ "+"はアドレスのポストインクリメント指定                 |

|        |                 | %rd, [%sp+imm6] スタック( ハーフワード ) 汎用レジスタ( データはゼロ拡張 ) |

|        | ld.w            | %rd, %rs 汎用レジスタ( ワード ) 汎用レジスタ                     |

|        |                 | %rd, %ss 特殊レジスタ( ワード ) 汎用レジスタ                     |

|        |                 | %sd, %rs 汎用レジスタ( ワード ) 特殊レジスタ                     |

| システム制御 | %rd, sign6      | 即値 汎用レジスタ( 即値は符号拡張 )                              |

|        | %rd, [%rb]      | メモリ( ワード ) 汎用レジスタ                                 |

|        | %rd, [%rb]+     | "+"はアドレスのポストインクリメント指定                             |

|        | %rd, [%sp+imm6] | スタック( ワード ) 汎用レジスタ                                |

|        | [%rb], %rs      | 汎用レジスタ( ワード ) メモリ                                 |

|        | [%rb]+, %rs     | "+"はアドレスのポストインクリメント指定                             |

|        | [%sp+imm6], %rs | 汎用レジスタ( ワード ) スタック                                |

|        | nop             | ノーオペレーション                                         |

|        | halt            | HALTモード設定                                         |

|        | slp             | SLEEPモード設定                                        |

| 即値拡張   | ext             | imm13 直後の命令のオペランド( 即値 )を拡張                        |

|        | btst            | [%rb], imm3 メモリデータ( バイト )の指定ビットをテスト               |

|        | bclr            | [%rb], imm3 メモリデータ( バイト )の指定ビットをクリア               |

|        | bset            | [%rb], imm3 メモリデータ( バイト )の指定ビットをセット               |

|        | bnot            | [%rb], imm3 メモリデータ( バイト )の指定ビットを反転                |

| その他    | scan0           | %rd, %rs "0"ビットのサーチ                               |

|        | scan1           | %rd, %rs "1"ビットのサーチ                               |

|        | swap            | %rd, %rs ワード中のバイト境界でバイト単位のスワップ( 上位↔下位 )           |

|        | mirror          | %rd, %rs ワード中のバイト毎にビット単位でスワップ( 上位↔下位 )            |

|        | mac             | %rs 積和演算 16ビット×16ビット+64ビット 64ビット オプション            |

|        | pushn           | %rsから%r0までの汎用レジスタをスタックにプッシュ                       |

|        | popn            | %r0から%rdまでの汎用レジスタのデータをスタックからポップ                   |

## 2.5.2 アドレッシングモード

S1C33000命令セットは以下に示す6種類のアドレッシングモードを持ちます。CPUは各命令のオペランドによってアドレッシングモードを決定し、データをアクセスします。

### (1) 即値アドレッシング

命令コード中に含まれるimmX( 符号なし即値 ) signX( 符号付き即値 )で示される即値をソースデータとして使用します。論理演算( and, or, xor, not ) 算術演算( add, sub, cmp ) 即値ロード( "ld.w %rd, sign6" ) シフト&ローテー卜( srl, sll, sra, sla, rr, rl ) ピット操作( btst, bclr, bset, bnot ) 即値拡張( ext )の各命令で、このアドレッシングモードを使用することができます。

各命令で指定可能な即値サイズは、シンボルの数字( 例: imm4=符号なし4ビット、sign6=符号付き6ビット )で示されます。

シフト・ローテート命令を除き、ext命令による即値拡張が行えます( 次節参照 )

### (2) レジスタ直接アドレッシング

指定のレジスタの内容をそのままソースデータとして使用します。また、結果をレジスタにロードする命令のディスティネーションとして指定した場合は、結果がそのレジスタにロードされます。以下のシンボルをオペランドとして持つ命令がこのアドレッシングモードで実行されます。

%rs rsは演算や転送のソースデータを保持している汎用レジスタを示すメタシンボルです。実際には%r0 ~ %r15と記述します。

%rd rdはディスティネーションとなる汎用レジスタを示すメタシンボルです。実際には%r0 ~ %r15と記述します。命令によって、ソースデータにもなります。

%ss ssは汎用レジスタに転送するソースデータを保持している特殊レジスタを示すメタシンボルです。

%sd sdは汎用レジスタからデータをロードする特殊レジスタを示すメタシンボルです。

実際の特殊レジスタ名は次のように記述します。

プロセッサステータスレジスタ %psr

スタックポインタ %sp

算術演算ローレジスタ %alr

算術演算ハイレジスタ %ahr

レジスタ名はシンボル等と区別するため、必ず "%" を前置きします。

### (3) レジスタ間接アドレッシング

アドレスを保持している汎用レジスタを指定して、間接的にメモリをアクセスするモードです。[%rb] をオペランドとして持つロード命令にのみ適用されます。実際は汎用レジスタ名を[ ]で囲み、[%r0] ~ [%r15]のように記述します。

CPUは指定レジスタの内容をベースアドレスとして、ロード命令の種類によって決まるデータ形式でデータ転送を行います。

ハーフワード転送、ワード転送の場合、レジスタに設定するベースアドレスはそれぞれハーフワード境界( 最下位ビット=0 ) ワード境界( 下位2ビット=0 )を指している必要があり、それ以外ではアドレス不整例外が発生します。

### (4) ポストインクリメント付きレジスタ間接アドレッシング

レジスタ間接アドレッシングと同様に、汎用レジスタによってアクセスするメモリを間接的に指定します。データ転送が終了すると、指定したレジスタが保持しているベースアドレスを、転送したデータサイズ分インクリメント\*します。これにより、メモリ上の連続したデータの読み出し/書き込みが、最初に1回先頭アドレスを設定するだけで行えます。

\* インクリメントサイズ

バイト転送( ld.b, ld.ub )           rb   rb+1

ハーフワード転送( ld.h, ld.uh )   rb   rb+2

ワード転送( ld.w )                  rb   rb+4

このアドレッシングモードは、レジスタ名を[ ]で囲み "+" を後置きして指定します。実際には[%r0]+ ~ [%r15]+のように記述します。

### (5)ディスプレースメント付きレジスタ間接アドレッシング

レジスタの内容に指定の即値(ディスプレースメント)を加えたアドレスから始まるメモリをアクセスするモードです。ext命令を使用しない場合、このアドレッシングモードは[%sp+imm6]をオペランドとして持つロード命令にのみ適用されます。

例: `ld.b %r0, [%sp+0x10]` ; 現在のSPの内容に0x10を加算したアドレスのバイトデータをR0レジスタにロードします。バイトデータ転送の場合、6ビットの即値がそのままディスプレースメントとして加算されます。

`ld.h %r0, [%sp+0x10]` ; 現在のSPの内容に0x20を加算したアドレスのハーフワードデータをR0レジスタにロードします。ハーフワードデータ転送の場合、ハーフワード境界をアクセスするため、指定した6ビット即値を2倍(最下位ビットは常に0)にした値がディスプレースメントとなります。

`ld.w %r0, [%sp+0x10]` ; 現在のSPの内容に0x40を加算したアドレスのワードデータをR0レジスタにロードします。ワードデータ転送の場合、ワード境界をアクセスするため、指定した6ビット即値を4倍(下位2ビットは常に0)にした値がディスプレースメントとなります。

次節で説明するext命令を使用すると、通常のレジスタ間接アドレッシング(%rb)がext命令で指定した即値をディスプレースメントとする本アドレッシングモードに変わります。

例: `ext imm13`

`ld.b %rd, [%rb]` ; "ld.b %rd, [%rb+imm13]"として機能します。

### (6)符号付きPC相対アドレッシング

符号付き8ビット即値(sign8)をオペランドに持つ分岐命令(jr\*, jp, call)に適用されるアドレッシングモードです。それらの分岐命令を実行すると、現在のPCにsign8の2倍の値(ハーフワード境界)を加算したアドレスに分岐します。

ext命令により即値のサイズを拡張することができます(次節参照)。

### 2.5.3 即値拡張(EXT)命令

16ビット固定長の命令コードでは、その中で指定可能な即値のサイズは限られています。ext命令は主にこの即値のサイズを拡張するために使用します。

ある命令の即値を拡張したい場合、その命令の直前にext命令を記述します。また、ext命令で指定可能な即値サイズは13ビットのため、さらに即値拡張するために2個までext命令を続けることができます。ext命令が有効となるのは直後に記述された即値拡張が可能な命令に対してのみで、その他の命令に対しては無効です。また、3個以上のext命令が連続的に記述された場合は、最初と最後(即値拡張の対象となる命令の直前のext命令)の2個のみが有効で、その間のext命令は無効となります。

以下にext命令の機能を示します。

注: ext命令の拡張例では、1個目のext命令の即値をimm13、2個目のext命令の即値をimm13'と区別して表記しています。

#### (1) 即値データアドレッシング命令の即値サイズの拡張

##### • imm6の拡張

拡張対象の命令: "add %rd, imm6", "sub %rd, imm6"

上記命令単独で指定可能な即値サイズは6ビットです。

これらの命令の直前にext命令を記述することで、即値サイズを19ビット、あるいは32ビットに拡張することができます。

##### ext命令を1個使用

ext imm13

add %rd, imm6 ; "add %rd, imm19"として機能します。

imm6(6ビット)をimm19(19ビット)に拡張します。ext命令のimm13はimm19の上位13ビットとなります。

rdレジスタに対する演算は32ビットとして行われますので、imm19は32ビットにゼロ拡張されます。

##### ext命令を2個使用

ext imm13

ext imm13'

sub %rd, imm6 ; "sub %rd, imm32"として機能します。

imm6(6ビット)をimm32(32ビット)に拡張します。各即値は上位側からimm13、imm13'、imm6の順で32ビットデータを構成します。

##### • sign6の拡張

拡張対象の命令: "and %rd, sign6", "or %rd, sign6", "xor %rd, sign6", "not %rd, sign6", "cmp %rd, sign6", "ld.w %rd, sign6"

上記命令単独で指定可能な即値サイズは符号付き6ビットです。

これらの命令の直前にext命令を記述することで、即値サイズを符号付き19ビット、あるいは符号付き32ビットに拡張することができます。

##### ext命令を1個使用

ext imm13

and %rd, sign6 ; "and %rd, sign19"として機能します。

sign6(符号付き6ビット)をsign19(符号付き19ビット)に拡張します。ext命令のimm13はsign19の上位13ビットとなります。rdレジスタに対する演算/転送は32ビットとして行われますので、sign19はimm13のMSBを符号ビット(0=+、1=-)として32ビットに符号拡張されます。

##### ext命令を2個使用

ext imm13

ext imm13'

cmp %rd, sign6 ; "cmp %rd, sign32"として機能します。

sign6(符号付き6ビット)をsign32(符号付き32ビット)に拡張します。各即値は上位側からimm13、imm13'、sign6の順で32ビットデータを構成します。最初のimm13のMSBが符号ビットとなります。

## (2)レジスタ間接アドレッシングのディスプレースメントを拡張

- [%rb]にディスプレースメントを付加

拡張対象の命令: "Id.\* %rd, [%rb]"( Id.\*: Id.b, Id.ub, Id.h, Id.uh, Id.w ) "Id.\* [%rb], %rs"( Id.\*: Id.b, Id.h, Id.w )

"btst [%rb], imm3", "bclr [%rb], imm3", "bset [%rb], imm3", "bnot [%rb], imm3"

上記命令単独ではrbレジスタの内容をベースアドレスとしたレジスタ間接アドレッシングが行われます。これらの命令の直前にext命令を記述することで、ディスプレースメント付きレジスタ間接アドレッシングに変更することができます。

### ext命令を1個使用

ext imm13

1d.b %rd, [%rb] ; "Id.b %rd, [%rb+imm13]"として機能します。

rbレジスタで指定されるベースアドレスにimm13で指定される13ビットのディスプレースメントを加えたアドレスをアクセスします。アドレス演算の際、imm13は32ビットにゼロ拡張されます。

### ext命令を2個使用

ext imm13

ext imm13'

btst [%rb], imm3 ; "btst [%rb+imm26], imm3"として機能します。

rbレジスタで指定されるベースアドレスにimm26で指定される26ビットのディスプレースメントを加えたアドレスをアクセスします。各即値は上位側からimm13、imm13'の順で26ビットディスプレースメントを構成します。アドレス演算の際、imm26は32ビットにゼロ拡張されます。

この拡張は、ポストインクリメント付きレジスタ間接アドレッシング(%rb)+の命令には適用されません。

- [%sp+imm6]のディスプレースメントを拡張

拡張対象の命令: "Id.\* %rd, [%sp+imm6]"( Id.\*: Id.b, Id.ub, Id.h, Id.uh, Id.w )

"Id.\* [%sp+imm6], %rs"( Id.\*: Id.b, Id.h, Id.w )

上記命令単独ではSPの内容をベースアドレス、コード中の即値imm6を6ビット~8ビットのディスプレースメントとして使用するディスプレースメント付きレジスタ間接アドレッシングが行われます。

バイト転送( Id.b, Id.ub ) 6ビットディスプレースメント = imm6 = {imm6}

ハーフワード転送( Id.h, Id.uh ) 7ビットディスプレースメント = imm6 × 2 = {imm6, 0}

ワード転送( Id.w ) 8ビットディスプレースメント = imm6 × 4 = {imm6, 00}

これらの命令の直前にext命令を記述することで、ディスプレースメントのサイズを19ビットあるいは32ビットに拡張することができます。

### ext命令を1個使用

ext imm13

1d.b %rd, [%sp+imm6] ; "Id.b %rd, [%sp+imm19]"として機能します。

SPが示すスタック先頭アドレスにimm19で指定される19ビットのディスプレースメントを加えたアドレスをアクセスします。ext命令で指定したimm13がimm19の上位13ビットとなり、ロード命令のimm6はimm19の下位6ビットとして使用されます。ただし、ハーフワード転送またはワードデータ転送では、アドレス不整例外が起こらないように、imm6が次のように用いられます。

バイト転送( Id.b, Id.ub ) imm19 = {imm13, imm6}

ハーフワード転送( Id.h, Id.uh ) imm19 = {imm13, imm6(5:1), 0} ( imm6の最下位ビットは無効 )

ワード転送( Id.w ) imm19 = {imm13, imm6(5:2), 00} ( imm6の下位2ビットは無効 )

アドレス演算の際、imm19は32ビットにゼロ拡張されます。

ext命令を2個使用

```

ext      imm13

ext      imm13'

```

ld.w [%sp+imm6],%rs ; "ld.w [%sp+imm32],%rs"として機能します。

SPが示すスタック先頭アドレスにimm32で指定される32ビットのディスプレースメントを加えたアドレスをアクセスします。各即値は上位側からimm13, imm13', imm6の順で32ビットディスプレースメントを構成します。ただし、ハーフワード転送またはワードデータ転送では、アドレス不整例外が起こらないように、imm6が次のように用いられます。

バイト転送( ld.b, ld.ub )   imm32 = {imm13, imm13', imm6}

ハーフワード転送( ld.h, ld.uh ) imm32 = {imm13, imm13', imm6(5:1), 0} (imm6の最下位ビットは無効)

ワード転送( ld.w )           imm32 = {imm13, imm13', imm6(5:2), 00} (imm6の下位2ビットは無効)

アドレス演算の際、imm32は符号なし32ビットデータとして扱われます。ディスプレースメントを加算後の値が有効アドレス範囲(最大28ビット)を越えた場合は、越えた部分が無効となります。

## (3)レジスタ間演算命令を3オペランド命令に拡張

拡張対象の命令: "add %rd, %rs", "sub %rd, %rs", "cmp %rd, %rs", "and %rd, %rs", "or %rd, %rs", "xor %rd, %rs"

上記命令単独ではrdレジスタの内容とrsレジスタの内容を演算し、結果をrdレジスタにロードします。これらの命令の直前にext命令を記述すると、rsレジスタとext命令で指定された即値との演算を行い、結果をrdにロードします。rdレジスタの内容は演算に影響を与えません。

ext命令を1個使用

```

ext      imm13

```

add     %rd,%rs ; "rd ← rs + imm13"として機能します。

演算は32ビットとして行われますので、imm13は32ビットにゼロ拡張されます。

ext命令を2個使用

```

ext      imm13

```

```

ext      imm13'

```

sub     %rd,%rs ; "rd ← rs - imm26"として機能します。

各即値は上位側からimm13, imm13'の順で26ビットデータを構成します。

演算は32ビットとして行われますので、imm26は32ビットにゼロ拡張されます。

## (4)PC相対分岐命令のディスプレースメントの拡張

オペランドにsign& 符号付き8ビット即値)を持つPC相対分岐命令は、現在のPCが示すアドレスにsign8を2倍にした9ビットディスプレースメントを加え、そのアドレスに分岐します。ext命令を使用することで、このディスプレースメントを22ビット(ext命令1個)、32ビット(ext命令2個)に拡張することができます。この詳細については"2.5.12 分岐命令・ディレイド命令"を参照してください。

## 2.5.4 データ転送命令

S1C33000命令セットは、レジスタ～レジスタ間、レジスタ～メモリ間のデータ転送をサポートしています。転送データサイズとデータ拡張形式が命令コードで指定可能です。ニーモニック表記上では次のように分類されます。

|       |                 |

|-------|-----------------|

| ld.b  | 符号付きバイトデータ転送    |

| ld.ub | 符号なしバイトデータ転送    |

| ld.h  | 符号付きハーフワードデータ転送 |

| ld.uh | 符号なしハーフワードデータ転送 |

| ld.w  | ワードデータ転送        |

レジスタへの符号付きバイト/ハーフワード転送では、ソースデータが32ビットに符号拡張されます。符号なしバイト/ハーフワード転送では、ソースデータが32ビットにゼロ拡張されます。

レジスタをソースとする転送では、レジスタ内下位側の指定サイズ分が転送データとなります。

## 2.5.5 論理演算命令

S1C33000命令セットでは、4種類の論理演算命令が使用可能です。

|     |          |

|-----|----------|

| and | 論理積命令    |

| or  | 論理和命令    |

| xor | 排他的論理和命令 |

| not | 否定命令     |

すべての論理演算は、指定の汎用レジスタ( R0～R15 )に対して行われます。ソースは指定の汎用レジスタの32ビットデータか、符号付き即値データ( 6、19、32ビット )の2種類です。

## 2.5.6 算術演算命令

S1C33000命令セットでは算術演算用に、加減算、比較、乗除算命令をサポートしています( 乗除算命令は次節で説明します )。

|     |            |

|-----|------------|

| add | 加算命令       |

| adc | キャリー付き加算命令 |

| sub | 減算命令       |

| sbc | ボロー付き減算命令  |

| cmp | 比較命令       |

上記算術演算は、汎用レジスタ間( R0～R15 ) 汎用レジスタ～即値間で行われます。add命令、sub命令は、さらにSP～即値間の演算にも対応しています。ワードサイズ以外の即値はcmp命令を除き、演算時にゼロ拡張されます。

cmp命令は2つのオペランドを比較する命令で、比較結果によりフラグのみを変更します。基本的には条件ジャンプ命令の条件設定に使用します。ソースにワードサイズ以外の即値を指定した場合は、比較の際に符号拡張されます。

## 2.5.7 乗算・除算命令

S1C33000は乗除算機能もサポートします。ただし、オプションの乗算器を内蔵した機種に限られます。各機種のテクニカルマニュアルで確認してください。

### (1) 乗算命令

S1C33000の命令セットには4つの乗算命令が含まれています。

|        |               |               |

|--------|---------------|---------------|

| mlt.h  | 16ビット × 16ビット | 32ビット( 符号付き ) |

| mltu.h | 16ビット × 16ビット | 32ビット( 符号なし ) |

| mlt.w  | 32ビット × 32ビット | 64ビット( 符号付き ) |

| mltu.w | 32ビット × 32ビット | 64ビット( 符号なし ) |

乗数と被乗数はそれぞれ指定の汎用レジスタ( R0 ~ R15 )のデータを使用します。16ビット乗算の場合は指定レジスタの下位16ビットが使用されます。符号付き乗算命令は乗数、被乗数のMSBを符号ビットとして扱います。

16ビット × 16ビットの演算結果はALRにロードされます。32ビット × 32ビットの演算結果は上位32ビットがAHRに、下位32ビットがALRにロードされます。

S1C33000は16ビット × 16ビットの乗算を1サイクル、32ビット × 32ビットの乗算を5サイクルで実行します。

### (2) 除算命令

S1C33000は符号付きおよび符号なしのステップ除算機能を持っています。

符号付きステップ除算に使用する命令: div0s, div1, div2s, div3s

符号なしステップ除算に使用する命令: div0u, div1

以下に、ステップ除算の実行手順と各命令の機能を示します。

#### 1. ステップ除算の前処理( div0s, div0u )

除算を開始する前に、被除数をALR、除数をrsレジスタ( 汎用レジスタR0 ~ R15 )に用意し、div0sまたはdiv0uを実行します。それぞれの命令は次のような動作を行います。

##### div0s( 符号付きステップ除算の前処理 )

- ・ AHRにALR( 被除数 )の符号を拡張

被除数が正の場合、AHRは0x00000000、負の場合は0xFFFFFFFFに設定されます。

- ・ PSRのDSフラグに被除数の符号ビットをセット

被除数が正の場合、DSフラグは0にリセット、負の場合は1にセットされます。

- ・ PSRのNフラグに除数( rs )の符号ビットをセット

除数が正の場合、Nフラグは0にリセット、負の場合は1にセットされます。

##### div0u( 符号なしステップ除算の前処理 )

- ・ AHRを0x00000000にクリア

- ・ PSRのDSフラグを0にリセット

- ・ PSRのNフラグを0にリセット

#### 2. ステップ除算を実行

div1命令を必要ステップ数、実行します。たとえば、32ビット ÷ 32ビットの場合はdiv1命令を32回実行します。

div1命令は符号付き除算、符号なし除算に共通です。

div1命令の1回の実行で、以下の処理が行われます。

1) {AHR, ALR}の64ビットを左( 上位側 )に1ビットシフト( ALR(0) = 0 )

2) AHRとrsを加算またはAHRからrsを減算し、結果によりAHR、ALRを再設定

加減算はAHRの内容にDSフラグを符号ビットとして付加した33ビットと、rsレジスタの内容にNフラグを符号ビットとして付加した33ビットデータによって行います。

この処理はPSRのDSフラグおよびNフラグによって以下のように異なります。なお、演算結果の33ビット目の値をtmp(32)として説明します。

DS = 0( 被除数: 正 ) N = 0( 除数: 正 )の場合

2-1) tmp = {0, AHR} - {0, rs} を実行

2-2) tmp(32) = 1 の場合: AHR = tmp(31:0)、ALR(0) = 1 として終了

tmp(32) = 0 の場合: AHR、ALR をそのままに終了

DS = 1( 被除数: 負 ) N = 0( 除数: 正 )の場合

2-1) tmp = {1, AHR} + {0, rs} を実行

2-2) tmp(32) = 0 の場合: AHR = tmp(31:0)、ALR(0) = 1 として終了

tmp(32) = 1 の場合: AHR、ALR をそのままに終了

DS = 0( 被除数: 正 ) N = 1( 除数: 負 )の場合

2-1) tmp = {0, AHR} + {1, rs} を実行

2-2) tmp(32) = 1 の場合: AHR = tmp(31:0)、ALR(0) = 1 として終了

tmp(32) = 0 の場合: AHR、ALR をそのままに終了

DS = 1( 被除数: 負 ) N = 1( 除数: 負 )の場合

2-1) tmp = {1, AHR} - {1, rs} を実行

2-2) tmp(32) = 0 の場合: AHR = tmp(31:0)、ALR(0) = 1 として終了

tmp(32) = 1 の場合: AHR、ALR をそのままに終了

符号なし除算の場合は、div1命令を必要数実行することにより結果が次のレジスタから得られます。

AHR 余り ALR 商

符号付き除算の場合は、以下に説明する補正が必要です。

### 3. 符号付き除算の補正

符号付き除算の場合、div1命令を必要ステップ数実行後、div2s命令とdiv3s命令を続けて実行し、演算結果を補正します。

符号なし除算では、div2s命令とdiv3s命令を実行する必要はありません。なお、実行した場合でもnop命令と同様に機能し、演算結果には影響を与えません。

以下に、div2s命令とdiv3s命令の機能を示します。

#### div2s( 符号付きステップ除算結果の補正1 )

被除数が負の数の場合に除算のステップ( div1命令の実行 )で演算結果がゼロになると、全ステップ終了後の演算結果が、除数と同じ余り( AHR ) および実際の値よりも絶対値で1少ない商( ALR )となる可能性があります。div2s命令はこの結果を補正します。

div2s命令の動作は次のとおりです。

DS = 0( 被除数: 正 )の場合

被除数が正の場合は上記の問題は発生しません。したがって、div2s命令は何も実行せずに終了します( nop命令と同じ )。

DS = 1( 被除数: 負 )の場合

1) N = 0( 除数: 正 )の場合: tmp = AHR + rs を実行

N = 1( 除数: 負 )の場合: tmp = AHR - rs を実行

2) 1)の演算結果により、

tmpがゼロの場合: AHR = tmp(31:0)、ALR = ALR + 1 として終了

tmpがゼロ以外の場合: AHR、ALR をそのままに終了

#### div3s( 符号付きステップ除算結果の補正2 )

ステップ除算によりALRから得られる商は常に正の数になります。被除数と除数の符号が異なる場合、結果は負でなければなりません。div3s命令はこの場合の符号補正を行います。

DS = N( 被除数と除数が同符号 )の場合

この場合は上記の問題は発生しません。したがって、div3s命令は何も実行せずに終了します( nop命令と同じ )。

DS = IN(被除数と除数の符号が異なる)の場合

ALR(商)の符号を反転します。

div2s命令およびdiv3s命令実行後、符号付き除算の最終結果が次のレジスタから得られます。

AHR 余り ALR 商

### 除算の実行例

#### (1) 符号付き32ビット ÷ 32ビットの実行

(被除数がR0、除数がR1にロードされている場合)

```

ld.w %alr,%r0 ; ALRに被除数を設定

div0s %r1 ; 初期化ステップ

div1 %r1 ; ステップ除算

:

div1 %r1 ; div1命令を32回実行

div2s %r1 ; 補正命令1

div3s ; 補正命令2

```

AHRに余り、ALRに商がロードされます。

この例の実行にかかる時間は36サイクルです。

符号付き除算の場合、除算結果の余りの符号は被除数と同じになります。

例: (-8) ÷ 5 = -1 余り -3

8 ÷ (-5) = -1 余り 3

#### (2) 符号なし32ビット ÷ 32ビットの実行

(被除数がR0、除数がR1にロードされている場合)

```

ld.w %alr,%r0 ; ALRに被除数を設定

div0u %r1 ; 初期化ステップ

div1 %r1 ; ステップ除算

:

div1 %r1 ; div1命令を32回実行

```

AHRに余り、ALRに商がロードされます。

この例の実行にかかる時間は34サイクルです。

## 2.5.8 積和演算命令

S1C33000は、"64ビット+16ビット×16ビット"の演算を指定回数実行する積和演算機能をサポートしています。この機能により、専用のDSPを外部に設けることなく、デジタル信号処理をオンチップで実現します。ただし、積和演算機能の乗算器を内蔵した機種に限られます。各機種のテクニカルマニュアルで確認してください。

積和演算はmac命令によって実行します。

"mac %rs"命令は" $\{AHR, ALR\} \leftarrow \{AHR, ALR\} + H[<rs+1>] + \times H[<rs+2>] +$ "をrsレジスタで指定される回数分実行します。

rsレジスタには、積和演算開始前に繰り返し回数を設定しておきます。rsレジスタは回数カウンタとして使用され、演算ごとにデクリメントされます。rsレジスタが0になると、mac命令は終了します。したがって、 $2^{32}-1$ 回(4,294,967,295回)までの繰り返しが可能です。rsレジスタに0を設定してmac命令を実行しても、積和演算は行われず、AHR、ALRも変更されません。rsレジスタも0のままデクリメントされません。

$<rs+1>$ と $<rs+2>$ はrsレジスタに続く2つの汎用レジスタです。

例: rsにR0レジスタを指定  $<rs+1>=R1$ レジスタ、 $<rs+2>=R2$ レジスタ

rsにR15レジスタを指定  $<rs+1>=R0$ レジスタ、 $<rs+2>=R1$ レジスタ

$H[<rs+1>] +, H[<rs+2>] +$ は、上記のレジスタの内容をベースアドレスとして指定されるメモリのハーフワードデータを表します。積和演算は、それらを符号付き16ビットデータとして乗算し、結果を{AHR, ALR}レジスタペアに加算します。 "+"は1回の演算後にそれぞれのベースアドレス( $<rs+1>$ と $<rs+2>$ レジスタの内容)がインクリメント(+2)されることを示します。

例: R0 = 16、R1 = 0x100、R2 = 0x120、AHR = ALR = 0に設定し、"mac %r0"を実行

- 1)  $\{AHR, ALR\} = 0 + H[0x100] \times H[0x120]$

- 2)  $\{AHR, ALR\} = \{AHR, ALR\} + H[0x102] \times H[0x122]$

- 3)  $\{AHR, ALR\} = \{AHR, ALR\} + H[0x104] \times H[0x124]$

- ⋮

- 16)  $\{AHR, ALR\} = \{AHR, ALR\} + H[0x11E] \times H[0x13E]$

演算結果は、AHRを上位32ビット、ALRを下位32ビットとする符号付き64ビットデータとして得られます。レジスタの値は、R0 = 0、R1 = 0x120、R2 = 0x140となります。

### 積和演算中のオーバーフロー

積和演算中に演算結果が符号付き64ビットの範囲を越えると、オーバーフローとしてPSRのMOフラグが1にセットされます。この場合でも、rsレジスタに設定した回数を終了するまで演算は継続されます。MOフラグは、ソフトウェアによってリセットするまで1を保持します。mac命令の実行終了後にMOフラグを読み出すことで、演算結果が有効かどうかチェックできます。

### 積和演算中の割り込み

mac命令の実行中は、繰り返しの途中であっても割り込みを受け付けます。割り込み処理ルーチンに分岐する際、スタッカには実行中のmac命令のアドレスがリターンアドレスとしてセーブされます。したがって、割り込み処理ルーチンをreti命令で終了すると、中断していたmac命令の実行を再開します。ただし、その時点のrsレジスタの内容が残りのカウント数となりますので、割り込み処理ルーチン中でrsレジスタの内容が変更されると、当初設定した回数とは異なる結果となります。同様に、 $<rs+1>$ 、 $<rs+2>$ レジスタの値が割り込み処理ルーチン中で変化すると、再開したmac命令は正しく実行されません。

## 2.5.9 シフト&ローテート命令

S1C33000命令セットは、レジスタデータのシフト、ローテート命令をサポートしています。

srl 標理右シフト

sll 標理左シフト

sra 算術右シフト

sla 算術左シフト

rr 右ローテート

rl 左ローテート

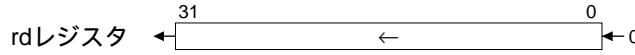

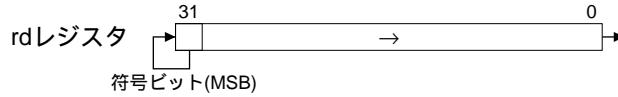

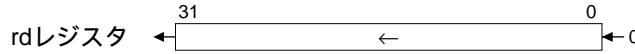

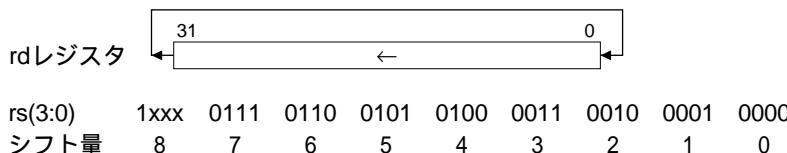

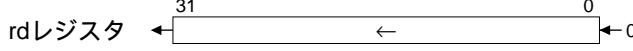

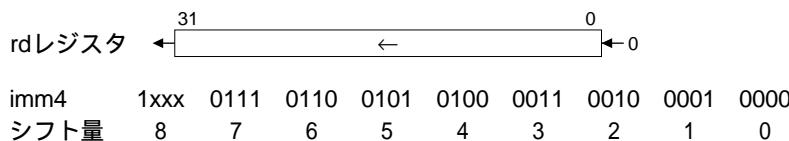

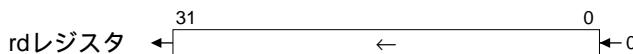

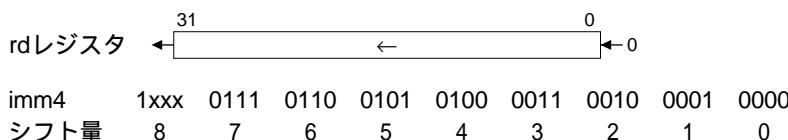

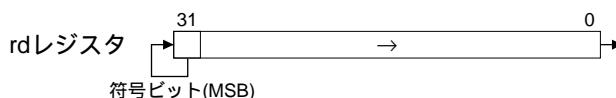

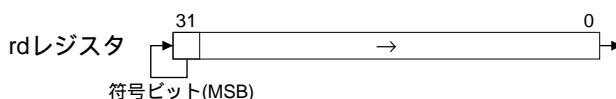

それぞれ、図のように指定の汎用レジスタのビットをシフトします。

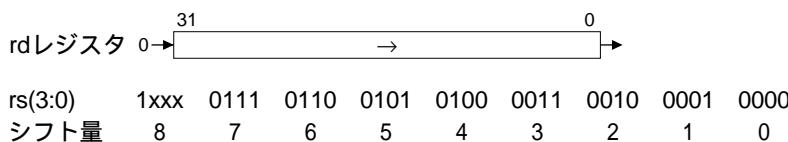

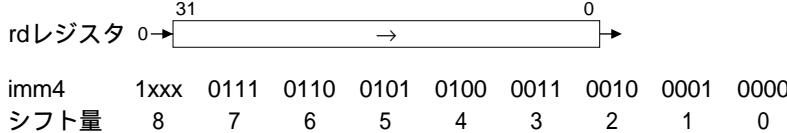

シフト量は、各命令とも任意の汎用レジスタまたは即値により0から8ビットの範囲で指定可能です。

命令 %rd, %rs      rdレジスタのビットをrsレジスタによる指定量シフト/ローテートします。

シフト量はrsレジスタのビット3からビット0の4ビットが有効となります。

命令 %rd, imm4      rdレジスタのビットを符号なし4ビット即値imm4による指定量シフト/ローテートします。

rsレジスタまたはimm4で指定するシフト量は次のとおりです。

rs(3:0)/imm4    シフト量

|      |      |            |

|------|------|------------|

| 1xxx | 8ビット | (x: 1または0) |

| 0111 | 7ビット |            |

| 0110 | 6ビット |            |

| 0101 | 5ビット |            |

| 0100 | 4ビット |            |

| 0011 | 3ビット |            |

| 0010 | 2ビット |            |

| 0001 | 1ビット |            |

| 0000 | 0ビット |            |

## 2.5.10 ビット操作命令

メモリ上のデータをビット単位で操作するため、以下の4種類の命令が用意されています。これらの命令を使用することで、表示メモリやI/Oマップの制御ビットを直接変更することができます。

|                  |                    |

|------------------|--------------------|

| btst [%rb], imm3 | 指定ビットが0ならばZフラグをセット |

| bclr [%rb], imm3 | 指定ビットを0にクリア        |

| bset [%rb], imm3 | 指定ビットを1にセット        |

| bnot [%rb], imm3 | 指定ビットを反転(1↔0)      |

ビット操作は、rb(汎用)レジスタで指定されるメモリアドレスに対して行われます。imm3はそのアドレスにストアされているバイトデータのビット番号(ビット0～ビット7)を指定します。

これらの命令(btstを除く)により変更される内容は指定のビットのみですが、メモリアクセスはバイト単位のため、指定アドレスは書き換えられます。このため、ビットの書き込み動作により機能が有効となるようなI/O制御ビットが割り付けられているアドレスの操作には注意が必要です。

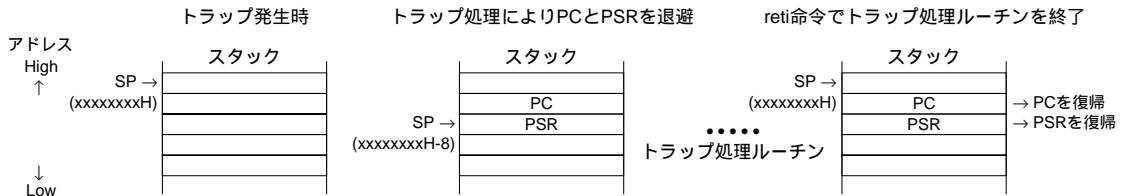

## 2.5.11 プッシュ&ポップ

汎用レジスタの内容をスタックに一時待避させるため、また退避させたデータを元のレジスタに復帰させるため、プッシュ命令とポップ命令が用意されています。

プッシュ命令 `pushn %rs`

この命令は、rsレジスタからR0レジスタまでを連続的にスタックにセーブします。

ポップ命令 `popn %rd`

この命令は、スタックのデータをR0レジスタからrdレジスタまで連続的にロードします。

例:

図2.5.11.1 汎用レジスタの退避と復帰

pushn命令とpopn命令は、同じレジスタ指定のものが対になっている必要があります。

これらの命令は退避/復帰するデータ数に従ってSPを変更します。

プッシュ/ポップ命令のほかに、SPをベースアドレスとしたディスプレースメント付きレジスタ間接アドレッシング( [%sp+imm6] )のロード命令も用意されていますので、SPを基準にしたレジスタ個別のストア/ロードも行えます。ただし、この場合はSPが変更されません。

## 2.5.12 分岐命令・ディレイド命令

### 分岐命令の種類

#### (1) PC相対ジャンプ命令( "jr\* sign8", "jp sign8" )

PC相対ジャンプ命令はリロケータブルなプログラミングに対応した分岐命令で、現在のPCが示すアドレス(分岐命令のアドレス)にオペランドで指定した符号付きのディスプレースメントを加えたアドレスに分岐します。なお、命令長が16ビット固定のため、sign8は16ビット単位のハーフワードアドレスを指定します。したがって、実際にPCに加算されるディスプレースメントはsign8を2倍にした符号付き9ビットとなり(最下位ビットは常に0)偶数アドレスに分岐します。また、ディスプレースメントを加えたPC値が28ビットのアドレス空間を越える場合は、越えた分( PCの上位4ビット )が無効となります。指定可能なディスプレースメントはext命令による拡張も可能で、それぞれ次のようにになります。

#### 分岐命令単独の場合

jp sign8 ; "jp sign9"として機能します。( sign9 = { sign8, 0 } )

分岐命令単独では、符号付き8ビットのディスプレースメント( sign8 )が指定可能です。

sign8は16ビット単位の相対値のため、分岐範囲は[ PC - 256 ~ PC + 254 ]です。

#### ext命令を1個拡張した場合

ext imm13

jp sign8 ; "jp sign22"として機能します。( sign22 = { imm13, sign8, 0 } )

ext命令で指定したimm13をsign22の上位13ビットとして拡張します。

分岐範囲は[ PC - 2,097,152 ~ PC + 2,097,150 ]です。

#### ext命令を2個拡張した場合

ext imm13

ext imm13'

jp sign8 ; "jp sign32"として機能します。

最初のext命令で指定したimm13はビット12~ビット3の10ビットのみが有効(下位3ビットを無視)で、sign32は次のように構成されます。

sign32 = { imm13(12:3), imm13', sign8, 0 }

分岐範囲は[ PC - 2,147,483,648 ~ PC + 2,147,483,646 ]です。

上記の分岐範囲は論理的な値で、実際は使用するメモリ領域の範囲に制限されます。

#### 分岐条件

jp命令は常にプログラムが分岐する無条件ジャンプ命令です。

jrで始まる命令は、それぞれフラグの組み合わせによる分岐条件が設定されており、その条件が満たされている場合にのみ指定アドレスに分岐する条件ジャンプ命令です。条件が合っていない場合は分岐しません。

条件ジャンプ命令は、基本的にcmp命令による2つの値の比較結果を判定するために使用します。このため、各命令の名称には大小関係を表す文字が使用されています。

条件ジャンプ命令の種類と分岐条件を表2.5.12.1に示します。

表2.5.12.1 条件ジャンプ命令と分岐条件

| 命令                                              | フラグ条件                 | "cmp A, B"の結果 | 備考         |

|-------------------------------------------------|-----------------------|---------------|------------|

| jr <sub>gt</sub> ( Grater Than )                | $!Z \& (N \wedge V)$  | A > B         | 符号付きデータ比較用 |

| jr <sub>ge</sub> ( Grater or Equal )            | $(N \wedge V)$        | A B           |            |

| jr <sub>lt</sub> ( Less Than )                  | $N \wedge V$          | A < B         |            |

| jr <sub>le</sub> ( Less or Equal )              | $Z \mid (N \wedge V)$ | A B           |            |

| jr <sub>ugt</sub> ( Unsigned, Grater Than )     | $!Z \& !C$            | A > B         | 符号なしデータ比較用 |

| jr <sub>uge</sub> ( Unsigned, Grater or Equal ) | $!C$                  | A B           |            |

| jr <sub>ult</sub> ( Unsigned, Less Than )       | $C$                   | A < B         |            |

| jr <sub>ule</sub> ( Unsigned, Less or Equal )   | $Z \mid C$            | A B           |            |

| jr <sub>eq</sub> ( Equal )                      | $Z$                   | A = B         | 符号付きおよび    |

| jr <sub>ne</sub> ( Not equal )                  | $!Z$                  | A B           | 符号なしデータ比較用 |

フラグ条件の論理式が真(1)の場合に分岐します。( !: NOT, |: OR, &: AND, ^: XOR )

## (2)絶対ジャンプ命令( "jp %rb" )

絶対ジャンプ命令"jp %rb"は、指定の汎用レジスタ( rb )の内容を絶対アドレスとして無条件に分岐します。rbレジスタの内容がPCにロードされると、その最下位ビットは常に0となり、アドレス空間を外れる上位4ビットも無効となります。

## (3)PC相対コール命令( "call sign8" )

PC相対コール命令"call sign8"はリロケータブルなプログラミングに対応したサブルーチンコール命令で、現在のPCが示すアドレス( 分岐命令のアドレス )にオペランドで指定した符号付きのディスプレースメントを加えたアドレスから始まるサブルーチンへ無条件に分岐します。分岐時には、callの次の命令のアドレス( ディレインド分岐時は2つ目の命令のアドレス )をリターンアドレスとしてスタックにセーブします。サブルーチンの最後にret命令を実行するとこのアドレスがPCにロードされ、サブルーチンからリターンします。

なお、命令長が16ビット固定のため、ディスプレースメントの最下位ビットは常に0として扱われ(sign8が2倍され)偶数アドレスに分岐します。また、ディスプレースメントを加えたPC値が28ビットのアドレス空間を越える場合は、越えた分( PCの上位4ビット )が無効となります。

指定可能なディスプレースメントは、PC相対ジャンプ命令と同様にext命令による拡張も可能です。ディスプレースメントの拡張については前ページの"PC相対ジャンプ命令"を参照してください。

## (4)絶対コール命令( "call %rb" )

絶対コール命令"call %rb"は、指定の汎用レジスタ( rb )の内容を絶対アドレスとして、そのアドレスから始まるサブルーチンを無条件にコールします。

rbレジスタの内容がPCにロードされると、その最下位ビットは常に"0"となり、アドレス空間を外れる上位4ビットも無効となります。

## (5)ソフトウェア例外( "int imm2" )

ソフトウェア例外"int imm2"は、ソフトウェアによって例外を発生させ、指定のトラップ処理ルーチンを実行するための命令です。4種類のトラップ処理ルーチンを作成することができ、imm2によってそれぞれのベクタ番号を指定します。CPUはソフトウェア例外が発生するとPSRと、intの次の命令アドレスをスタックにセーブし、トラップテーブルから指定のベクタを読み出してトラップ処理ルーチンを実行します。したがって、トラップ処理ルーチンからのリターンにはPSRも復帰させるreti命令を使用する必要があります。

ソフトウェア例外の詳細については、"3.3 トラップ( 割り込みと例外 )"を参照してください。

## (6)リターン命令( "ret", "reti" )

ret命令はcall命令に対応するリターン命令で、スタックにセーブされているリターンアドレスをPCにロードしてサブルーチンを終了します。したがって、ret命令実行時のSPの値は、そのサブルーチンの実行開始時の値と同じ( リターンアドレスの位置を示している )でなければなりません。

reti命令はトラップ処理ルーチン用のリターン命令です。トラップ処理では、リターンアドレスとともにPSRもスタックにセーブされますので、reti命令によってPSRの内容を復帰させる必要があります。ret命令と同様にreti命令実行時とトラップ処理ルーチンの実行開始時のSPの値は同じでなければなりません。

## (7)デバッグ例外( "brk", "retd" )

brk命令とretd命令はデバッグ例外処理ルーチンの呼び出しとリターンに使用します。基本的にはICEソフトウェア用の命令のため、アプリケーションプログラムでは使用しないでください。

これらの命令の機能については、"3.6 デバッグモード"を参照してください。

## ディレイド分岐機能

S1C33000は、パイプライン処理により命令の実行とフェッチを同時に行います。分岐命令実行時は続く命令がすでにフェッチされているため、分岐前にその命令を実行することによって分岐命令の実行サイクル数を1サイクル削減することができます。これがディレイド分岐機能で、分岐前に実行される命令(分岐命令の次のアドレスの命令)をディレイド命令と呼びます。

ディレイド分岐機能が使用できる命令は以下のとおりで、ニーモニックでは分岐命令の後ろに".d"を付けて指定します。

### ディレイド分岐命令

jrgt.d jrgt.d jrlt.d jrlt.d jrgt.d jrgt.d jrlt.d jrlt.d jrule.d jrule.d jreq.d jreq.d jrne.d jrne.d call.d call.d jp.d jp.d ret.d

### ディレイド命令

ディレイド命令は以下の条件をすべて満たしていることが必要です。

- ・1サイクル命令

- ・メモリをアクセスしない

- ・ext命令による拡張なし

以下の命令はディレイド命令として使用することができます。

|        |          |      |            |            |

|--------|----------|------|------------|------------|

| ld.w   | %rd, %rs | ld.w | %rd, sign6 |            |

| add    | %rd, %rs | add  | %rd, imm6  |            |

| adc    | %rd, %rs |      | add        | %sp, imm10 |

| sub    | %rd, %rs | sub  | %rd, imm6  |            |

| sbc    | %rd, %rs |      | sub        | %sp, imm10 |

| mlt.h  | %rd, %rs |      |            |            |

| mltu.h | %rd, %rs |      |            |            |

| cmp    | %rd, %rs | cmp  | %rd, sign6 |            |

| and    | %rd, %rs | and  | %rd, sign6 |            |

| or     | %rd, %rs | or   | %rd, sign6 |            |

| xor    | %rd, %rs | xor  | %rd, sign6 |            |

| not    | %rd, %rs | not  | %rd, sign6 |            |

| srl    | %rd, %rs | srl  | %rd, imm4  |            |

| sll    | %rd, %rs | sll  | %rd, imm4  |            |

| sra    | %rd, %rs | sra  | %rd, imm4  |            |

| sla    | %rd, %rs | sla  | %rd, imm4  |            |

| rr     | %rd, %rs | rr   | %rd, imm4  |            |

| rl     | %rd, %rs | rl   | %rd, imm4  |            |

| scan0  | %rd, %rs |      |            |            |

| scan1  | %rd, %rs |      |            |            |

| swap   | %rd, %rs |      |            |            |

| mirror | %rd, %rs |      |            |            |

注: 上記の条件を満たさない命令は動作が不定となるため、ディレイド命令として使用することは禁止します。

ディレイド命令は、ディレイド分岐命令が条件付きか、あるいは無条件かにかかわらず、また分岐するしないにかかわらず必ず実行されます。

ディレイド分岐の使用できない分岐命令( ".d" の付かないもの)では、分岐命令の次のアドレスの命令は、命令フローが分岐する場合は実行されません。

分岐命令が条件分岐命令であって分岐しなかった場合には、次のアドレスの命令が分岐命令に続く命令として実行されます。

call.d命令でスタックにセーブされるリターンアドレスはディレイド命令の次の命令のアドレスとなり、サブルーチンからのリターン時にディレイド命令は実行されません。

ディレイド分岐命令とディレイド命令の間は、割り込みや例外などのトラップはハードウェアによってマスクされ発生しません。

### 2.5.13 システム制御命令

以下の3つの命令はシステムを制御するもので、レジスタやメモリには影響を与えません。

- nop PCをインクリメントするのみで、他の動作を行いません。

- halt CPUをHALTモードにします。

- slp CPUをSLEEPモードにします。

HALTモード、SLEEPモードについては"3.4 パワーダウンモード"を参照してください。

### 2.5.14 スキャン命令

スキャン命令は、指定の汎用レジスタの上位8ビットをMSBからスキャンして、最初に見つかった1または0のビットの位置を返します。

scan0 %rd, %rs

rsレジスタの上位8ビットをスキャンして、最初の0のビットの位置(MSBからのオフセット)をrdレジスタにロードします。rdレジスタのビット31からビット4はすべて0になります。0が見つからない場合、rdレジスタには"0x00000008"がロードされ、Cフラグがセットされます。

例:

| rsの上位8ビット | rdの下位8ビット | PSR |   |   |   |

|-----------|-----------|-----|---|---|---|

|           |           | C   | V | Z | N |

| 0xxx xxxx | 0000 0000 | 0   | 0 | 1 | 0 |

| 10xx xxxx | 0000 0001 | 0   | 0 | 0 | 0 |

| 110x xxxx | 0000 0010 | 0   | 0 | 0 | 0 |

| 1110 xxxx | 0000 0011 | 0   | 0 | 0 | 0 |

| 1111 0xxx | 0000 0100 | 0   | 0 | 0 | 0 |

| 1111 10xx | 0000 0101 | 0   | 0 | 0 | 0 |

| 1111 110x | 0000 0110 | 0   | 0 | 0 | 0 |

| 1111 1110 | 0000 0111 | 0   | 0 | 0 | 0 |

| 1111 1111 | 0000 1000 | 1   | 0 | 0 | 0 |

scan1 %rd, %rs

rsレジスタの上位8ビットをスキャンして、最初の1のビットの位置(MSBからのオフセット)をrdレジスタにロードします。rdレジスタのビット31からビット4はすべて0になります。1が見つからない場合、rdレジスタには"0x00000008"がロードされ、Cフラグがセットされます。

例:

| rsの上位8ビット | rdの下位8ビット | PSR |   |   |   |

|-----------|-----------|-----|---|---|---|

|           |           | C   | V | Z | N |

| 1xxx xxxx | 0000 0000 | 0   | 0 | 1 | 0 |

| 01xx xxxx | 0000 0001 | 0   | 0 | 0 | 0 |

| 001x xxxx | 0000 0010 | 0   | 0 | 0 | 0 |

| 0001 xxxx | 0000 0011 | 0   | 0 | 0 | 0 |

| 0000 1xxx | 0000 0100 | 0   | 0 | 0 | 0 |

| 0000 01xx | 0000 0101 | 0   | 0 | 0 | 0 |

| 0000 001x | 0000 0110 | 0   | 0 | 0 | 0 |

| 0000 0001 | 0000 0111 | 0   | 0 | 0 | 0 |

| 0000 0000 | 0000 1000 | 1   | 0 | 0 | 0 |

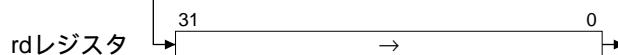

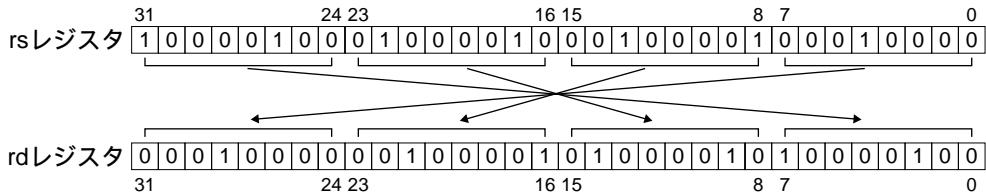

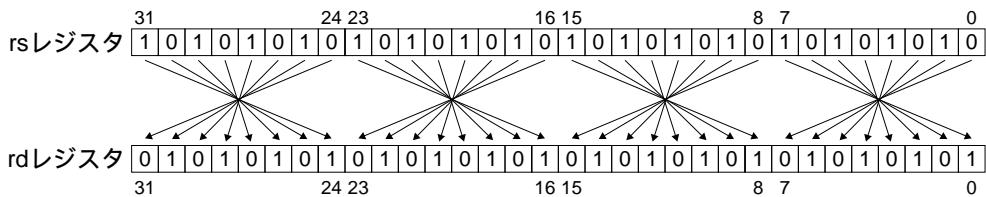

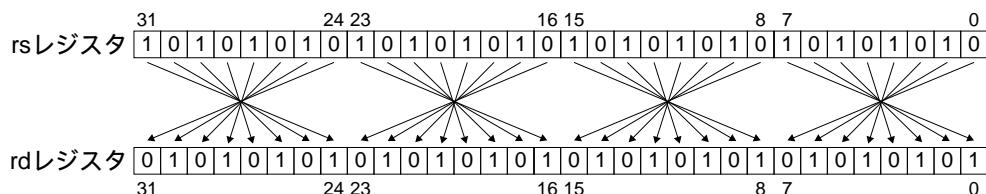

### 2.5.15 スワップとミラー命令

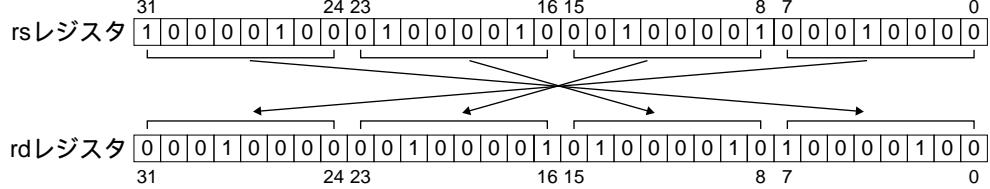

スワップ命令とミラー命令は汎用レジスタの内容を図のように入れ替えます。

スワップ命令: swap %rd, %rs

ミラー命令: mirror %rd, %rs

# 3 CPUの動作と処理状態

ここでは、CPUの処理状態と動作の概要を述べます。詳細についてはS1C33 Family各機種のテクニカルマニュアルを参照してください。

## 3.1 CPUの処理状態

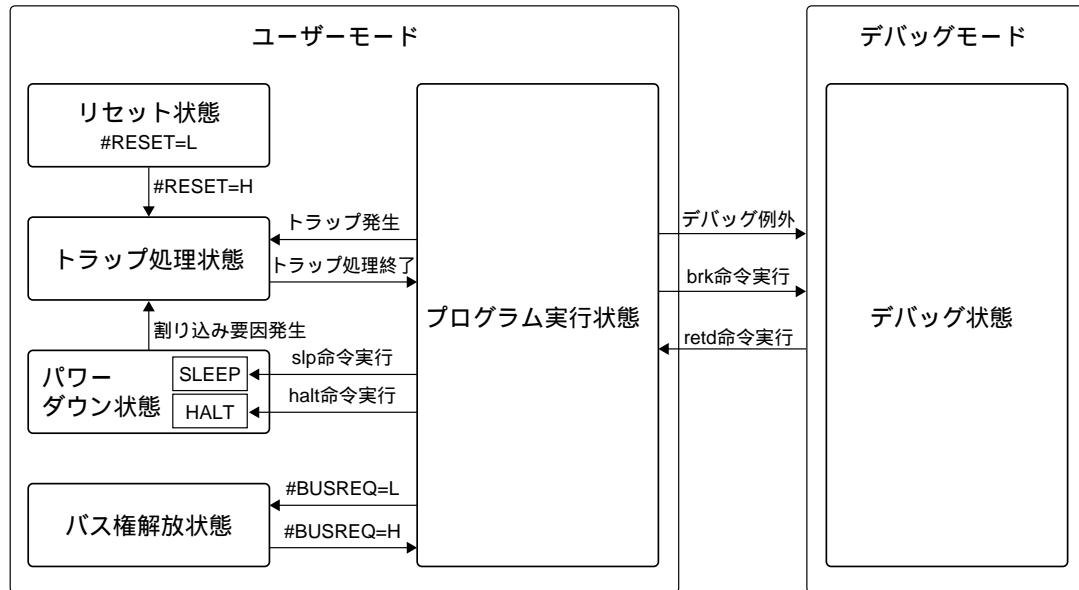

S1C33000の状態遷移図を図3.1.1に示します。

図3.1.1 状態遷移図

### ユーザー モード

ユーザー モードはS1C33000がアプリケーションプログラムを実行するモードです。

イニシャルリセット後はこのモードで動作します。この中で、S1C33000は常に以下に示す5つの処理状態のいずれかに置かれています。

- (1)リセット状態

CPUの内部が初期化され、動作を停止している状態です。

- (2)プログラム実行状態

CPUがユーザープログラムをシケンシャルに実行している状態です。

- (3)トランプ処理状態

CPUが、発生した割り込みや例外の処理ルーチンに分岐するための処理を行っている状態です。

- (4)パワーダウン状態

消費電流を低減するため、CPUが動作を停止している状態です。

- (5)バス解放状態

バス権を外部バスマスターに解放し、外部バスマスターが動作を終了するのを待っている状態です。

### デバッグ モード

S1C33000は開発効率を上げるため、デバッグを支援する機能を搭載しています。この機能を使用するためのモードがデバッグモードでbrk命令やデバッグ例外によってユーザー モードから切り換わるようになっています。通常は、このモードになることはありません。

## 3.2 プログラム実行状態

プログラム実行状態とは、ROMやRAM内のユーザープログラムをシーケンシャルに実行している状態です。実行中のアドレスはPC( プログラムカウンタ )が保持しており、各命令の実行によりインクリメントされます。分岐命令実行時は分岐先アドレスがPCにロードされ、そのアドレスに分岐します。

プログラム実行状態は、トラップの発生、haltまたはslp命令の実行、周辺回路からのバスリクエストによって中断され、CPUはそれぞれの処理状態に移行します。

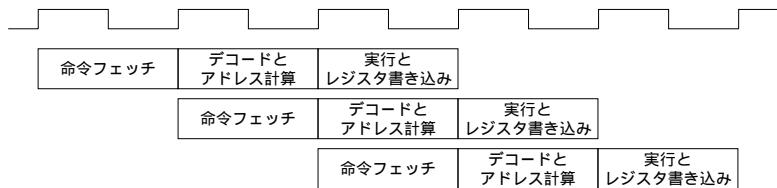

### 3.2.1 プログラムのフェッチと実行

S1C33000は処理速度を上げるために、各命令の実行と実行予定の命令のフェッチを同時に使う3段のパイプライン処理を行っています。また、ハーバードアーキテクチャにより、内部ROM( プログラムメモリ )と内部RAM( データメモリ )を同時にアクセスすることができます。

図3.2.1.1 プログラムのフェッチと実行

### 3.2.2 命令の実行サイクル数

S1C33000は主要な命令を1サイクルで実行することができます。各命令の実行サイクル数についてはAppendixの命令セット一覧表を参照してください。なお、本書に記載の実行サイクル数は内蔵ROMのプログラムと内蔵RAMのデータの場合です。以下に、外部メモリ/デバイスを使用する場合のサイクル数について補足しておきます。実行時間を計算する際には注意してください。なお、以下の計算方法は簡略化されたものです。実際はさらに、命令の組み合わせ、メモリマップの設定内容によって実行サイクルが変わることがあります。

- (1)命令フェッチが内蔵ROM/内蔵RAM領域以外の場合、その領域の[ウェイトサイクル+1]サイクル分、実行サイクルが伸びます。

- (2)内蔵RAM以外の領域に対してld.\*命令でデータの書き込み・読み出しを行う場合、その領域の[ウェイトサイクル+1]サイクル分、実行サイクルが伸びます。

- (3)内蔵RAMから命令をフェッチしながら内蔵RAMに対するデータアクセスを行う場合、1回のデータアクセスについて1サイクル分、実行サイクルが伸びます。

- (4)命令フェッチ、データの書き込み・読み出しでは、転送されるデータサイズと接続されたデバイスサイズの組み合わせによって、バスオペレーションが1回、2回または4回実行されます。これに併せて実行サイクルが伸びます。また、ウェイトサイクルも必要サイクル分だけ長くなります。たとえば、ゼロウェイトで8ビット幅の外部ROMから命令をフェッチする場合、2回のバスオペレーションが実行され、実行サイクルが3サイクル伸びます。

- (5)上記の他にも、BCU( バスコントロールユニット )に設定された外部バス条件の中で以下の要因が実行サイクルに影響します。

- ・外部バス上のデバイスに対して設定されている出力ディセーブルサイクル

- ・DRAMのRASサイクル、プリチャージサイクルおよびリフレッシュサイクル

- ・外部#WAIT端子入力によるウェイトサイクル

- (6)以下の命令は実行中にデータを複数回アクセスします。したがって、その1回のデータアクセスにつき[ウェイトサイクル+1]サイクル分、実行サイクルが伸びます。

|                              |     |                              |    |

|------------------------------|-----|------------------------------|----|

| ・ビット操作命令( btst )             | 1回  | ・ソフトウェア例外( int )             | 3回 |

| ・ビット操作命令( bset, bclr, bnot ) | 2回  | ・トラップ処理ルーチンからのリターン( reti )   | 2回 |

| ・プッシュ/ポップ命令( pushn, popn )   | n回  | ・デバッグ例外( brk )               | 3回 |

| ・積和演算命令( mac )               | 2n回 | ・デバッグ例外処理ルーチンからのリターン( retd ) | 2回 |

- (7)インターロックによる遅延

メモリからデータを汎用レジスタに転送するロード命令のディスティネーションレジスタ( %rd )を直後の命令で演算のソースとして使用する場合は( %rsまたは%rdが直前の%rdと同じ場合 ) インターロックを解消するために実行サイクルが1サイクル伸びます。

BCUおよびウェイト等の外部バス条件については、S1C33 Family各機種のテクニカルマニュアルを参照してください。

### 3.3 トランプ(割り込みと例外)

CPUはプログラム実行中に、トランプ(割り込みや例外)が発生するとトランプ処理状態となります。トランプ処理状態は、各割り込み/例外要因に対応したユーザーの処理ルーチンに分岐するまでのプロセスで、分岐後は再びプログラム実行状態に戻ります。

#### 3.3.1 トランプテーブル

S1C33000のトランプ一覧を表3.3.1.1に示します。

表3.3.1.1 トランプ一覧

| トランプ名称          | 同期/非同期 | 分類   | ベクタアドレス        | 優先順位 | トランプ発生後の割り込みレベル              |

|-----------------|--------|------|----------------|------|------------------------------|

| リセット            | 非同期    | 割り込み | base+0x0       | 最も高い | レベル0                         |

| Reserved        |        |      | base+0x4~0xC   |      | 変更なし                         |

| ゼロ除算            | 同期     | 例外   | base+0x10      |      | 変更なし                         |

| Reserved        |        |      | base+0x14      |      | 変更なし                         |

| アドレス不整例外        | 同期     | 例外   | base+0x18      |      | 変更なし                         |

| デバッグ例外(brk、その他) | 同期     | 例外   | 0x0 or 0x60000 |      | 変更なし                         |

| NMI             | 非同期    | 割り込み | base+0x1C      |      | 変更なし                         |

| Reserved        |        |      | base+0x20~0x2C |      | 変更なし                         |

| ソフトウェア例外0       | 同期     | 例外   | base+0x30      |      | 変更なし                         |

| ⋮               | ⋮      | ⋮    | ⋮              |      | ⋮                            |

| ソフトウェア例外3       | 同期     | 例外   | base+0x3C      |      | 変更なし                         |

| マスク可能な外部割り込み0   | 非同期    | 割り込み | base+0x40      |      | 割り込み要求元の割り込みレベル<br>(レベル0~15) |

| ⋮               | ⋮      | ⋮    | ⋮              |      |                              |

| マスク可能な外部割り込み215 | 非同期    | 割り込み | base+0x39C     | 最も低い |                              |

トランプ名称に挙げた7種類が、S1C33000で扱うトランプ要因です( それぞれの詳細は後述します )。

同期/非同期は、そのトランプがプログラムの実行に同期して発生するか、非同期に発生するかを示しています。同期して発生するものを「例外」、非同期に発生するものを「割り込み」として分類しています。トランプの発生によって行うCPUの処理について、本書では一括してトランプ処理と記述しています。

ベクタアドレスは、各トランプが発生した場合に実行するユーザーのトランプ処理ルーチンへのベクタ(分岐先アドレス)を格納しておくアドレスです。アドレス値を格納しておくため、それぞれワード境界に配置されます。このベクタを格納しておくメモリ領域をトランプテーブルと呼び、ベクタアドレス欄に示した"base"はトランプテーブルのベース(先頭)アドレスを表します。

S1C33000では、トランプテーブルのベースアドレスをTTBRレジスタによって設定することができます。

TTBR0 = D(9:0)/0x48134: トランプテーブルベースアドレス(9:0)…0に固定

TTBR1 = D(F:A)/0x48134: トランプテーブルベースアドレス(15:10)

TTBR2 = D(B:0)/0x48136: トランプテーブルベースアドレス(27:16)

TTBR3 = D(F:C)/0x48136: トランプテーブルベースアドレス(31:28)…0に固定

コールドスタート(3.3.3節参照)によるイニシャルリセット時、TTBRレジスタはBTA3端子の状態で決まるブートアドレスに設定されます。

表3.3.1.2 コールドスタート後のトランプテーブルの位置

| BTA3端子 | トランプテーブルの位置                    |

|--------|--------------------------------|

| High   | エリア3(内蔵ROMの先頭、base=0x0080000)  |

| Low    | エリア10(外部ROMの先頭、base=0x0C00000) |

したがって、トランプテーブルの位置を変更する場合でも、コールドスタート用のリセットベクタのみは上記のアドレスに書き込んでおくことが必要です。ホットスタートによるイニシャルリセット時は、TTBRレジスタは初期化されません。

TTBR0とTTBR3は読み出し専用で"0"に固定されます。このため、トラップテーブルの先頭アドレスは常に1KB境界アドレスから始まります。

なお、TTBRレジスタは誤って書き換えることのないように、通常は書き込み禁止状態に置かれ、この書き込み保護機能を解除するためにTBRPレジスタ(D[7:0] 0x4812D)が用意されています。TBRPレジスタに0x59を書き込むとTTBRレジスタへの書き込みが許可され、TTBRレジスタの最上位バイト(0x48137)への書き込みにより書き込み禁止状態に戻ります。したがって、TTBRレジスタへの書き込みは下位ハーフワードから先に行なうことが必要です。ただし、下位と上位ハーフワードの書き込みの間にNMI等が発生すると誤動作しますので、ワード書き込みを推奨します。

機種によってアクセス可能なメモリ空間は異なります。各ベクタ用にワードサイズの領域が確保されていますが、実際にベクタとして使用されるのは下位側の有効なビット長のみです。また、ベクタはプログラムメモリのアドレスのため、最下位ビットは常に0として扱われます。

トラップテーブルのサイズは機種により設定されるマスク可能な割り込みの数で決まります。

優先順位は、複数のトラップが同時に発生した場合に、どれが先にCPUに受け付けられるかを示しています。複数の例外が同時に発生することはありません。リセット要因は他のすべての処理に優先して受け付けられます。マスク可能な割り込みについては、後述する割り込みレベルによっても優先度が管理されます。したがって、表3.3.1.1に示したマスク可能な割り込みの優先順位は、すべてが同じ割り込みレベルを持つ場合のものです。

トラップ発生後の割り込みレベルについては、"3.3.8 マスク可能な外部割り込み"で説明します。

### 3.3.2 トラップ処理

リセットおよびデバッグ例外を除いたトラップが発生すると、CPUは以下に示すトラップ処理を実行します。なお、以下の処理はリセット処理には適用されません。リセットについては次節で、デバッグ例外については3.6節で説明します。

- (1) 実行中の命令を終了またはキャンセルします。

- (2) PC、PSRの順にそれぞれの内容をスタックに待避させます。

- (3) PSRのIE(割り込みイネーブル)ビットをクリアし、それ以降のマスク可能な割り込みを禁止します。発生したトラップがマスク可能な割り込みの場合は、PSRのIL(割り込みレベル)を発生した割り込みのレベルに変更します。

- (4) トラップテーブルから、発生したトラップのベクタを読み出しPCにセットします。これにより、ユーザーのトラップ処理ルーチンに分岐します。

ここまでが、CPUのトラップ処理です。

ユーザーのトラップ処理ルーチンの最後にreti命令を実行すると、スタックに待避していたPSRとPCの内容がそれぞれのレジスタに戻り、トラップの発生によって中断していた処理を再開します。

トラップ処理ルーチンからのリターンには、PCのみを復帰するret命令は使用できません。

なお、リセットを除くトラップは以下の場合にマスクされ、その要因が解除されるまでCPUには受け付けられません。

- (1) ext命令実行時

ext命令があると、続くターゲット命令の実行を終了するまでトラップはマスクされます。

ただし、アドレス不整例外の場合を除きます。

- (2) ディレイド分岐命令実行時

ディレイド分岐命令(.d)があると、続くディレイド命令の実行を開始するまでトラップはマスクされます。

- (3) SP未設定時のNMI

CPUをリセット後、SPにデータを書き込む(スタックが設定される)まではプログラムの暴走を防ぐためNMIがマスクされます。

例外は発生が予測できるため、マスクの対象とはなりません。また、リセット後はマスク可能な割り込みもPSRのIEビットによりマスクされているため同様にマスクの対象とはなりません。

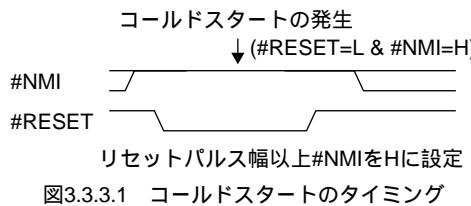

### 3.3.3 リセット

CPUの#RESET端子にLowパルスを入力することで、CPUがリセットされます。これによりPSRの全ビットが0にクリアされます。他のレジスタは不定となります。

CPUは#RESETパルスの立ち上りエッジで動作を開始し、リセット処理を行います。リセット処理ではトランプテーブルの先頭からリセットベクタが読み出され、PCにセットされます。これにより、ユーザーの初期化ルーチンに分岐してプログラムの実行を開始します。

リセット処理は他のすべての処理に優先します。

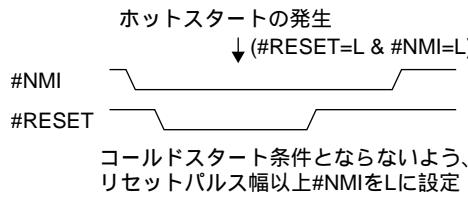

S1C33000は、コールドスタートとホットスタートの2種類のリセット方式をサポートしています。この条件設定には#NMI端子を#RESET端子とともに使用します。

#### コールドスタート(#RESET=L, #NMI=H)

#RESET端子をLow、#NMI端子をHighにしてリセットすると、S1C33 FamilyのMPUIはコールドスタートします。コールドスタートの場合、CPUの他にチップ上の周辺回路もすべて初期化されますので、主にパワーオンリセットに用います。

図3.3.1 コールドスタートのタイミング

#### ホットスタート(#RESET=L, #NMI=L)

#RESET端子および#NMI端子をLowにしてリセットすると、S1C33 FamilyのMPUIはホットスタートします。ホットスタートの場合、CPUは初期化されますが、周辺回路の中で外部バスコントロールユニットや出入力ポートなどは初期化されません。外部メモリや外部入出力の状態を保持したままリセットをかけたい場合に用います。

図3.3.2 ホットスタートのタイミング

リセットタイミングや周辺回路の初期化については、S1C33 Family各機種のテクニカルマニュアルを参照してください。

### 3.3.4 ゼロ除算例外

除算命令実行時に除数がゼロであると、このゼロ除算例外が発生します。

この例外が発生するのは、除算の前処理を行うdiv0sまたはdiv0uの2命令です。除数が0の場合、CPUはこの命令の実行を終了後、トラップ処理に移行します。トラップ処理でスタックにセーブするPC値は、次の命令(通常div1命令)のアドレスとなります。

ただし、パイプライン処理の関係で、例外の発生が1命令後ろにずれる場合があります。

### 3.3.5 アドレス不整例外

メモリやI/O領域をアクセスするロード命令は、命令により転送するデータサイズが決まっています。そのアドレスはデータサイズごとの境界でなければなりません。

| 命令         | 転送データサイズ       | アドレス     |                   |

|------------|----------------|----------|-------------------|

| ld.b/ld.ub | バイト (8ビット)     | バイト境界    | (使用領域の全アドレスが対象)   |

| ld.h/ld.uh | ハーフワード (16ビット) | ハーフワード境界 | (アドレスの最下位ビットが常に0) |

| ld.w       | ワード (32ビット)    | ワード境界    | (アドレスの下位2ビットが常に0) |

ロード命令の指定アドレスがこの条件を満たしていない場合、CPUはアドレス不整例外としてトラップ処理に移行します。この場合、ロード命令は実行されません。トラップ処理でスタックにセーブするPC値は、例外を発生したロード命令のアドレスとなります。

通常のext命令実行時は、次の命令との間でトラップがマスクされるようになっています。ただし、アドレス不整例外のみはマスクされません。したがって、ext命令に続くロード命令( ext命令によるディスプレイスメント付きレジスタ間接アドレッシング)でアドレス不整例外が発生した場合は、上記のように、そのロード命令を実行前にトラップ処理に移行します。この場合、処理ルーチンから単純にreti命令で戻ると、そのロード命令のみが単独で( ext命令のないレジスタ間接アドレッシングとして)実行されてしまいますので注意が必要です。

積和演算(mac)命令もメモリ上のハーフワードデータを扱うため、アドレス不整例外が発生する可能性があります。この場合も、スタックにセーブされるリターンアドレスはmac命令のアドレスとなり、トラップ処理ルーチンからのリターン後は残りの回数の積和演算を継続します。

ベースアドレスとしてSPを使用するロード命令においては、アドレスがデータサイズに応じてアライメントされるため、アドレス不整例外は発生しません。

プログラムの分岐を伴う命令("call %rb"、"jp %rb")では、PCの最下位ビットが常に0に固定されるため、この例外は発生しません。トラップ処理のベクタについても同様です。

### 3.3.6 NMI(マスク不可能な割り込み)

CPUの#NMI入力がアクティブ(Low)になるとNMIが発生します。NMIが発生すると、CPUは実行中の命令を終了後、トラップ処理に移行します。トラップ処理でスタックにセーブするPC値は、次の命令のアドレスとなります。

NMIはマスクが不可能な割り込みですが、CPUリセット後(コールドスタート、ホットスタートとも)のSPが不定な期間に発生するとプログラムが暴走するため、"ld.w %sp, %rs"命令によってSPを設定するまではハードウェアによってCPUの#NMI入力がマスクされるようになっています。

### 3.3.7 ソフトウェア例外

ソフトウェア例外は"int imm2"命令の実行によって発生します。このトラップ処理でスタックにセーブするPC値は、次の命令のアドレスとなります。int命令中のオペランドimm2は、4種類のソフトウェア例外のベクタアドレスを指定します。CPUはbase+48(ソフトウェア例外0ベクタアドレス)に4×imm2を加算したアドレスからベクタを読み出して処理ルーチンに分岐します。

### 3.3.8 マスク可能な外部割り込み

S1C33000は128種類までのマスク可能な外部割り込み(NMIを除く)を受け付けることができます。

マスク可能な割り込みは、PSRのIE(割り込みイネーブル)ビットがセットされている場合にのみCPUが受け付けます。また、PSRのIL(割り込みレベル)フィールドにより受け付け可能な割り込みのレベルが制限されます。ILフィールドの割り込みレベル(0~15)はCPUが受け付け可能な割り込みレベルを示し、その値より大きいレベルの割り込みのみを受け付けます。

IEビットとILフィールドはソフトウェアで設定可能です。また、トラップ発生時にはPSRをスタックにセーブ後、IEビットは(割り込み禁止)にクリアされ、処理ルーチン内でIEビットをセットするか、PSRを復帰させるreti命令で処理ルーチンを終了させるまで、マスク可能な割り込みを禁止します。

ILフィールドも発生した割り込みのレベルに設定されます。割り込み処理ルーチン内でIEビットをセットすることによって、現在処理中の割り込みよりも高いレベルの割り込みを受け付ける多重割り込みが容易に実現できます。

CPUがリセットされた場合はPSRが0に初期化されるため、マスク可能な割り込みは禁止され、割り込みレベルは(1~15の割り込みレベルを許可)に設定されます。

S1C33 Familyの全機種がチップ上に割り込みコントローラを内蔵しているため、CPUへの割り込み要求は割り込みコントローラが行います。

オンチップ割り込みコントローラによるマスク可能な割り込みの発生手順とCPUのトラップ処理の内容は次のとおりです。

- (1) オンチップ割り込みコントローラは、#INTREQ端子をLowにして割り込みを要求します。同時に、INTLEV(3:0)に割り込みレベルを、INTVEC(7:0)にベクタ番号を出力します。

- (2) CPUはその割り込み要求を受け付けるとPCとPSRをスタックにセーブ後、PSRのIEビットをクリアし、ILフィールドをINTLEVの状態に従った割り込みレベルに設定します。

- (3) CPUはトラップテーブル内のINTVECで指定されるベクタアドレスからベクタを読み出してPCにセットし、割り込み処理ルーチンに分岐します。

オンチップ割り込みコントローラの制御方法については、各機種のテクニカルマニュアルを参照してください。

### 3.4 パワーダウンモード

システムがキー入力待ちなど、特にプログラムを実行する必要のない待機状態の場合、CPUの動作を停止して消費電流を低減することができます。このために、S1C33000は2種類のパワーダウンモード、HALTモードとSLEEPモードをサポートしています。

なお、パワーダウンモード中もCPU内部のレジスタの状態は保持されます。

#### 3.4.1 HALTモード

CPUがhalt命令を実行すると、その時点でプログラムの実行を中断しHALTモードに移行します。

HALTモードではCPUの動作が停止します。チップ上の周回路に対してはクロックが供給されますので、周回路は動作を継続します。

HALTモードはイニシャルリセットまたはNMIを含む割り込みによって解除され、解除後はそれぞれのトラップ処理を経てプログラム実行状態に移行します。割り込みによって解除した場合、トラップ処理によってhaltの次の命令のアドレスがスタックにセーブされます。したがって、発生した割り込みの処理ルーチンをreti命令で終了すると、haltの次の命令の位置にリターンします。

#### 3.4.2 SLEEPモード

CPUがslp命令を実行すると、その時点でプログラムの実行を中断しSLEEPモードに移行します。

SLEEPモードではCPUおよびチップ上の周回路も動作を停止します。このため、HALTモードよりも大幅に消費電流を低減することができます。

SLEEPモードはイニシャルリセットまたはNMIを含む割り込みによって解除され、解除後はそれぞれのトラップ処理を経てプログラム実行状態に移行します。割り込みによって解除した場合、トラップ処理によってslpの次の命令のアドレスがスタックにセーブされます。したがって、発生した割り込みの処理ルーチンをreti命令で終了すると、slpの次の命令の位置にリターンします。

なお、SLEEPモードではチップ上の発振回路およびその出力クロックを使用する周回路が基本的に停止するため、SLEEPモードの解除はキー入力割り込み等により行われます。

また、SLEEP解除により発振回路が動作を開始するため、CPUの動作開始には発振安定待ち時間が必要となります。

HALTモード、SLEEPモード時の周回路の状態、解除方法等の詳細については、各機種のテクニカルマニュアルを参照してください。

### 3.5 バス権解放状態

周辺回路/デバイスが接続される外部バスは、通常CPUの管理下に置かれています。S1C33000は、DMA(ダイレクト・メモリ・アクセス)を必要とする周辺回路/デバイスやマルチCPUシステムに対応するため、バス権を外部に解放することが可能となっています。

この制御には、CPUの#BUSREQ端子と#BUSACK端子を使用します。

バス権解放のシーケンスは次のとおりです。

- (1)バス権を要求する外部デバイスは、CPUの#BUSREQ端子をLowレベルにします。

- (2)CPUは常に#BUSREQ端子の状態を監視しており、端子がLowレベルになると実行中のバスサイクルを終了し、その1サイクル後にアドレスバス( A27 ~ A0 ) データバス( D15 ~ D0 ) バス制御信号( #RD, #WRL, #WRH )をハイインピーダンスにします。

さらに1サイクル後、CPUは#BUSACK端子をLowレベルにしてバス権を解放したことを、外部デバイスに知らせます。

- (3)(2)によってバス権を要求した外部デバイスがバスマスターとなり、自らのバスサイクルを実行します。

この間、外部バスマスターはCPUの#BUSREQ端子をLowに固定しておく必要があります。

- (4)外部バスマスターは必要なバスサイクルを終了後、バスをハイインピーダンスにしてから#BUSREQ端子をHighレベルに戻します。

- (5)CPUは#BUSREQ端子のHighレベルを確認すると、その1サイクル後に#BUSACK端子をHighレベルにし、中断していた処理を再開します。

機種によっては、バス権解放中にCPUがバス権を取り戻すことが必要な場合もあります(たとえば、DRAMを直結する機種のリフレッシュ要求等)。その場合は、CPUの要求を出力ポートなどの周辺回路を利用して出力するため、外部バスマスターとなるデバイスはその信号への対応も必要となります。詳細については、S1C33 Family各機種のテクニカルマニュアルを参照してください。

### 3.6 デバッグモード

S1C33000はデバッグモードという特殊な動作モードを持っています。

このデバッグモードはターゲットプログラム開発時のデバッグを支援するために設定されており、量産用のアプリケーションで使用することはできません。ここでは、CPUの機能としての概要を説明します。

#### 3.6.1 デバッグモードの機能

S1C33000は以下のデバッグ機能を内蔵しています。

- ・シングルステップ

ユーザー ターゲットプログラムの各命令の実行前にデバッグ例外を発生させることができます。

- ・命令ブレーク

設定したアドレスを実行する直前にデバッグ例外を発生させることができます。アドレスは3ヶ所まで設定することができます。

- ・データブレーク

設定したアドレスに対して読み出し/書き込みが行われると、読み出しありまたは書き込みの実行より1~数命令後にデバッグ例外を発生させることができます。アドレスは1ヶ所のみ設定することができます。

- ・ソフトウェアブレーク

brk命令の実行によりデバッグ例外を発生することができます。デバッグ例外発生時の退避アドレスはbrk命令の次のアドレスとなります。

これらのデバッグ例外が発生すると、CPUはユーザー モードとは異なる例外処理を行いデバッグモードに移行します。

デバッグモードでは、ユーザーが作成したデバッグ処理ルーチン、あるいはセイコーエプソンが提供するデバッグ処理ルーチンを実行することにより、ユーザー ターゲットプログラムを任意のアドレスでブレークさせたり、シングルステップなどの実行を行うことができます。

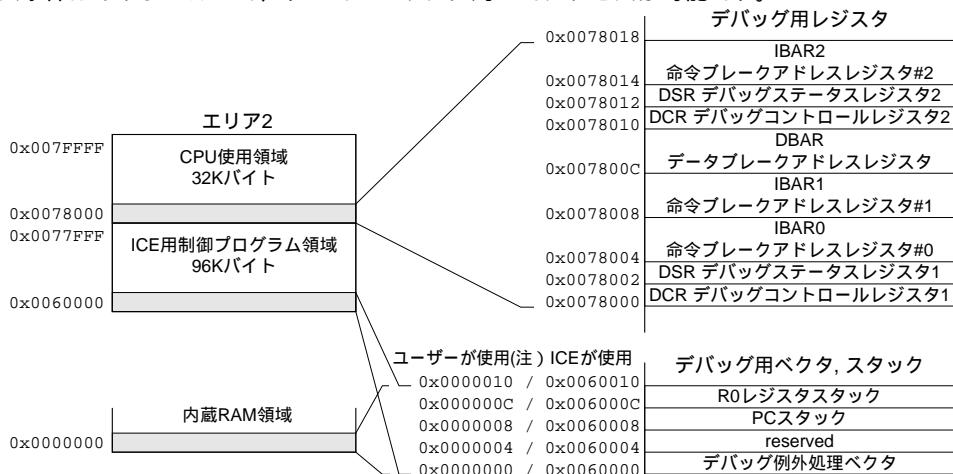

#### 3.6.2 エリア2の構成

S1C33000はアドレス空間の中のエリア( 0x0060000 ~ 0x007FFFF の128Kバイト )をICE( In-Circuit Emulator )用の予約エリアとしています。このエリア2にデバッグ機能を制御するレジスタが配置されています。

0x0060010 ~ 0x007FFFFがICE用制御プログラム領域として予約され、0x0078000以降の領域はデバッグ機能を制御するレジスタとCPUの専用領域として予約されています。

エリア2のデバッグ機能を制御するレジスタへのデータ書き込みは、ユーザー モードでは行えません。デバッグ例外発生後のデバッグモードで行う必要があります。なお、デバッグモードでは特に各エリアへのアクセス条件はありませんので、すべてのエリアに対してアクセスが可能です。

図3.6.2.1 エリア2の構成

注: ユーザーがデバッグモードを使用した場合には、0x0000000のアドレスからデバッグ例外処理ベクタを読み出し、また0x00000008、0x0000000CにそれぞれPCとR0レジスタを退避します。

MON33( デバッグモニタ )は、このユーザー用の設定で作成されています。

### 3.6.3 ユーザーモードからデバッグモードへの移行

デバッグ例外が発生すると(例:brk命令の実行) CPUはデバッグ例外処理に移行します。

このデバッグ例外処理は通常の例外処理とは異なり、通常のトラップテーブルを使用せずにエリア0の0x00000000またはICEが使用する0x0060000に書き込まれたベクタを読み出してデバッグモードに移行します。同時に動作モードをユーザーモードからデバッグモードに切り替えます。この際に退避されるレジスタもR0レジスタとPCで、通常の例外処理とは異なります。また、この退避領域も通常の例外処理とは異なり、R0レジスタには0x000000CまたはICEが使用する0x006000C、PCには0x0000008またはICEが使用する0x0060008の固定された領域が使用されます。

デバッグモードからユーザーモードへの移行は、retd命令を実行することにより行われます。retd命令は、R0レジスタとPCの内容をデバッグモード移行前の状態に復帰させ、ユーザーモードに戻します。

### 3.6.4 デバッグ用レジスタ

エリア2にはデバッグ機能を制御するデバッグ用レジスタが設定されており、デバッグモード時に書き込みが可能となります。以下に各レジスタの内容と機能を示します。

DCR(デバッグコントロールレジスタ) 0x0078000/バイト, 0x0078010/バイト

|           | 7 | 6     | 5     | 4   | 3        | 2   | 1   | 0             |      |

|-----------|---|-------|-------|-----|----------|-----|-----|---------------|------|

| 0x0078000 | – | MWRBE | MRDBE | DBE | IBE(1:0) | SE  | DM  | R/W可 (DMはRのみ) |      |

| 0x0078010 | – | –     | (注)   | (注) | (注)      | (注) | (注) | IBE(2)        | R/W可 |

注: 0x0078010のビット5~1は以下の値以外に設定しないでください。デバッグ機能が正常に動作しなくなります。

ビット5, 4: "0"固定、ビット3~1: "1"固定

DCRはデバッグ機能を許可/禁止するためのレジスタです。イニシャルリセット時、DCRの全ビットは0に初期化されます。

0x0078000

| 名称       | ビット番号 | ビットの状態  |          | 機能                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |       | 1       | 0        |                                                                                                                                                                                                                                                                                                                                                         |

| DM       | 0     | デバッグモード | ユーザー モード | Debug Mode: CPUがデバッグモードにあることを示します。デバッグ例外が発生すると、DMがセット(1)され、CPUがデバッグモードになります。デバッグ処理ルーチンでretd命令を実行するとリセット(0)され、CPUはユーザー モードに戻ります。DMは読み出し専用で、ソフトウェアによる書き込みはできません。                                                                                                                                                                                          |