CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

# S1C63158

テクニカルマニュアル

S1C63158 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

## 本版で改訂または追加された箇所

| 章        | 節/項 | 頁   | 項目                   | 内容          |

|----------|-----|-----|----------------------|-------------|

| 7        | 7.1 | 110 | 絶対最大定格               | 定格値を変更      |

| Appendix | A.1 | 123 | (5) CR発振周波数調整ボリューム   | 文章削除        |

|          | A.2 | 126 | 表A.2.1 I/Oコネクタのピン配列表 | 表変更         |

|          | A.3 | 128 | (3) 機能上の相違           | 文章削除<br>図変更 |

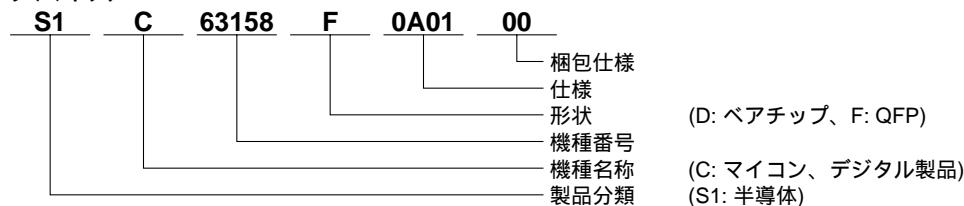

## 製品型番変更のご案内

2001年4月1日より、弊社半導体製品の製品型番が以下のとおり変更となっておりますので、ご発注につきましては変更後の製品型番にてお願い申し上げます。

なお、製品型番の詳細仕様につきましては、弊社営業担当にお問い合わせください。

## 製品型番体系

### デバイス

### 開発ツール

\*1: ツールの種類は、新旧型番対応表を参照してください。(マニュアル類には一桁で記載されているものもあります。)

\*2: マニュアル類には、実際のバージョンは記載されておりません。

## 新旧型番対応表

### S1C63ファミリ

| 旧型番       | 新型番      |

|-----------|----------|

| E0C63158  | S1C63158 |

| E0C63256  | S1C63256 |

| E0C63358  | S1C63358 |

| E0C63P366 | S1C6P366 |

| E0C63404  | S1C63404 |

| E0C63406  | S1C63406 |

| E0C63408  | S1C63408 |

| E0C63F408 | S1C6F408 |

| E0C63454  | S1C63454 |

| E0C63455  | S1C63455 |

| E0C63458  | S1C63458 |

| E0C63466  | S1C63466 |

| E0C63P466 | S1C6P466 |

| 旧型番       | 新型番      |

|-----------|----------|

| E0C63467  | S1C63467 |

| E0C63557  | S1C63557 |

| E0C63558  | S1C63558 |

| E0C63567  | S1C63567 |

| E0C63F567 | S1C6F567 |

| E0C63658  | S1C63658 |

| E0C63666  | S1C63666 |

| E0C63F666 | S1C6F666 |

| E0C63A08  | S1C63A08 |

| E0C63B07  | S1C63B07 |

| E0C63B08  | S1C63B08 |

| E0C63B58  | S1C63B58 |

### S1C63ファミリのペリフェラル製品

| 旧型番     | 新型番      |

|---------|----------|

| E0C5250 | S1C05250 |

| E0C5251 | S1C05251 |

## 開発ツール新旧型番対応表

### S1C63ファミリ関係の開発ツール

| 旧型番      | 新型番          |

|----------|--------------|

| ADP63366 | S5U1C63366X  |

| ADP63466 | S5U1C63466X  |

| ASM63    | S5U1C63000A  |

| GAM63001 | S5U1C63000G  |

| ICE63    | S5U1C63000H1 |

| PRC63001 | S5U1C63001P  |

| PRC63002 | S5U1C63002P  |

| PRC63004 | S5U1C63004P  |

| PRC63005 | S5U1C63005P  |

| PRC63006 | S5U1C63006P  |

| PRC63007 | S5U1C63007P  |

| URS63366 | S5U1C63366Y  |

### S1C63/88ファミリ関係の開発ツール

| 旧型番      | 新型番          |

|----------|--------------|

| ADS00002 | S5U1C88000X1 |

| GWH00002 | S5U1C88000W2 |

| URM00002 | S5U1C88000W1 |

## - 目 次 -

|       |                            |    |

|-------|----------------------------|----|

| 1     | 概要                         | 1  |

| 1.1   | 特長                         | 1  |

| 1.2   | ブロック図                      | 2  |

| 1.3   | 端子配置図                      | 3  |

| 1.4   | 端子説明                       | 4  |

| 1.5   | マスクオプション                   | 4  |

| 2     | 電源系 および イニシャルリセット          | 7  |

| 2.1   | 電源系                        | 7  |

| 2.1.1 | 発振回路および内部回路用電圧<VD1>        | 7  |

| 2.1.2 | 発振系定電圧回路用電源電圧              | 8  |

| 2.1.3 | A/D変換回路用電源電圧               | 8  |

| 2.2   | イニシャルリセット                  | 9  |

| 2.2.1 | リセット端子( RESET )            | 9  |

| 2.2.2 | 入力ポート( K00 ~ K03 )の同時LOW入力 | 10 |

| 2.2.3 | イニシャルリセット時の内部レジスタ          | 10 |

| 2.2.4 | イニシャルリセット時の端子設定            | 11 |

| 2.3   | テスト端子( TEST )              | 11 |

| 3     | CPU, ROM, RAM              | 12 |

| 3.1   | CPU                        | 12 |

| 3.2   | コードROM                     | 12 |

| 3.3   | RAM                        | 12 |

| 4     | 周辺回路と動作                    | 14 |

| 4.1   | メモリマップ                     | 14 |

| 4.2   | 電源と動作モードの設定                | 21 |

| 4.2.1 | 電源電圧の制御                    | 21 |

| 4.2.2 | 発振系定電圧回路の動作モードと内部動作電圧      | 21 |

| 4.2.3 | A/D変換器電源の動作モード             | 22 |

| 4.2.4 | 電源と動作モードのI/Oメモリ            | 23 |

| 4.2.5 | プログラミング上の注意事項              | 24 |

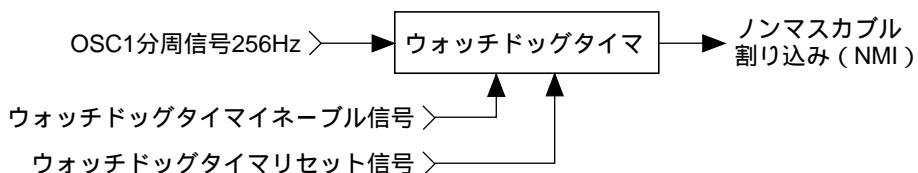

| 4.3   | ウォッチドッグタイマ                 | 25 |

| 4.3.1 | ウォッチドッグタイマの構成              | 25 |

| 4.3.2 | 割り込み機能                     | 25 |

| 4.3.3 | ウォッチドッグタイマのI/Oメモリ          | 26 |

| 4.3.4 | プログラミング上の注意事項              | 26 |

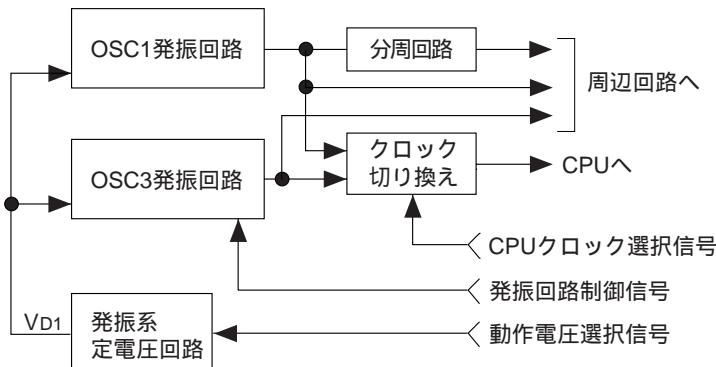

| 4.4   | 発振回路                       | 27 |

| 4.4.1 | 発振回路の構成                    | 27 |

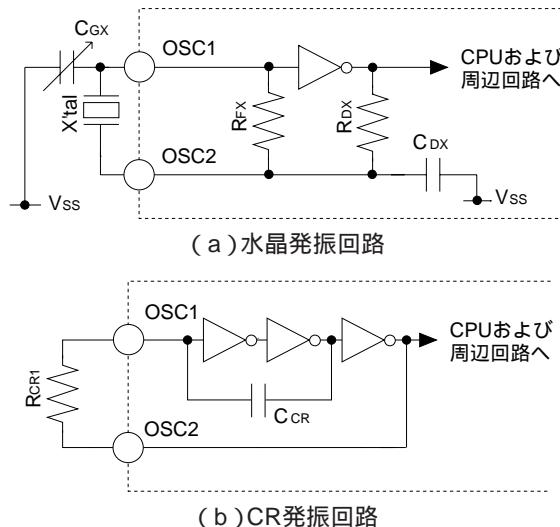

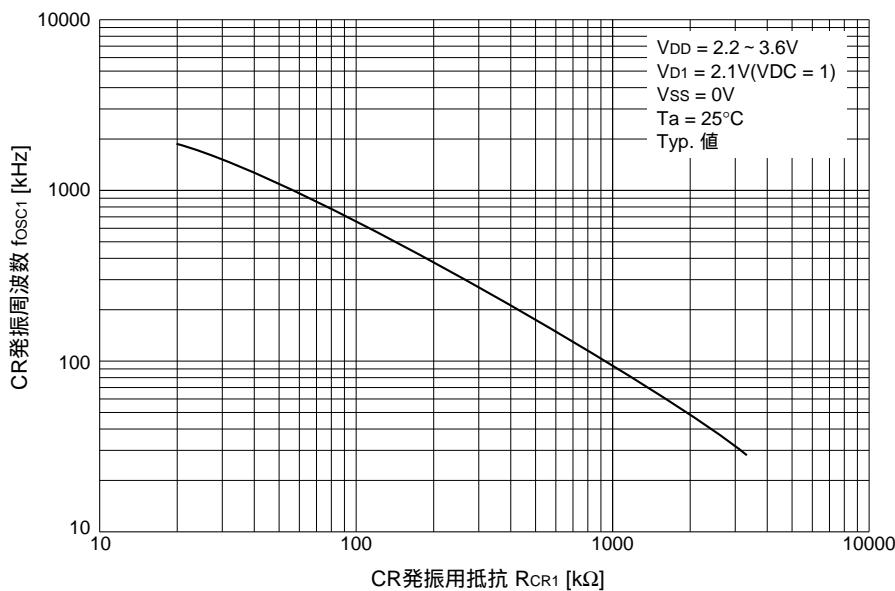

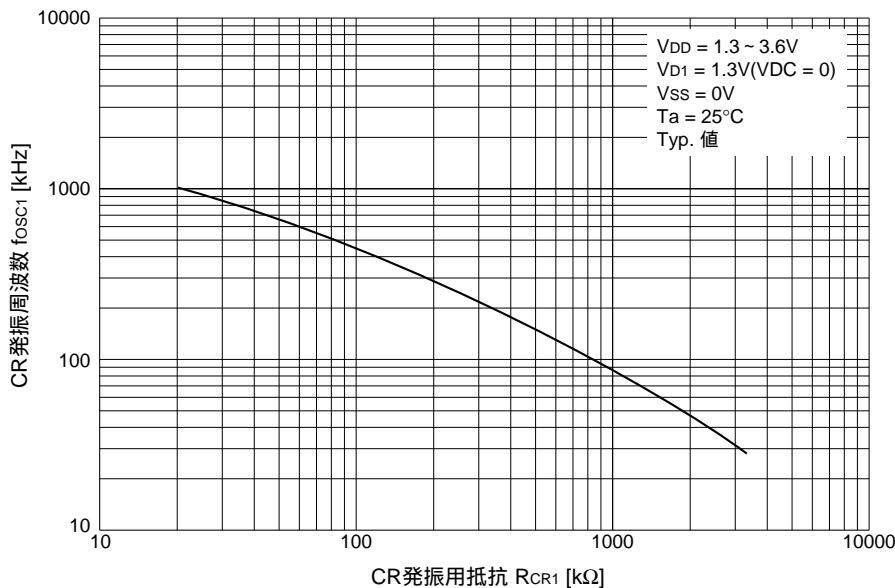

| 4.4.2 | OSC1発振回路                   | 28 |

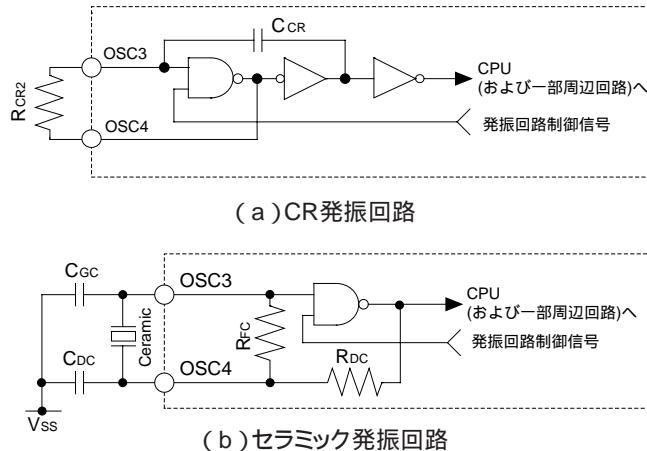

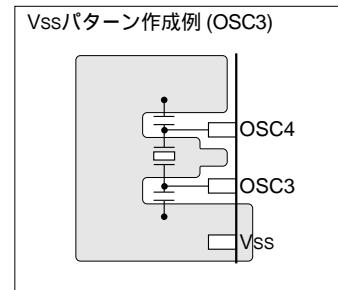

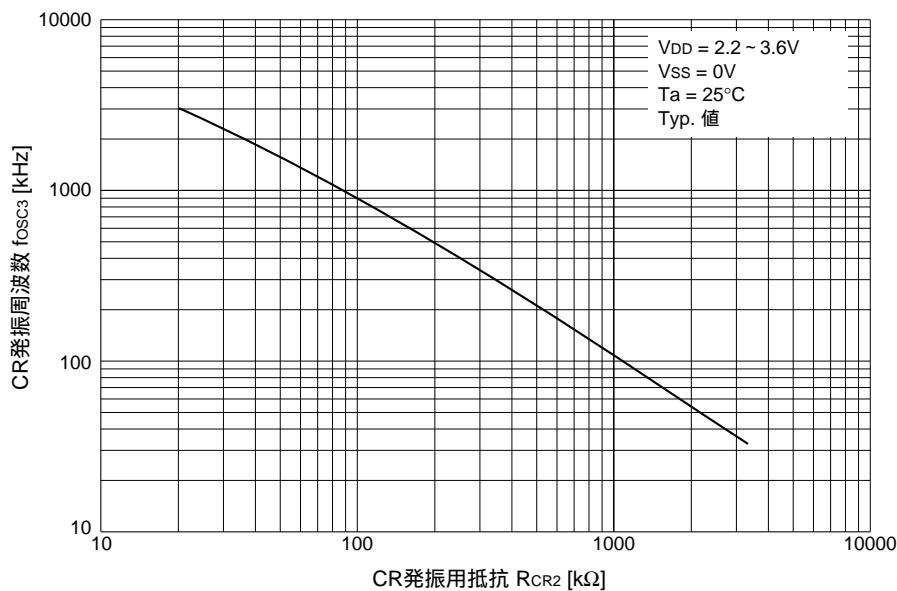

| 4.4.3 | OSC3発振回路                   | 29 |

| 4.4.4 | 動作電圧切り換え                   | 30 |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| 4.4.5 クロック周波数とインストラクション実行時間 .....                                           | 31 |

| 4.4.6 発振回路のI/Oメモリ .....                                                     | 31 |

| 4.4.7 プログラミング上の注意事項 .....                                                   | 32 |

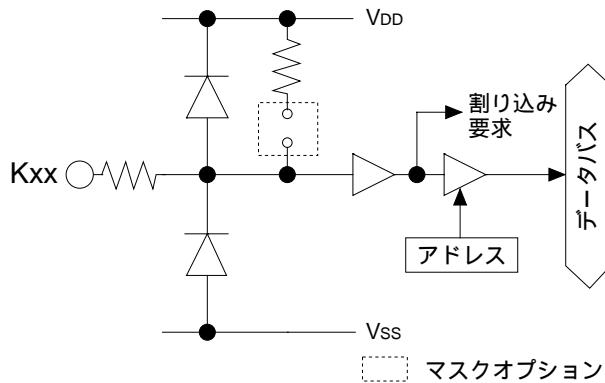

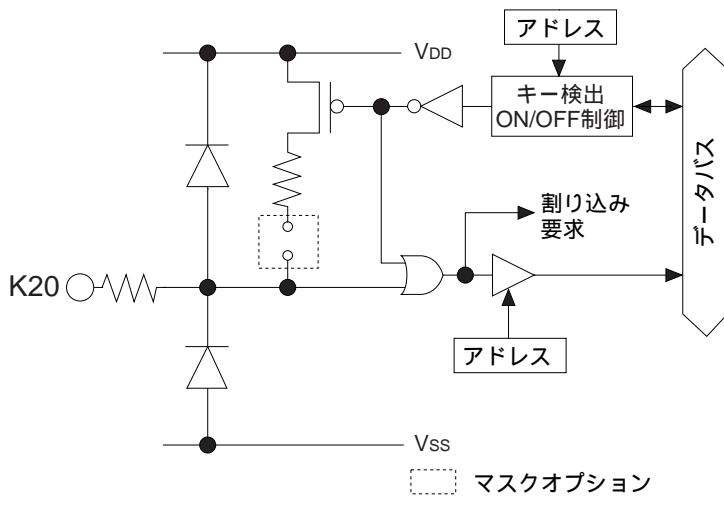

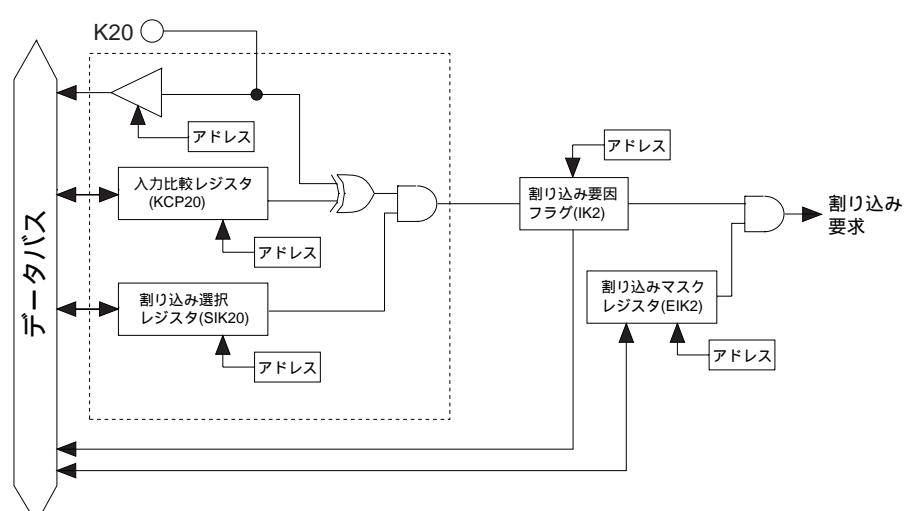

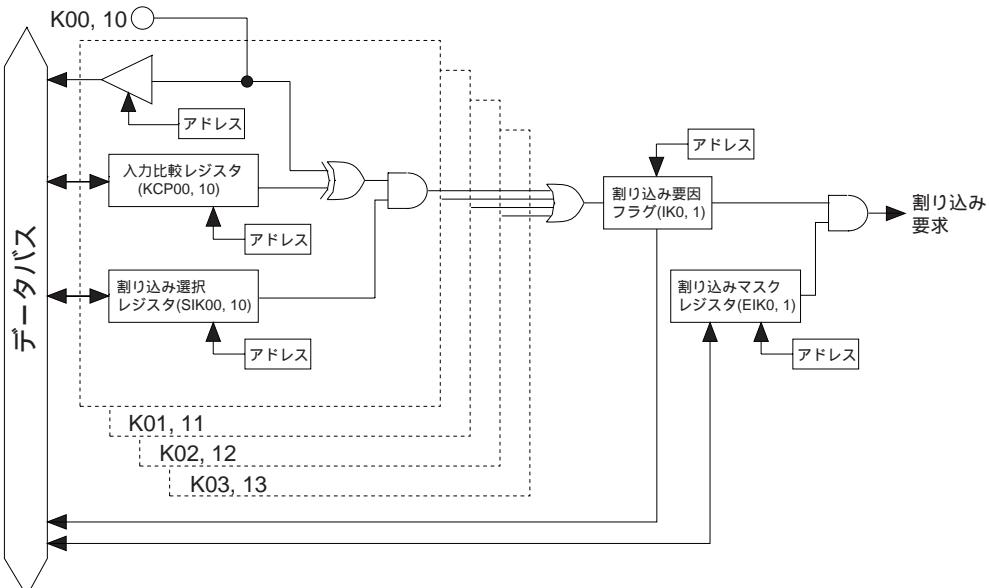

| 4.5 入力ポート( K00 ~ K03, K10 ~ K13, K20 ) .....                                | 33 |

| 4.5.1 入力ポートの構成 .....                                                        | 33 |

| 4.5.2 割り込み機能 .....                                                          | 34 |

| 4.5.3 マスクオプション .....                                                        | 35 |

| 4.5.4 入力ポートのI/Oメモリ .....                                                    | 36 |

| 4.5.5 プログラミング上の注意事項 .....                                                   | 39 |

| 4.6 出力ポート( R00 ~ R03, R10 ~ R13, R20 ~ R23 ) .....                          | 40 |

| 4.6.1 出力ポートの構成 .....                                                        | 40 |

| 4.6.2 マスクオプション .....                                                        | 40 |

| 4.6.3 ハイインピーダンス制御 .....                                                     | 41 |

| 4.6.4 特殊出力 .....                                                            | 41 |

| 4.6.5 出力ポートのI/Oメモリ .....                                                    | 43 |

| 4.6.6 プログラミング上の注意事項 .....                                                   | 45 |

| 4.7 入出力兼用ポート( P00 ~ P03, P10 ~ P13, P20 ~ P23, P30 ~ P33, P40 ~ P43 ) ..... | 46 |

| 4.7.1 入出力兼用ポートの構成 .....                                                     | 46 |

| 4.7.2 マスクオプション .....                                                        | 47 |

| 4.7.3 I/O制御レジスタと入力/出力モード .....                                              | 47 |

| 4.7.4 入力モード時のプルアップ .....                                                    | 47 |

| 4.7.5 入出力兼用ポートのI/Oメモリ .....                                                 | 48 |

| 4.7.6 プログラミング上の注意事項 .....                                                   | 51 |

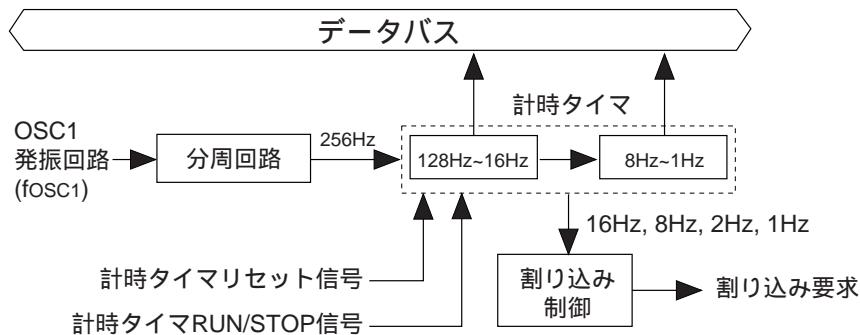

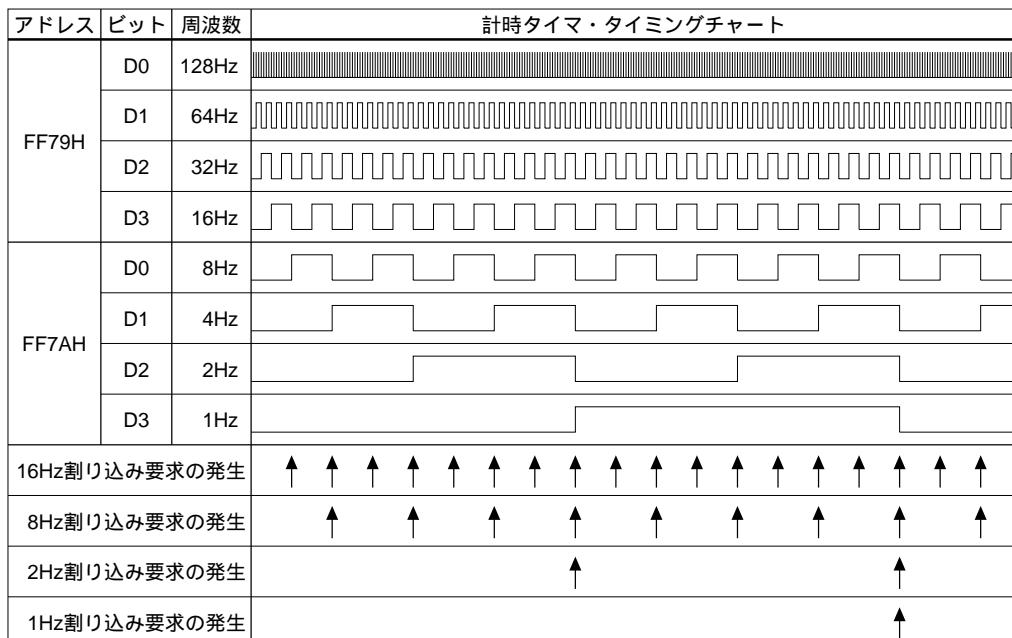

| 4.8 計時タイマ .....                                                             | 52 |

| 4.8.1 計時タイマの構成 .....                                                        | 52 |

| 4.8.2 データの読み出しとホールド機能 .....                                                 | 52 |

| 4.8.3 割り込み機能 .....                                                          | 53 |

| 4.8.4 計時タイマのI/Oメモリ .....                                                    | 54 |

| 4.8.5 プログラミング上の注意事項 .....                                                   | 55 |

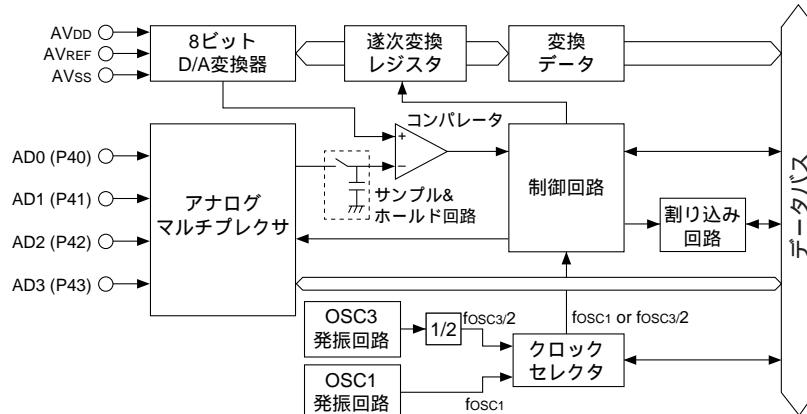

| 4.9 A/D変換器 .....                                                            | 56 |

| 4.9.1 A/D変換器の特徴と構成 .....                                                    | 56 |

| 4.9.2 A/D変換器の端子構成 .....                                                     | 56 |

| 4.9.3 マスクオプション .....                                                        | 57 |

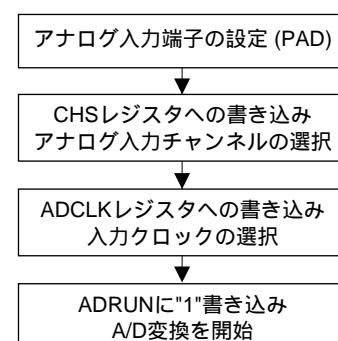

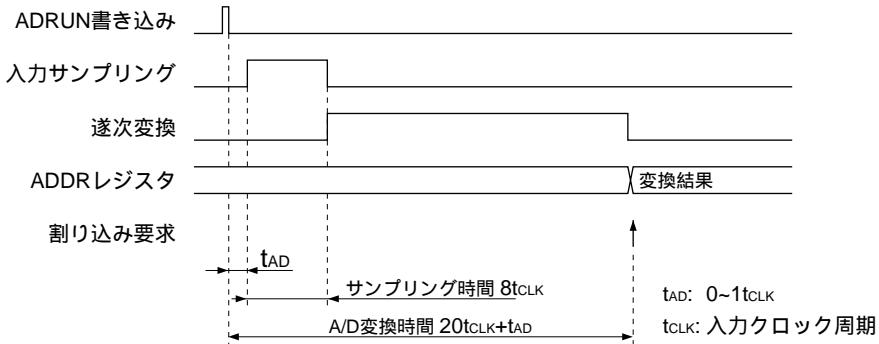

| 4.9.4 A/D変換の制御 .....                                                        | 57 |

| 4.9.5 割り込み機能 .....                                                          | 59 |

| 4.9.6 A/D変換器のI/Oメモリ .....                                                   | 60 |

| 4.9.7 プログラミング上の注意事項 .....                                                   | 62 |

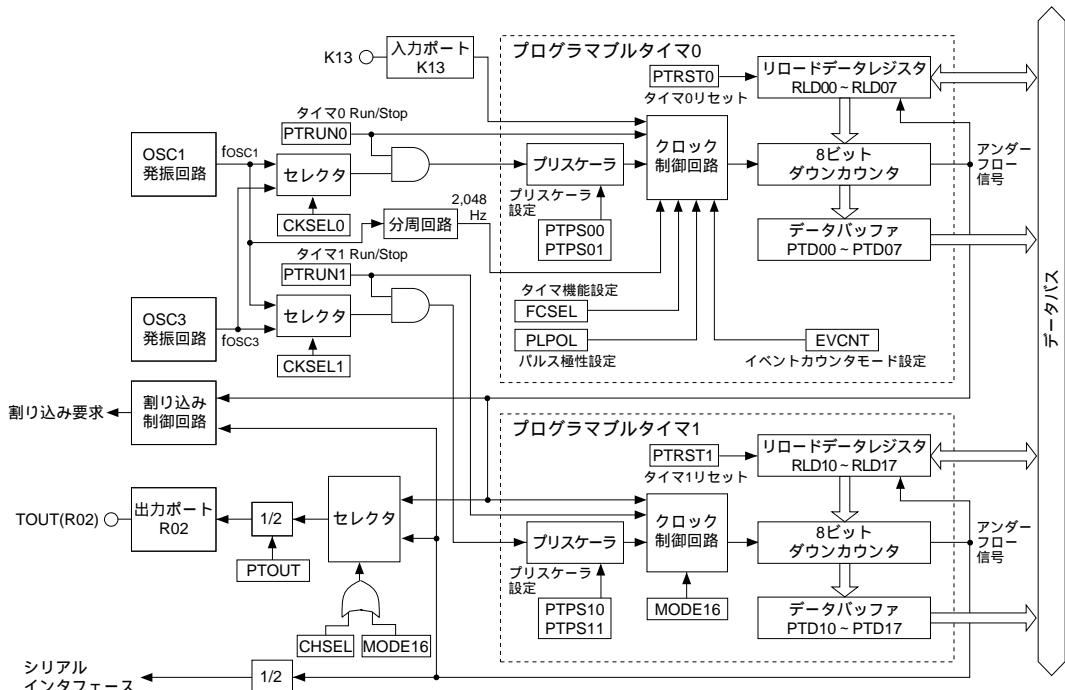

| 4.10 プログラマブルタイマ .....                                                       | 63 |

| 4.10.1 プログラマブルタイマの構成 .....                                                  | 63 |

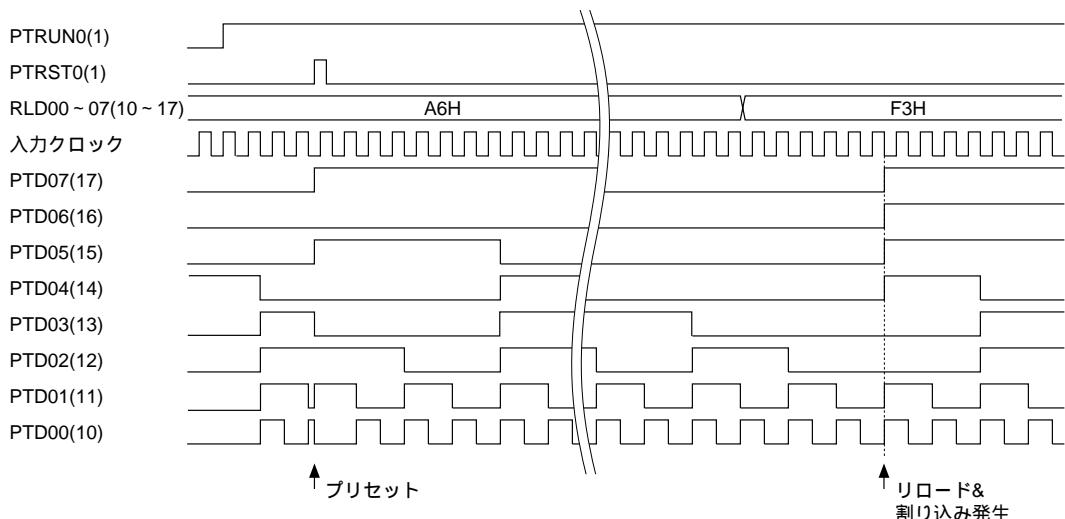

| 4.10.2 2チャンネル×8ビットタイマ( MODE16 = "0" )の動作 .....                              | 64 |

| 4.10.2.1 カウンタ初期値の設定とダウンカウント動作 .....                                         | 64 |

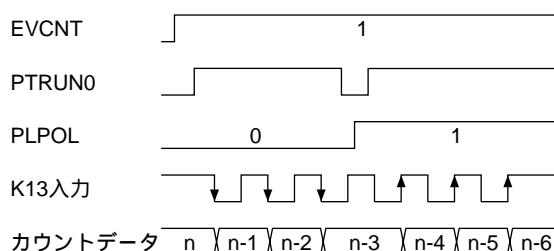

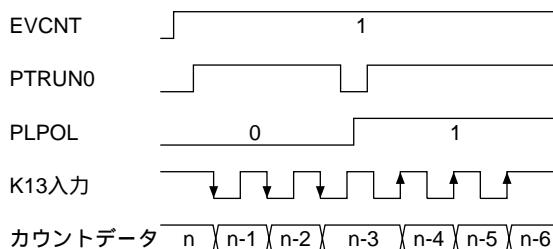

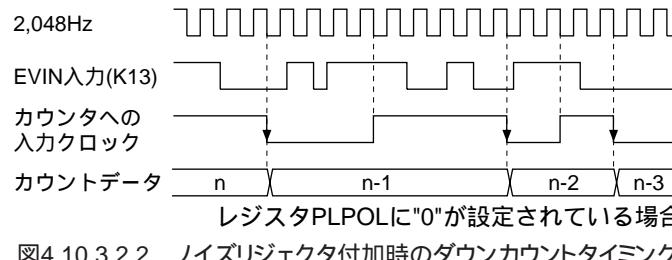

| 4.10.2.2 カウンタモード .....                                                      | 65 |

| 4.10.2.3 タイマモード入力クロックの設定 .....                                              | 66 |

| 4.10.2.4 割り込み機能 .....                                                       | 67 |

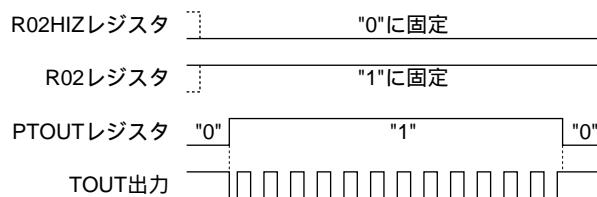

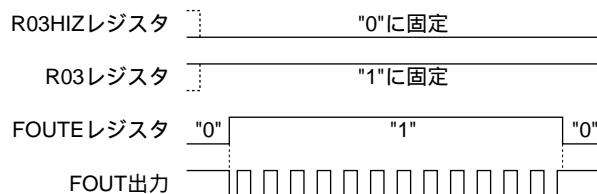

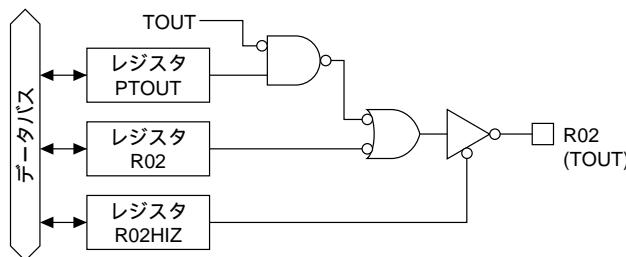

| 4.10.2.5 TOUT出力の設定 .....                                                    | 67 |

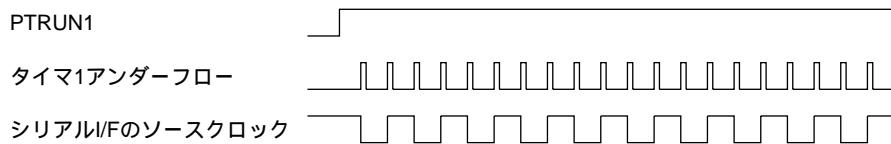

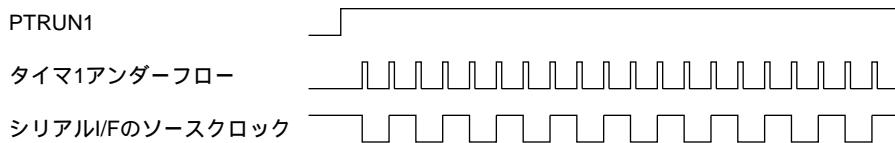

| 4.10.2.6 シリアルインターフェースの転送速度設定 .....                                          | 68 |

|                                                  |            |

|--------------------------------------------------|------------|

| 4.10.3 1チャンネル×16ビットタイマ( MODE16 = "1" )の動作 .....  | 68         |

| 4.10.3.1 カウンタ初期値の設定とダウンカウント動作 .....              | 68         |

| 4.10.3.2 カウンタモード .....                           | 69         |

| 4.10.3.3 タイマモード入力クロックの設定 .....                   | 70         |

| 4.10.3.4 割り込み機能 .....                            | 71         |

| 4.10.3.5 TOUT出力の設定 .....                         | 71         |

| 4.10.3.6 シリアルインターフェースの転送速度設定 .....               | 72         |

| 4.10.4 プログラマブルタイマのI/Oメモリ .....                   | 73         |

| 4.10.5 プログラミング上の注意事項 .....                       | 78         |

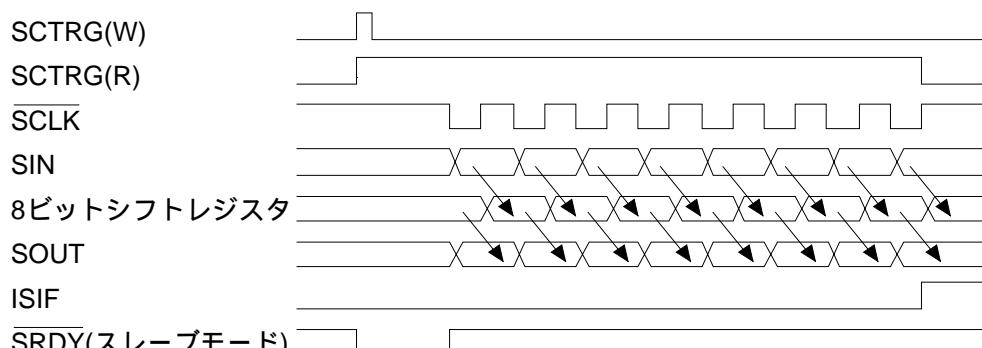

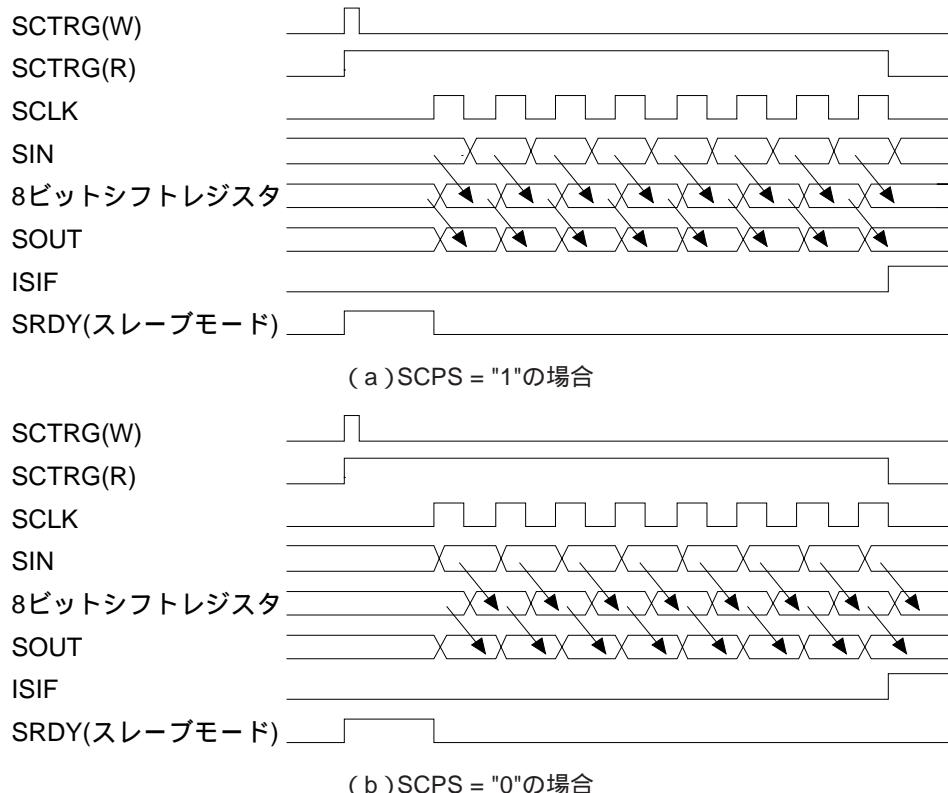

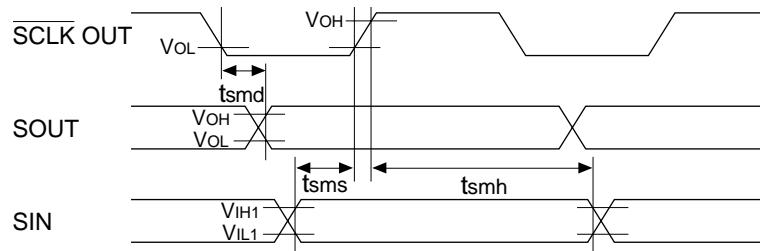

| 4.11 シリアルインターフェース( SIN, SOUT, SCLK, SRDY ) ..... | 79         |

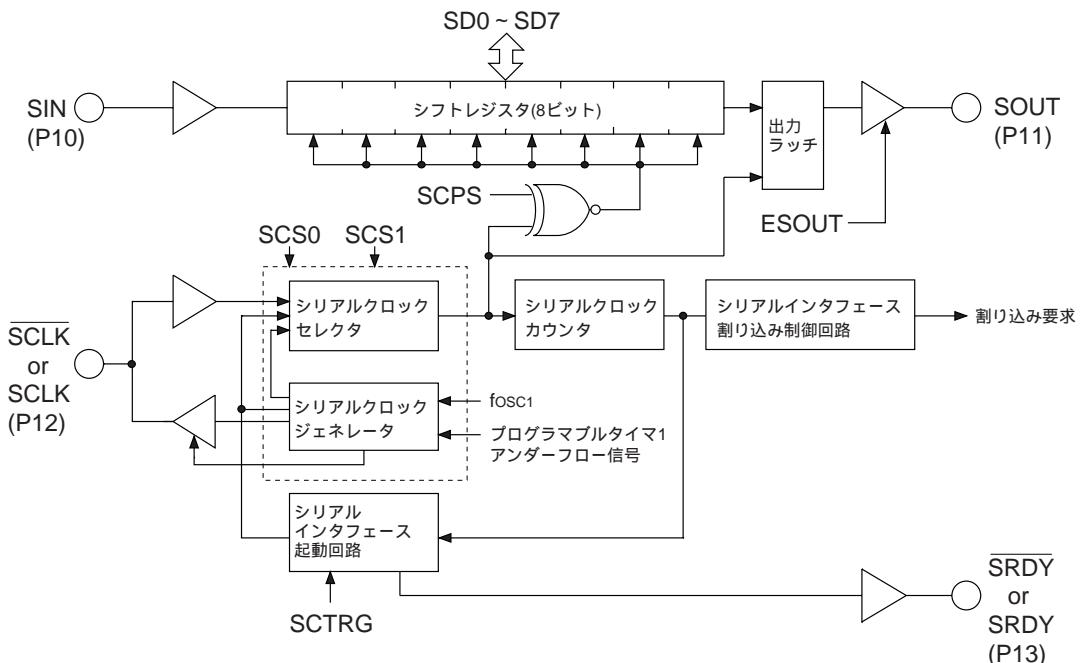

| 4.11.1 シリアルインターフェースの構成 .....                     | 79         |

| 4.11.2 マスクオプション .....                            | 80         |

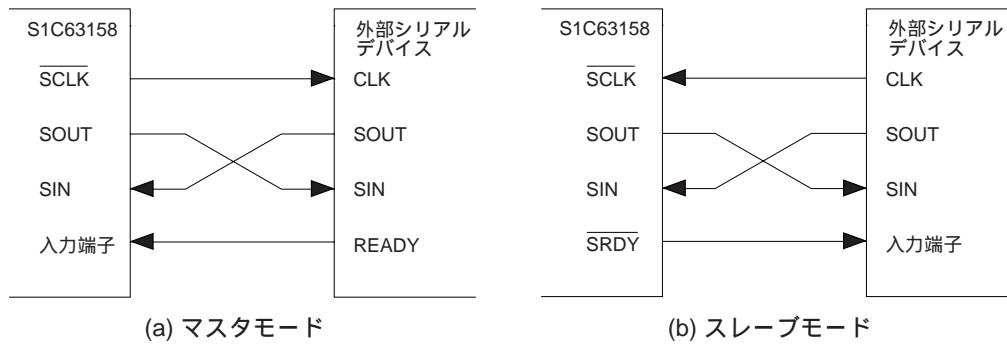

| 4.11.3 シリアルインターフェースのマスタモードとスレーブモード .....         | 80         |

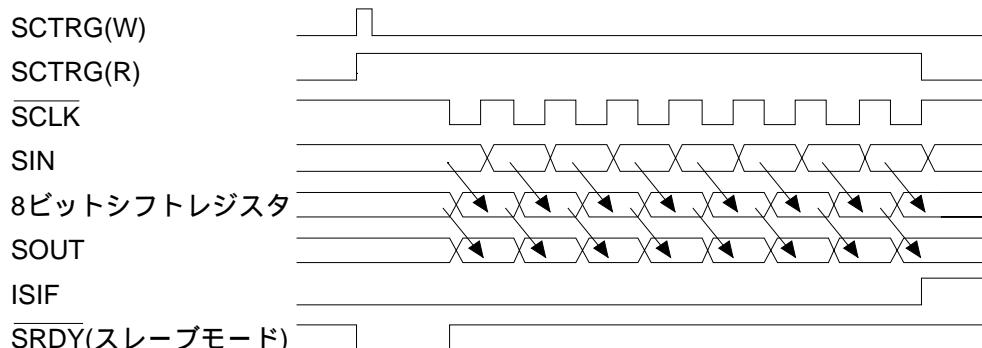

| 4.11.4 データの入出力と割り込み .....                        | 81         |

| 4.11.5 シリアルインターフェースのI/Oメモリ .....                 | 85         |

| 4.11.6 プログラミング上の注意事項 .....                       | 89         |

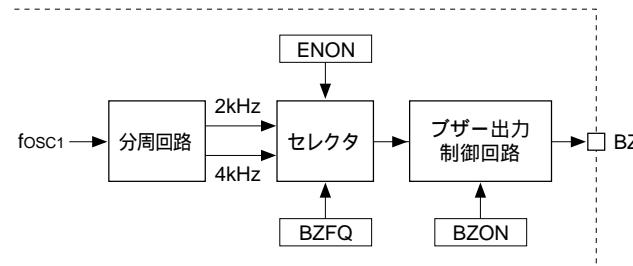

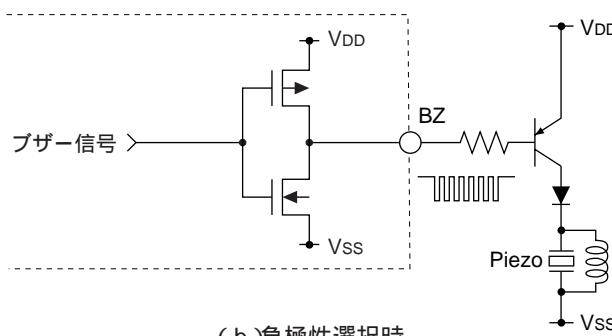

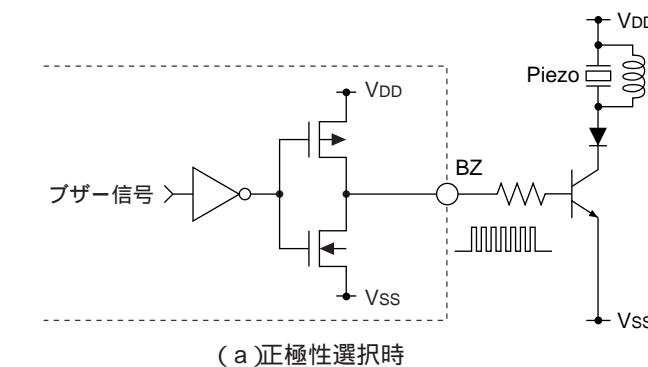

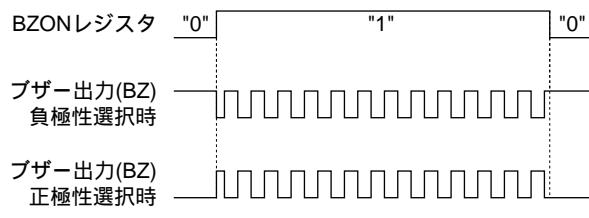

| 4.12 ブザー出力回路 .....                               | 90         |

| 4.12.1 ブザー出力回路の構成 .....                          | 90         |

| 4.12.2 マスクオプション .....                            | 90         |

| 4.12.3 ブザー出力の制御 .....                            | 91         |

| 4.12.4 ブザー出力回路のI/Oメモリ .....                      | 92         |

| 4.12.5 プログラミング上の注意事項 .....                       | 92         |

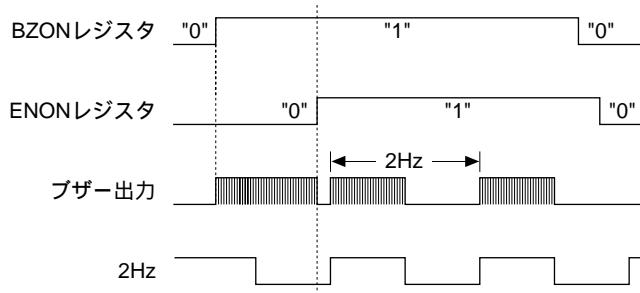

| 4.13 SVD( 電源電圧検出 )回路 .....                       | 93         |

| 4.13.1 SVD回路の構成 .....                            | 93         |

| 4.13.2 SVD動作 .....                               | 93         |

| 4.13.3 SVD回路のI/Oメモリ .....                        | 94         |

| 4.13.4 プログラミング上の注意事項 .....                       | 94         |

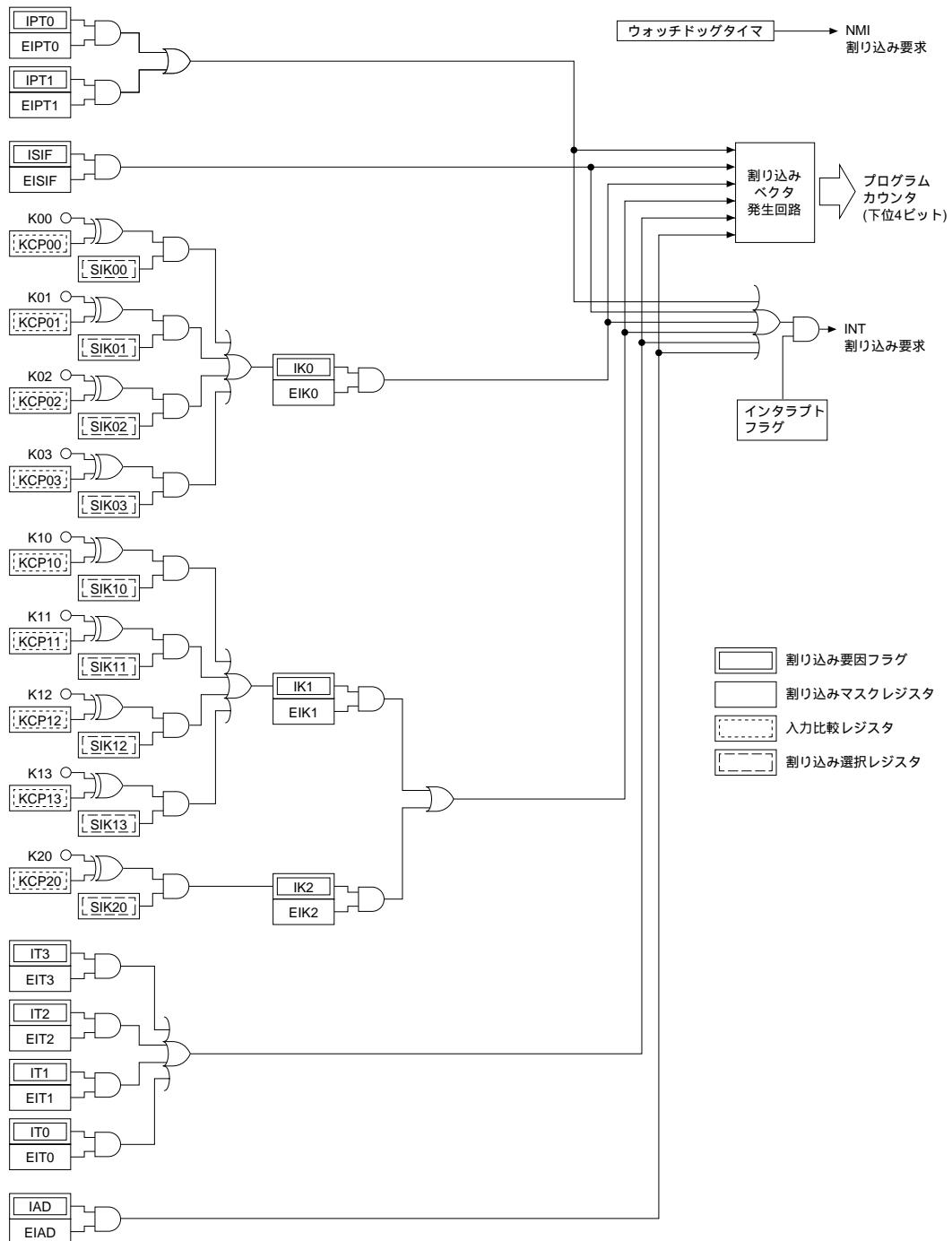

| 4.14 割り込みとHALT .....                             | 95         |

| 4.14.1 割り込みの要因 .....                             | 97         |

| 4.14.2 割り込みの個別マスク .....                          | 98         |

| 4.14.3 割り込みベクタ .....                             | 98         |

| 4.14.4 割り込みのI/Oメモリ .....                         | 99         |

| 4.14.5 プログラミング上の注意事項 .....                       | 101        |

| <b>5 注意事項のまとめ .....</b>                          | <b>102</b> |

| 5.1 低消費電流化のための注意事項 .....                         | 102        |

| 5.2 個別機能についての注意事項のまとめ .....                      | 103        |

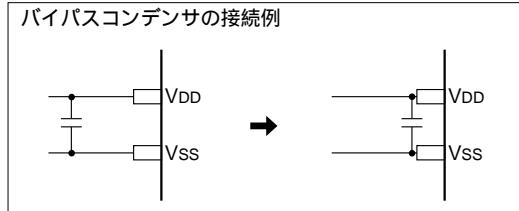

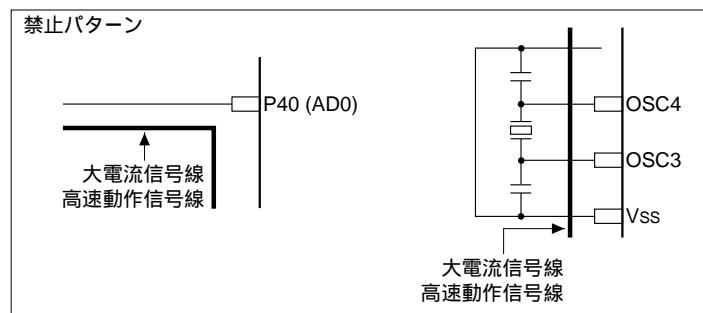

| 5.3 実装上の注意事項 .....                               | 107        |

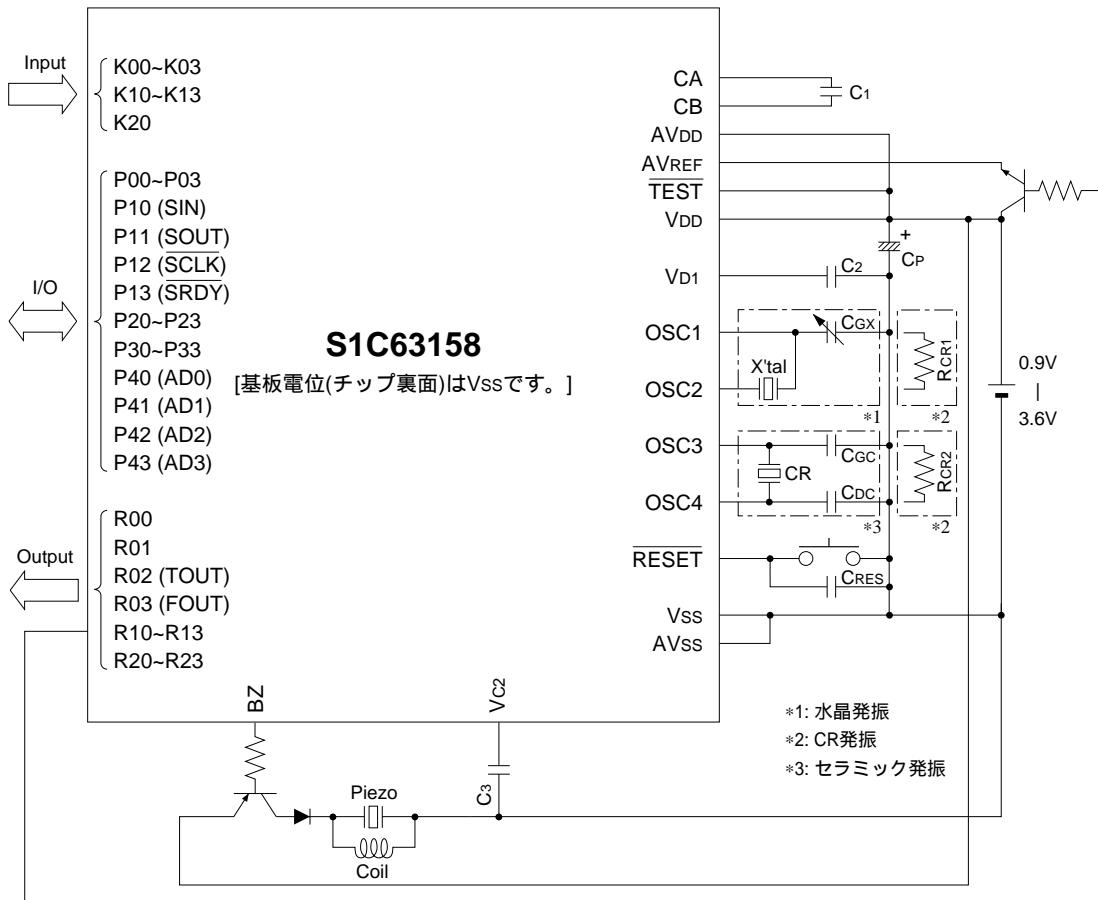

| <b>6 基本外部結線図 .....</b>                           | <b>109</b> |

| <b>7 電気的特性 .....</b>                             | <b>110</b> |

| 7.1 絶対最大定格 .....                                 | 110        |

| 7.2 推奨動作条件 .....                                 | 110        |

| 7.3 DC特性 .....                                   | 111        |

|                                                    |                    |     |

|----------------------------------------------------|--------------------|-----|

| 7.4                                                | アナログ回路特性・消費電流      | 112 |

| 7.5                                                | 発振特性               | 113 |

| 7.6                                                | シリアルインターフェースAC特性   | 116 |

| 7.7                                                | タイミングチャート          | 117 |

| 8                                                  | パッケージ              | 118 |

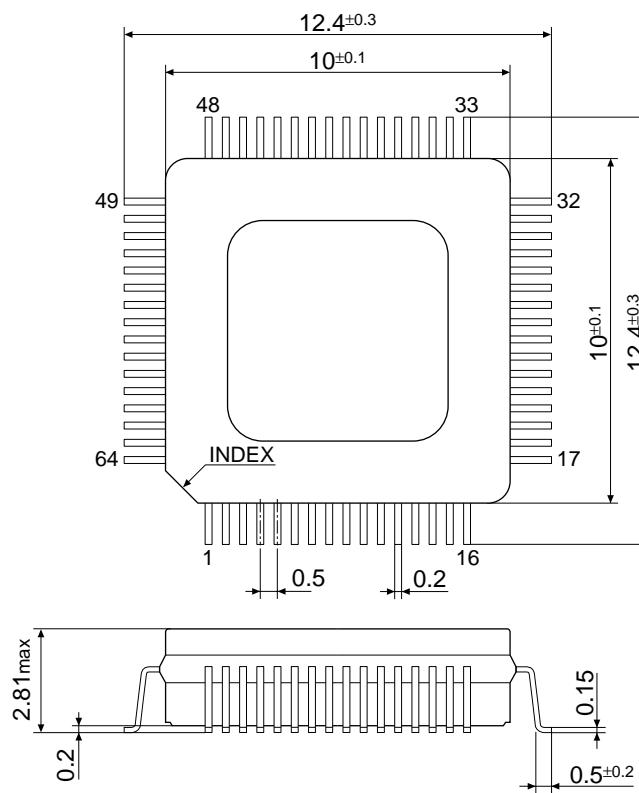

| 8.1                                                | プラスチックパッケージ        | 118 |

| 8.2                                                | テストサンプル用セラミックパッケージ | 120 |

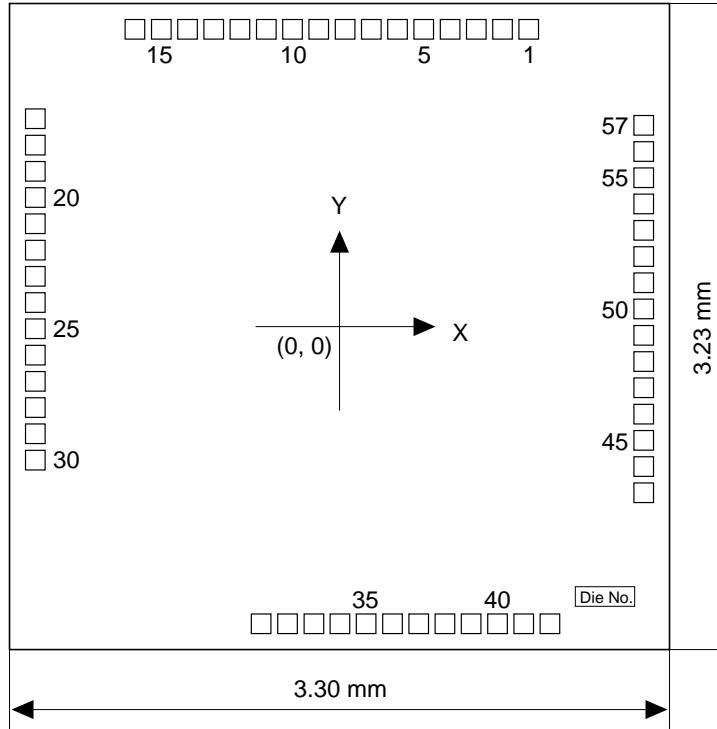

| 9                                                  | パッド配置              | 121 |

| 9.1                                                | パッド配置図             | 121 |

| 9.2                                                | パッド座標              | 121 |

| APPENDIX S5U1C63000P Manual                        |                    |     |

| ( Peripheral Circuit Board for S1C63158/358/P366 ) |                    | 122 |

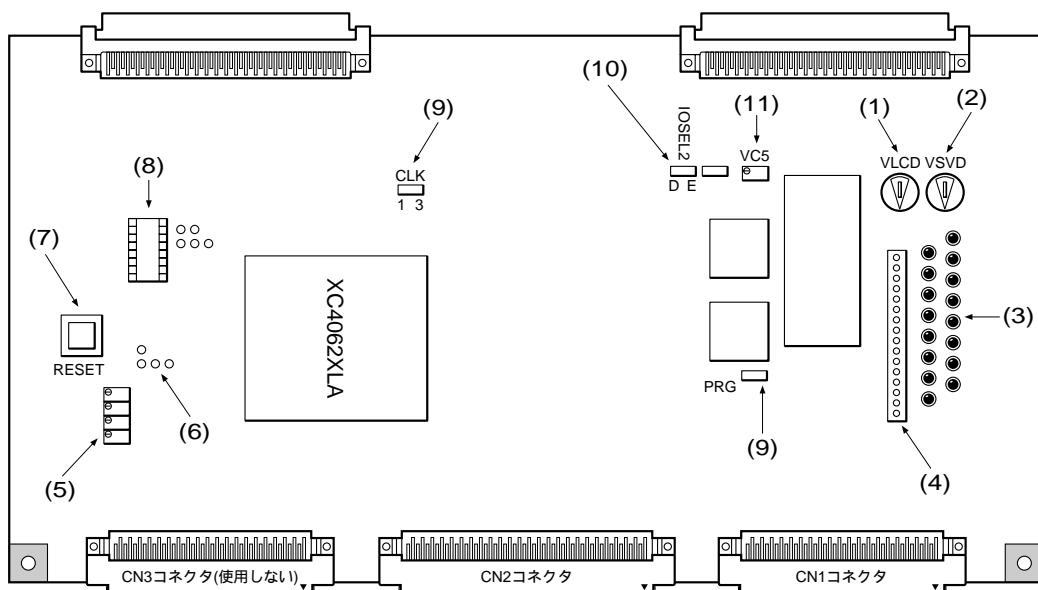

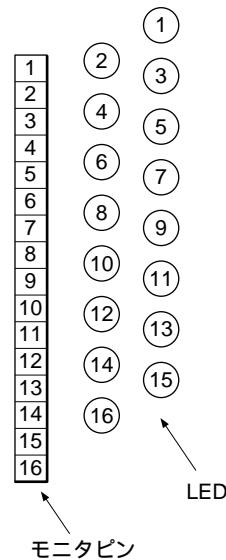

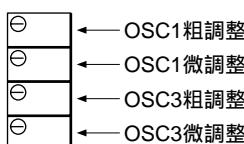

| A.1                                                | 各部の名称と機能           | 122 |

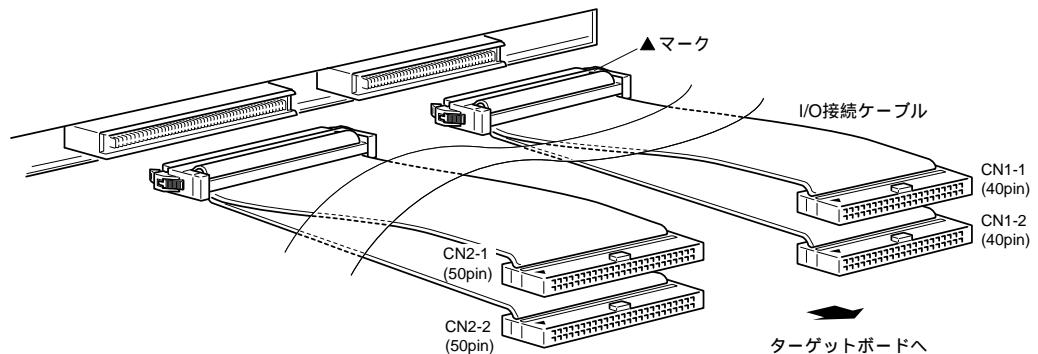

| A.2                                                | ターゲットシステムとの接続      | 125 |

| A.3                                                | 使用上の注意             | 127 |

| A.3.1                                              | 操作上の注意事項           | 127 |

| A.3.2                                              | 実ICとの相違点           | 127 |

# 1 概要

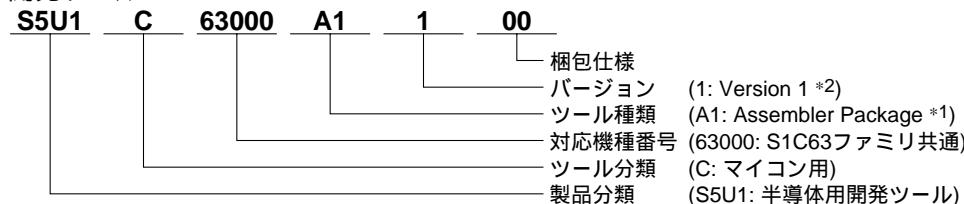

S1C63158は高性能4ビットCPU S1C63000を中心に、ワンチップ上にROM( 8,192ワード×13ビット ) RAM ( 512ワード×4ビット ) シリアルインターフェース、ウォッチドッグタイマ、プログラマブルタイマ、タイムベースカウンタ( 1系統 ) SVD回路、4チャンネルA/D変換器、A/D変換器を使用して入力キーを識別可能な特殊入力ポート等を内蔵したマイクロコンピュータです。低電圧/高速動作( 4MHz Max. ) および低消費電流 ( HALT時消費電流2μA Typ. ) 等の特長を持ち、ヘッドフォンステレオ等、電池駆動を必要とする各種携帯機器への応用に最適です。

## 1.1 特長

|                 |                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| OSC1発振回路        | 32.768kHz( Typ. )水晶発振回路、またはCR発振回路( *1 )                                                                                  |

| OSC3発振回路        | 2MHz( Typ. )CR発振回路、または4MHz( Max. )セラミック発振回路( *1 )                                                                        |

| インストラクションセット    | 基本命令 46種類( 全命令数 411種類 ) アドレッシングモード 8種類                                                                                   |

| インストラクション実行時間   | 32.768kHz動作時: 61μsec( Min. )<br>4MHz動作時: 0.5μsec( Min. )                                                                 |

| ROM容量           | 命令ROM: 8,192ワード×13ビット                                                                                                    |

| RAM容量           | データメモリ: 512ワード×4ビット                                                                                                      |

| 入力ポート           | 9ビット 8ビット( プルアップ抵抗の付加が可能*1 )<br>1ビット( A/D変換によるキーポジション検出割り込みを発生 )                                                         |

| 出力ポート           | 12ビット( 2ビットを特殊出力に切り換え可能*2 )                                                                                              |

| 入出力兼用ポート        | 20ビット( 4ビットをシリアル入出力に切り換え可能*2 )<br>( 4ビットをA/D変換器入力に切り換え可能*2 )                                                             |

| シリアルインターフェース    | 1ポート( クロック同期式8ビット )                                                                                                      |

| タイムベースカウンタ      | 1系統( 計時タイマ )                                                                                                             |

| プログラマブルタイマ      | 内蔵 2チャンネル×8ビットまたは1チャンネル×16ビット( *2 )<br>イベントカウンタ機能付き                                                                      |

| ウォッチドッグタイマ      | 内蔵                                                                                                                       |

| A/D変換器          | 分解能 8ビット<br>最大誤差: ±3LSB<br>A/Dクロック: 1MHz以下( 0.9V ~ 3.6V。ただし、1.6V以下ではVc2モード )                                             |

| ブザー出力           | ブザー周波数: 2kHzまたは4kHz( *2 ) 2Hzインターバル出力( *2 )                                                                              |

| 電源電圧検出( SVD )回路 | 16値プログラマブル( 1.05V ~ 2.60V )                                                                                              |

| 外部割り込み          | 入力ポート割り込み 2系統<br>キー検出割り込み 1系統                                                                                            |

| 内部割り込み          | 計時タイマ割り込み 4系統<br>プログラマブルタイマ割り込み 2系統<br>シリアルインターフェース割り込み 1系統<br>A/D変換器割り込み 1系統                                            |

| 電源電圧            | 0.9V ~ 3.6V                                                                                                              |

| 動作温度範囲          | -20°C ~ 85°C                                                                                                             |

| 消費電流( Typ. )    | シングルクロック: HALT時( 32kHz ) 1.5V( 通常モード ) 2μA<br>動作時( 32kHz ) 1.5V( 通常モード ) 4μA<br>ツインクロック: 動作時( 4MHz ) 3.0V( 通常モード ) 900μA |

| 出荷形態            | QFP12-48pin、QFP13-64pin( プラスチック ) またはチップ                                                                                 |

\*1: マスクオプションにより選択

\*2: ソフトウェアにより選択

## 1.2 ブロック図

図1.2.1 ブロック図

### 1.3 端子配置図

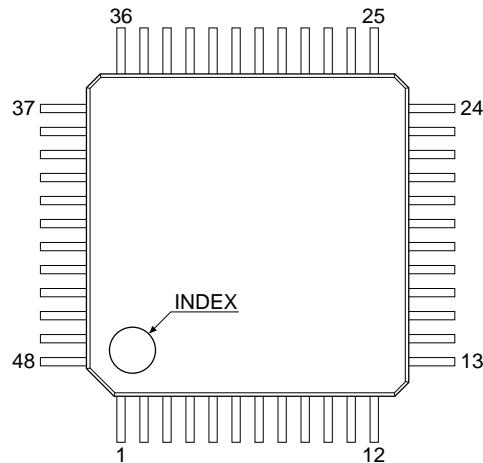

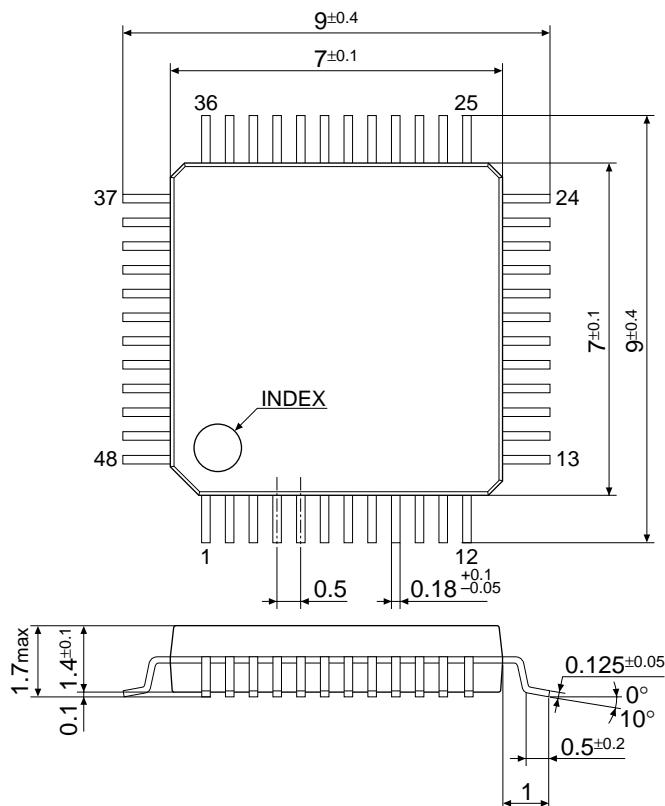

QFP12-48pin

| No. | 端子名             | No. | 端子名             | No. | 端子名  | No. | 端子名 |

|-----|-----------------|-----|-----------------|-----|------|-----|-----|

| 1   | V <sub>SS</sub> | 13  | V <sub>C2</sub> | 25  | P10  | 37  | R01 |

| 2   | OSC1            | 14  | P43             | 26  | P03  | 38  | R00 |

| 3   | OSC2            | 15  | P42             | 27  | P02  | 39  | BZ  |

| 4   | V <sub>D1</sub> | 16  | P41             | 28  | P01  | 40  | K00 |

| 5   | OSC3            | 17  | P40             | 29  | P00  | 41  | K01 |

| 6   | OSC4            | 18  | P23             | 30  | R13  | 42  | K02 |

| 7   | V <sub>DD</sub> | 19  | P22             | 31  | R12  | 43  | K03 |

| 8   | RESET           | 20  | P21             | 32  | R11  | 44  | K10 |

| 9   | TEST            | 21  | P20             | 33  | R10  | 45  | K11 |

| 10  | AVREF           | 22  | P13             | 34  | R03  | 46  | K12 |

| 11  | CB              | 23  | P12             | 35  | R02  | 47  | K13 |

| 12  | CA              | 24  | P11             | 36  | N.C. | 48  | K20 |

N.C.: No Connection

図1.3.1 端子配置図( QFP12-48pin)

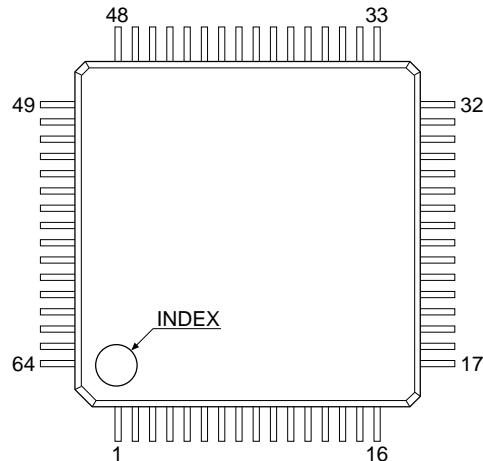

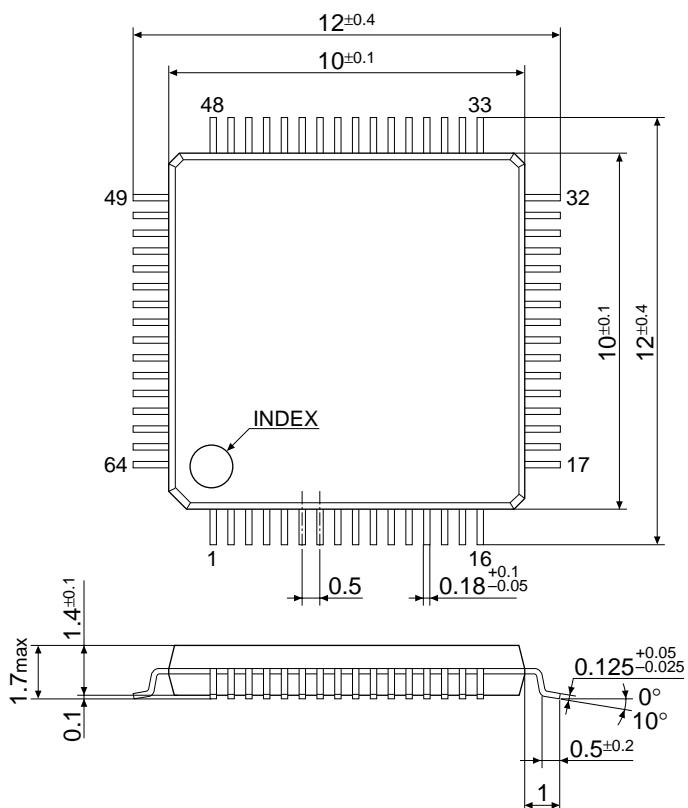

QFP13-64pin

| No. | 端子名             | No. | 端子名 | No. | 端子名  | No. | 端子名  |

|-----|-----------------|-----|-----|-----|------|-----|------|

| 1   | V <sub>ss</sub> | 17  | P43 | 33  | P03  | 49  | N.C. |

| 2   | OSC1            | 18  | P42 | 34  | P02  | 50  | N.C. |

| 3   | OSC2            | 19  | P41 | 35  | P01  | 51  | N.C. |

| 4   | V <sub>D1</sub> | 20  | P40 | 36  | P00  | 52  | R01  |

| 5   | OSC3            | 21  | P33 | 37  | R23  | 53  | R00  |

| 6   | OSC4            | 22  | P32 | 38  | R22  | 54  | BZ   |

| 7   | V <sub>DD</sub> | 23  | P31 | 39  | R21  | 55  | K00  |

| 8   | RESET           | 24  | P30 | 40  | R20  | 56  | K01  |

| 9   | TEST            | 25  | P23 | 41  | R13  | 57  | K02  |

| 10  | AVDD            | 26  | P22 | 42  | R12  | 58  | K03  |

| 11  | AVSS            | 27  | P21 | 43  | R11  | 59  | K10  |

| 12  | AVREF           | 28  | P20 | 44  | R10  | 60  | K11  |

| 13  | CB              | 29  | P13 | 45  | R03  | 61  | K12  |

| 14  | CA              | 30  | P12 | 46  | R02  | 62  | K13  |

| 15  | V <sub>C2</sub> | 31  | P11 | 47  | N.C. | 63  | K20  |

| 16  | N.C.            | 32  | P10 | 48  | N.C. | 64  | N.C. |

N.C.: No Connection

図1.3.2 端子配置図( QFP13-64pin)

## 1.4 端子説明

表1.4.1 端子説明

| 端子名        | 端子No.    |          | 入出力 | 機能                           |

|------------|----------|----------|-----|------------------------------|

|            | QFP12-48 | QFP13-64 |     |                              |

| VDD        | 7        | 7        | -   | 電源(+)端子                      |

| VSS        | 1        | 1        | -   | 電源(-)端子                      |

| VD1        | 4        | 4        | -   | 発振および内部ロジック系定電圧出力端子          |

| VC2        | 13       | 15       | -   | 昇圧電源端子                       |

| CA, CB     | 12, 11   | 14, 13   | -   | 昇圧コンデンサ接続端子                  |

| OSC1       | 2        | 2        | I   | 水晶またはCR発振入力端子(マスクオプション選択)    |

| OSC2       | 3        | 3        | O   | 水晶またはCR発振出力端子(マスクオプション選択)    |

| OSC3       | 5        | 5        | I   | CRまたはセラミック発振入力端子(マスクオプション選択) |

| OSC4       | 6        | 6        | O   | CRまたはセラミック発振出力端子(マスクオプション選択) |

| K00~K03    | 40~43    | 55~58    | I   | 入力端子                         |

| K10~K13    | 44~47    | 59~62    | I   | 入力端子                         |

| K20        | 48       | 63       | I   | 入力端子(キーポジション検出割り込みポート)       |

| P00~P03    | 29~26    | 36~33    | I/O | 入出力端子                        |

| P10~P13    | 25~22    | 32~29    | I/O | 入出力端子(シリアルI/F入出力にソフト切り換え)    |

| P20~P23    | 21~18    | 28~25    | I/O | 入出力端子                        |

| P30~P33 *1 | -        | 24~21    | I/O | 入出力端子                        |

| P40~P43    | 17~14    | 20~17    | I/O | 入出力端子(A/D変換器入力として使用可能)       |

| R00        | 38       | 53       | O   | 出力端子                         |

| R01        | 37       | 52       | O   | 出力端子                         |

| R02        | 35       | 46       | O   | 出力端子(TOUT信号出力にソフト切り換え)       |

| R03        | 34       | 45       | O   | 出力端子(FOUT信号出力にソフト切り換え)       |

| R10~R13    | 33~30    | 44~41    | O   | 出力端子                         |

| R20~R23 *1 | -        | 40~37    | O   | 出力端子                         |

| AVDD *2    | -        | 10       | -   | アナログ回路系電源(+)端子               |

| AVSS *2    | -        | 11       | -   | アナログ回路系電源(-)端子               |

| AVREF      | 10       | 12       | -   | アナログ回路系基準電圧端子                |

| BZ         | 39       | 54       | O   | ブザー出力端子                      |

| RESET      | 8        | 8        | I   | イニシャルリセット入力端子                |

| TEST       | 9        | 9        | I   | テスト用入力端子                     |

\*1 QFP12-48pinパッケージの場合、P30～P33およびR20～R23は使用できません。

\*2 QFP12-48pinパッケージの場合、AVDDはVDDと、AVSSはVssとIC内部で短絡されます。

## 1.5 マスクオプション

S1C63158には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択にはS1C63158の開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogを使用します。winfogによって作成したデータをもとに最終的なICのマスクパターン生成が行われます。winfogについては"S5U1C63000A Manual"を参照してください。

### S1C63158のマスクオプション

#### (1)出荷形態

プラスチックパッケージ( QFP12-48pin, QFP13-64pin )またはチップから選択できます。

#### (2)入力ポート( K00～K03 )同時LOW入力による外部リセット

この機能は、複数キーの同時押しによってICをリセットするもので、この機能を使用するかしないかをマスクオプションで選択できます。また、使用する場合は、同時に押すキーを接続する入力ポート( K00～K03 )の組み合わせを選択します。詳細については"2.2.2 入力ポート( K00～K03 )の同時LOW入力"を参照してください。

### (3) 入力ポート同時LOW入力リセットの時間検定回路

入力ポート( K00 ~ K03 )同時LOW入力による外部リセット機能を使用する場合に、時間検定回路を使用するかしないか選択できます。時間検定回路を使用すると、規定時間以上の同時LOW入力があった場合のみ、リセット機能が働きます。詳細については"2.2.2 入力ポート( K00 ~ K03 )の同時LOW入力"を参照してください。

### (4) 入力ポートプルアップ抵抗

入力ポートにプルアップ抵抗を付加するかしないか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"4.5.3 マスクオプション"を参照してください。

### (5) 出力ポートの出力仕様

出力ポートR10 ~ R13およびR20 ~ R23の出力仕様として、コンプリメンタリ出力またはNチャンネルオープンドレイン出力が選択できます。選択は4ビット単位( R10 ~ R13およびR20 ~ R23 )で行います。R00 ~ R03はコンプリメンタリ出力としてのみ使用可能で、詳細については"4.6.2 マスクオプション"を参照してください。

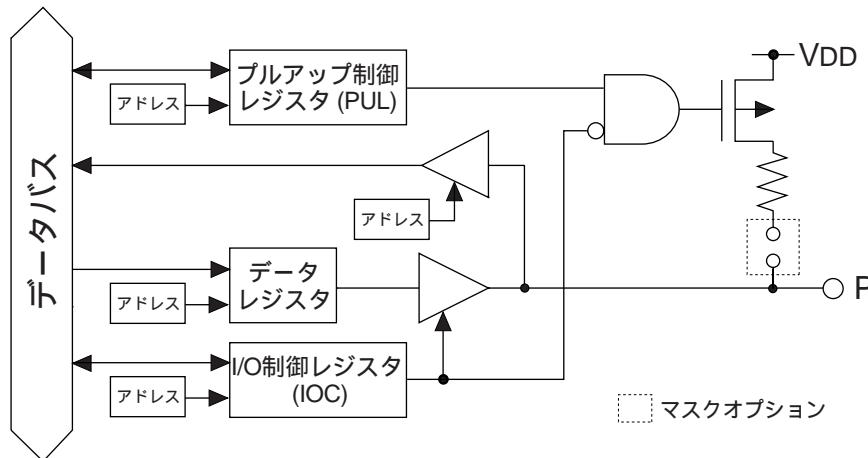

### (6) 入出力兼用ポートの出力仕様/プルアップ抵抗

入出力兼用ポートが出力モードの際の出力仕様として、コンプリメンタリ出力またはNチャンネルオープンドレイン出力が選択できます。また入力モード時に働くプルアップ抵抗を付加するかしないか選択できます。選択は入出力兼用ポートによりビット単位または4ビット単位で行います。

1ビット単位: P20, P21, P22, P23, P30, P31, P32, P33, P40, P41, P42, P43

4ビット単位: P10 ~ P13

P00 ~ P03はコンプリメンタリ出力、プルアップありで固定となります。

詳細については"4.7.2 マスクオプション"を参照してください。

### (7) シリアルインターフェースの同期クロック極性

シリアルインターフェースの同期クロックSCLKおよびスレーブモード時のSRDY信号の極性を正極性とするか負極性とするか選択できます。詳細については"4.11.2 マスクオプション"を参照してください。

### (8) ブザー出力信号の極性

BZ端子から出力するブザー信号の極性が選択できます。駆動用外付けトランジスタに合わせ、正極性または負極性を選択します。詳細については"4.12.2 マスクオプション"を参照してください。

### (9) OSC1発振回路

OSC1発振回路には、水晶発振回路またはCR発振回路が選択できます。詳細については"4.4.2 OSC1発振回路"を参照してください。

### (10) OSC3発振回路

OSC3発振回路には、CR発振回路またはセラミック発振回路、あるいは使用しないことを選択できます。詳細については"4.4.3 OSC3発振回路"を参照してください。

#### マスクオプションリスト

S1C63158のオプションリストを以下に示します。各オプション項目には、複数の選択肢が用意されていますので、4章の"周辺回路と動作"を参照してシステムに合った内容を選択してください。使用しない機能についてもオプション設定が必要です。このオプションリストを参照しながら、S1C63158のオプション設定をS5U1C63000A内のwinfogの画面上で行ってください。詳細については"S5U1C63000A Manual"を参照してください。

##### 1. パッケージタイプの選択( Package type select )

1. チップ

2. QFP12-48

3. QFP13-64

##### 2. OSC3システムクロック( OSC3 system clock )

1. 使用しない

2. 使用する<セラミック 2MHz >

3. 使用する<CR( 2MHz )>

## 3. OSC1システムクロック( OSC1 system clock )

1. 水晶発振回路( 32.768kHz )

2. CR発振回路

## 4. キー同時押しリセット組み合わせ( Multiple key entry reset combination )

1. 使用しない

2. 使用する <K00, K01, K02, K03>

3. 使用する <K00, K01, K02>

4. 使用する <K00, K01>

## 5. キー同時押しリセット時間検定( Multiple key entry reset time authorize )

1. 使用しない

2. 使用する

## 6. 入力ポートプルアップ抵抗( Input port pull up resistor )

|           |       |       |

|-----------|-------|-------|

| K00 ..... | 1. あり | 2. なし |

| K01 ..... | 1. あり | 2. なし |

| K02 ..... | 1. あり | 2. なし |

| K03 ..... | 1. あり | 2. なし |

| K10 ..... | 1. あり | 2. なし |

| K11 ..... | 1. あり | 2. なし |

| K12 ..... | 1. あり | 2. なし |

| K13 ..... | 1. あり | 2. なし |

| K20 ..... | 1. あり | 2. なし |

## 7. 出力ポート出力仕様( Output port output specification )

|           |             |                |

|-----------|-------------|----------------|

| R1* ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R2* ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

## 8. I/Oポート出力仕様( I/O port output specification )

|           |             |                |

|-----------|-------------|----------------|

| P1* ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P20 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P21 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P22 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P23 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P30 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P31 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P32 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P33 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P40 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P41 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P42 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P43 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

## 9. I/Oポートプルアップ抵抗( I/O port pull up resistor )

|           |       |       |

|-----------|-------|-------|

| P1* ..... | 1. あり | 2. なし |

| P20 ..... | 1. あり | 2. なし |

| P21 ..... | 1. あり | 2. なし |

| P22 ..... | 1. あり | 2. なし |

| P23 ..... | 1. あり | 2. なし |

| P30 ..... | 1. あり | 2. なし |

| P31 ..... | 1. あり | 2. なし |

| P32 ..... | 1. あり | 2. なし |

| P33 ..... | 1. あり | 2. なし |

| P40 ..... | 1. あり | 2. なし |

| P41 ..... | 1. あり | 2. なし |

| P42 ..... | 1. あり | 2. なし |

| P43 ..... | 1. あり | 2. なし |

## 10. シリアルポートインタフェース極性( Serial port interface polarity )

1. 正極性

2. 負極性

## 11. サウンドジェネレータ出力仕様( Sound generator polarity for output )

1. 正極性

2. 負極性

## 2 電源系 および イニシャルリセット

### 2.1 電源系

S1C63158の動作電源電圧は次のとおりです。

0.9V ~ 3.6V

注: • 0.9V ~ 1.35Vを動作電源電圧とする場合はソフトウェアによる制御が必要です( 4.2項参照 )

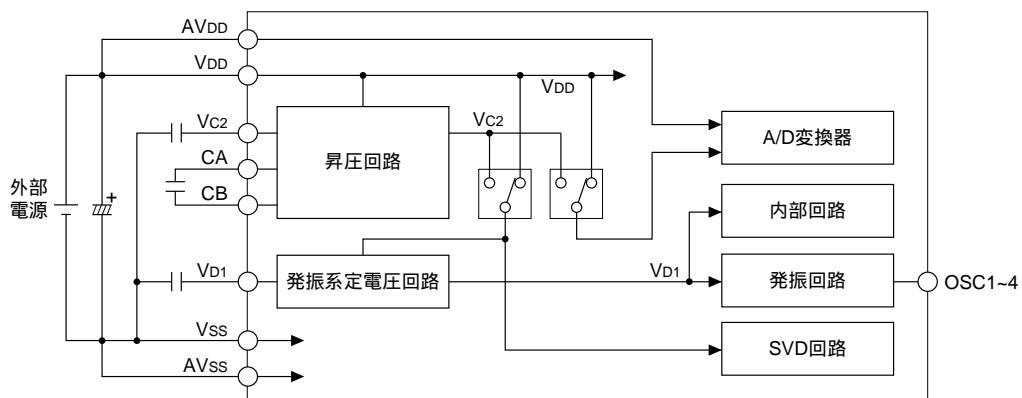

S1C63158は上記範囲の単一電源をVDD/AVDD - Vss/AVss間に与えることにより動作し、内部に必要な電圧を、内蔵された以下の電源回路によりIC自身で発生します。

| 回路系      | 電源回路                                                                          | 出力電圧                                                   |

|----------|-------------------------------------------------------------------------------|--------------------------------------------------------|

| 発振、内部回路  | 発振系定電圧回路                                                                      | V <sub>D1</sub>                                        |

| 発振系定電圧回路 | 電源電圧(V <sub>DD</sub> )または昇圧回路(V <sub>C2</sub> )                               | V <sub>DD</sub> またはV <sub>C2</sub>                     |

| A/D変換器   | アナログ電源電圧(AV <sub>DD</sub> )および電源電圧(V <sub>DD</sub> )または昇圧回路(V <sub>C2</sub> ) | AV <sub>DD</sub> およびV <sub>DD</sub> またはV <sub>C2</sub> |

注: • 内部電源回路の出力電圧による外付け負荷の駆動は禁止します。

• 電圧値、駆動能力については"7 電気的特性"を参照してください。

図2.1.1 電源系の構成

#### 2.1.1 発振回路および内部回路用電圧<VD1>

V<sub>D1</sub>は発振回路および内部ロジック回路用の電圧で、発振を安定させるため発振系定電圧回路で発生しています。

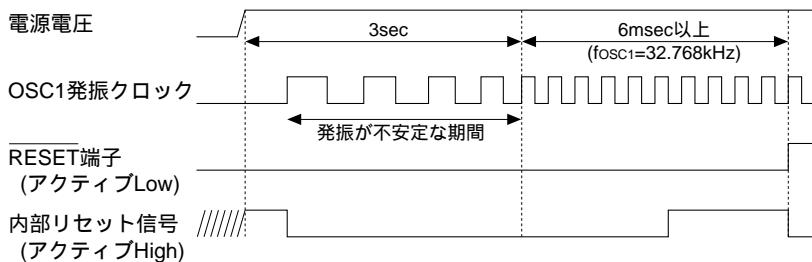

S1C63158はツインクロック仕様となっており、2種類の発振回路OSC1およびOSC3を内蔵しています。通常動作時はOSC1クロックを使用し、高速動作が必要なときにソフトウェアによってOSC3クロックに切り換えます。その際には、発振回路およびそれぞれのクロックによる内部回路の動作を安定させるため、動作電圧V<sub>D1</sub>もソフトウェアによって切り換える必要があります。発振系定電圧回路はV<sub>D1</sub>の電圧値として以下の2種類が output 可能で、ソフトウェアにより発振回路と発振周波数にしたがった値に設定します。

1. OSC1クロックによる動作時: V<sub>D1</sub> = 1.3V

2. OSC3クロックによる動作時: V<sub>D1</sub> = 2.1V

V<sub>D1</sub>の切り換え方法については"4.4 発振回路"を参照してください。

ただし、マスクオプションでOSC1にCR発振回路を選択し、OSC3発振回路( CRまたはセラミック )を使用するとした場合はV<sub>D1</sub>の電圧値が2.1V固定となりますので、ソフトウェアによるV<sub>D1</sub>の切り換えは必要ありません。OSC3発振回路を使用しない場合は、OSC1がCR発振回路の場合でもV<sub>D1</sub>=1.3Vで動作可能です。

### 2.1.2 発振系定電圧回路用電源電圧

#### ( 1 )Vc2モード( 昇圧モード )

S1C63158は0.9V ~ 3.6Vの電源電圧により動作します。ただし、発振系定電圧回路用に、シングルクロック( OSC1 )動作時は最低1.35Vの電源電圧が、ツインクロック( OSC3, Typ. 2MHz )動作時は最低2.2Vの電源電圧が必要となります。このため以下の電源電圧VDDで動作させる場合はVc2モードに切り換え、発振系定電圧回路をVc2で駆動してください。

- シングルクロック( OSC1 )動作時:  $VDD = 0.9V \sim 1.35V$  (  $Vc2 = 1.8V \sim 2.7V$  )

Vc2モードでは消費電流が増加しますので、電源電圧が必要以上の場合はこのモードに設定しないでください。

注: ブザー駆動時やランプ点灯時など、電池の負荷が重くなり電源電圧が低下する場合(重負荷時)または電池の寿命による電源電圧低下をSVD回路で検出した場合、Vc2モードを設定してください。

#### ( 2 )通常モード

このモードでは、発振系定電圧回路が1.35V ~ 3.6V( OSC3クロックを使用する場合は2.2V ~ 3.6V )の電源電圧VDDによって直接動作します。イニシャルリセット時は、このモードに設定されます。

表2.1.2.1 電源電圧と動作モードの対応( 発振系定電圧回路 )

| 電源回路  | 動作条件       | 電源電圧VDD( V ) |          |         |

|-------|------------|--------------|----------|---------|

|       |            | 0.9~1.35     | 1.35~2.2 | 2.2~3.6 |

| 発振系   | OSC1       | Vc2モード       | 通常モード*   |         |

| 定電圧回路 | OSC3, 4MHz | 動作不可         |          | 通常モード   |

\* 上記"( 1 )Vc2モード"の注参照

動作モードの設定方法については"4.2 電源と動作モードの設定"を参照してください。

### 2.1.3 A/D変換回路用電源電圧

#### ( 1 )Vc2モード( 昇圧モード )

A/D変換器は0.9V ~ 3.6Vの電源電圧により動作します。ただし、A/D変換器を最大±3LSB以内の誤差( A/Dクロック 1MHz )で動作させるためには、最低1.6Vの電源電圧が必要となります。このため、電源電圧VDDが1.6V以下の場合はVc2モードに切り換え、A/D変換器をVc2で動作させてください。

#### ( 2 )通常モード

このモードでは、A/D変換器が1.6V以上の電源電圧VDDによって直接動作します。

表2.1.3.1 電源電圧と動作モードの対応(A/D変換器 )

| 回路     | 電源電圧VDD( V ) |         |

|--------|--------------|---------|

|        | 0.9~1.6      | 1.6~3.6 |

| A/D変換器 | Vc2モード       | 通常モード   |

## 2.2 イニシャルリセット

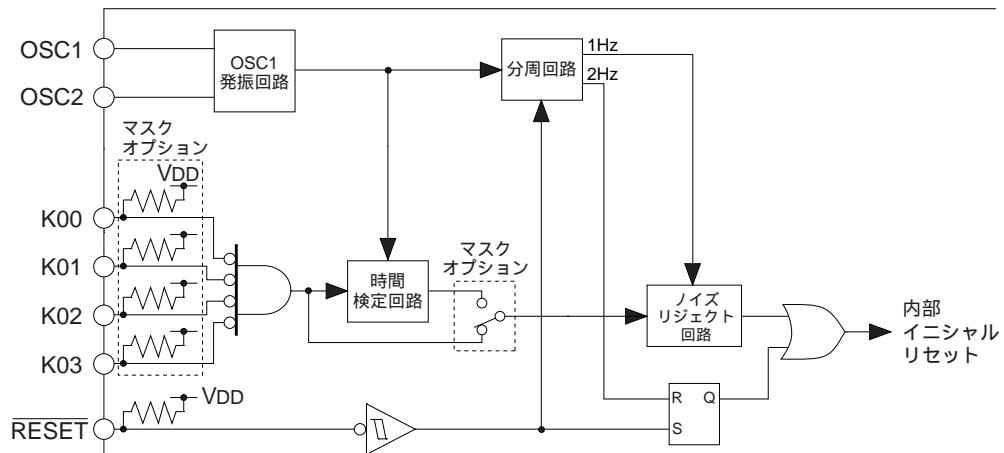

S1C63158は回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては次の2種類があります。

(1)  $\overline{\text{RESET}}$ 端子による外部イニシャルリセット

(2) K00～K03端子の同時LOWレベル入力による外部イニシャルリセット(マスクオプションで設定)

電源投入時は必ずこのリセット機能を使用し、ICを確実に初期化してください。電源投入のみでは動作が保証できません。

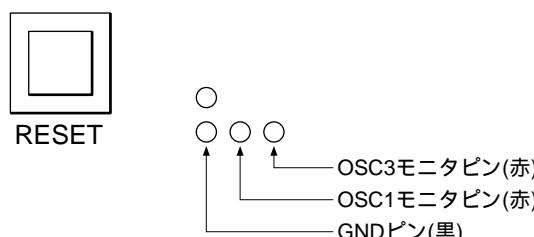

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

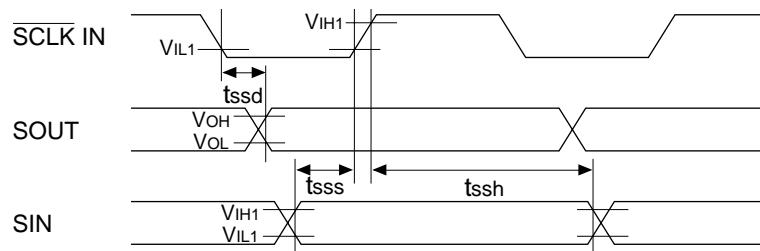

### 2.2.1 リセット端子( $\overline{\text{RESET}}$ )

外部よりリセット端子をLOWレベル(  $V_{SS}$  )にすることによりイニシャルリセットが行えます。

その後、リセット端子をHIGHレベル(  $V_{DD}$  )にすることによりイニシャルリセットは解除され、CPUが動作を開始します。

電源投入時、リセット入力信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチは、OSC1クロックを分周した2Hz信号で解除されるようになっています。

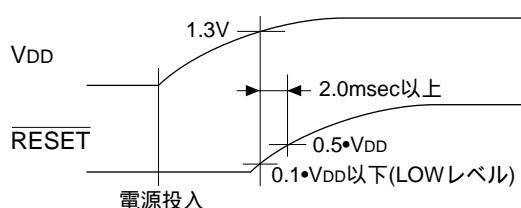

ICを確実にイニシャルリセットするためには、図2.2.1.1に示すタイミングでリセット端子をLOWレベルにしてください。

図2.2.1.1 電源投入時のイニシャルリセット

電源電圧が1.3V以上になるまで、リセット端子は0.1  $\cdot$   $V_{DD}$ 以下(LOWレベル)とします。

その後2.0msec以上、0.5  $\cdot$   $V_{DD}$ 以下のレベルを保持してください。

通常動作時は、リセット端子がHIGHレベルになった後、内部イニシャルリセットが解除されるまで、最大250msec(  $f_{OSC1}=32.768\text{kHz}$  )の時間を要します。確実にイニシャルリセットを行うためには、最低0.1msec以上、リセット入力をLOWレベルを保ってください。

### 2.2.2 入力ポート( K00 ~ K03 )の同時LOW入力

マスクオプションで選択された入力ポート( K00 ~ K03 )に、外部から同時にLOW入力を与えることによりイニシャルリセットが行えます。このイニシャルリセットはノイズリジェクト回路を通るため、通常動作中は 1.5msec(  $fosc1=32.768\text{kHz}$  )以上、指定入力ポート端子をLOWレベルに保ってください。また、電源投入時にはリセット端子の場合と同様に発振を開始するまで( 2.2.1項参照 ) 指定入力ポート端子をLOWレベルに保ってください。表2.2.2.1にマスクオプションで選択できる入力ポート( K00 ~ K03 )の組合せを示します。

表2.2.2.1 入力ポートの組合せ

|   |                 |

|---|-----------------|

| 1 | 使用しない           |

| 2 | K00*K01*K02*K03 |

| 3 | K00*K01*K02     |

| 4 | K00*K01         |

たとえば、マスクオプションで2の"K00\*K01\*K02\*K03"を選択した場合、K00 ~ K03の4ポートの入力が同時にLOWレベルになったときにイニシャルリセットを行います。3または4の場合は、選択した入力ポートの組合せが含まれるキー入力が行われたときにイニシャルリセットがかかります。

また、同時LOW入力の入力時間を検定し、規定時間( 1 ~ 2秒 )以上の入力があったときにイニシャルリセットを行う時間検定回路をマスクオプションで選択できます。

なお、このリセット機能を使用する場合、通常動作時に指定ポートが同時にLOWレベルにならないように注意してください。

### 2.2.3 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは表2.2.3.1のように初期化されます。

イニシャルリセットによって初期化されないレジスタ、フラグは必要に応じてプログラムで初期化する必要があります。

特にスタックポインタSP1およびSP2は必ずペアで設定してください。イニシャルリセット後は、SP1、SP2両方のスタックポインタがソフトウェアにより設定されるまでNMIを含むすべての割り込みがマスクされます。

EXTレジスタにデータを書き込むとEフラグがセットされ、次の命令が拡張アドレッシングモードで実行されます。そこに拡張アドレッシングが禁止されている命令を使用した場合、動作が保証されません。したがって、EXTレジスタの初期化のみを目的としたデータ書き込みは行わないでください。

拡張アドレッシングと使用可能な命令については"S1C63000コアCPUマニュアル"を参照してください。

表2.2.3.1 初期設定値

| CPUコア       |     |      |       |

|-------------|-----|------|-------|

| 名 称         | 記 号 | ビット長 | 設 定 値 |

| データレジスタA    | A   | 4    | 不定    |

| データレジスタB    | B   | 4    | 不定    |

| 拡張レジスタEXT   | EXT | 8    | 不定    |

| インデックスレジスタX | X   | 16   | 不定    |

| インデックスレジスタY | Y   | 16   | 不定    |

| プログラムカウンタ   | PC  | 16   | 0110H |

| スタックポインタSP1 | SP1 | 8    | 不定    |

| スタックポインタSP2 | SP2 | 8    | 不定    |

| ゼロフラグ       | Z   | 1    | 不定    |

| キャリーフラグ     | C   | 1    | 不定    |

| インタラプトフラグ   | I   | 1    | 0     |

| 拡張フラグ       | E   | 1    | 0     |

| キューレジスタ     | Q   | 16   | 不定    |

| 周辺回路     |      |       |

|----------|------|-------|

| 名 称      | ビット長 | 設 定 値 |

| RAM      | 4    | 不定    |

| 表示メモリ    | 4    | 不定    |

| その他の周辺回路 | -    | *     |

\* "4.1 メモリマップ"参照

### 2.2.4 イニシャルリセット時の端子設定

S1C63158の出力ポート(R端子)、入出力兼用ポート(P端子)は特殊出力端子やシリアルインターフェースの入出力端子およびA/D変換器の入力端子と兼用されており、それらの機能をソフトウェアで選択するようになっています。イニシャルリセット時、各端子はすべてが汎用出力ポート端子、汎用入出力兼用ポート端子として設定されますので、アプリケーションの初期化ルーチンでシステムに合った設定を行ってください。また、システム設計の際には、出力端子の初期状態にも注意してください。

表2.2.4.1に兼用端子設定の一覧を示します。

表2.2.4.1 兼用端子設定一覧

| 端子名     | イニシャルリセット時の<br>端子状態   | 特殊出力使用時 |      | シリアルI/F使用時 |         | A/D変換器<br>使用時 |

|---------|-----------------------|---------|------|------------|---------|---------------|

|         |                       | TOUT    | FOUT | Master     | Slave   |               |

| R00     | R00 ( HIGH出力 )        |         |      |            |         |               |

| R01     | R01 ( HIGH出力 )        |         |      |            |         |               |

| R02     | R02 ( HIGH出力 )        | TOUT    |      |            |         |               |

| R03     | R03 ( HIGH出力 )        |         | FOUT |            |         |               |

| R10~R13 | R10~R13 ( HIGH出力 )    |         |      |            |         |               |

| R20~R23 | R20~R23 ( HIGH出力 )    |         |      |            |         |               |

| P00~P03 | P00~P03 ( 入力&プルアップ )  |         |      |            |         |               |

| P10     | P10 ( 入力&プルアップ* )     |         |      | SIN(I)     | SIN(I)  |               |

| P11     | P11 ( 入力&プルアップ* )     |         |      | SOUT(O)    | SOUT(O) |               |

| P12     | P12 ( 入力&プルアップ* )     |         |      | SCLK(O)    | SCLK(I) |               |

| P13     | P13 ( 入力&プルアップ* )     |         |      |            | SRDY(O) |               |

| P20~P23 | P20~P23 ( 入力&プルアップ* ) |         |      |            |         |               |

| P30~P33 | P30~P33 ( 入力&プルアップ* ) |         |      |            |         |               |

| P40     | P40 ( 入力&プルアップ* )     |         |      |            |         | AD0(I)        |

| P41     | P41 ( 入力&プルアップ* )     |         |      |            |         | AD1(I)        |

| P42     | P42 ( 入力&プルアップ* )     |         |      |            |         | AD2(I)        |

| P43     | P43 ( 入力&プルアップ* )     |         |      |            |         | AD3(I)        |

\* マスクオプションにて"プルアップあり"選択時 ("プルアップなし"選択時はハイインピーダンス)

機能の設定方法については各周辺回路の説明を参照してください。

### 2.3 テスト端子( TEST )

ICの出荷検査時に使用する端子です。通常動作時はTESTをVDDに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C63158はCPU部分に4ビットコアCPU S1C63000を使用しています。

S1C63000については"S1C63000コアCPUマニュアル"を参照してください。

注: S1C63158においては、SLEEP動作を想定していないため、SLP命令は使用できません。

### 3.2 コードROM

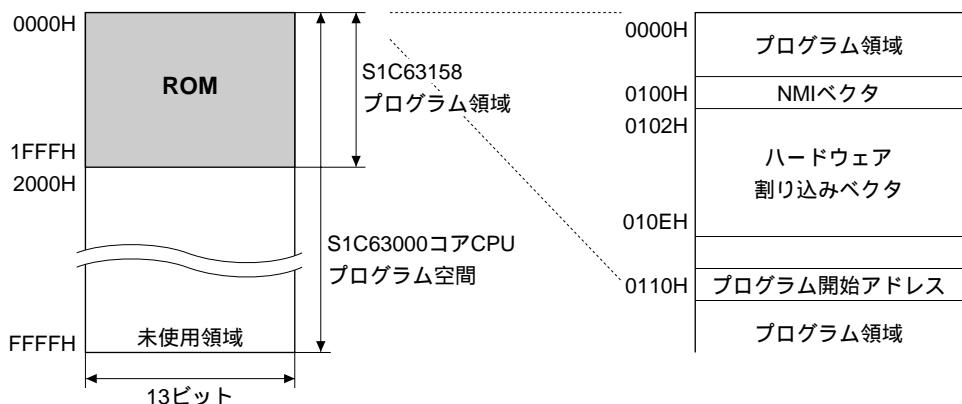

内蔵コードROMはプログラム格納用のマスクROMで、8,192ステップ×13ビットの容量があります。コアCPUのプログラム領域は0000H～FFFFHステップまでリニアにアクセス可能ですが、S1C63158では、このうち0000H～1FFFHステップがプログラム領域となります。イニシャルリセット後のプログラム開始番地が0110Hステップ、ノンマスカブル割り込み(NMI)ベクタが0100H、ハードウェア割り込みベクタが0102H～010EHステップに割り当てられています。

図3.2.1 コードROMの構成

### 3.3 RAM

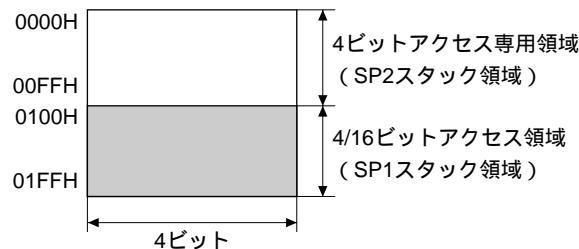

RAMは種々のデータを格納するデータメモリで、512ワード×4ビットの容量があります。

RAM領域は、データメモリマップ上のアドレス0000H～01FFHに割り当てられています。

この中でアドレス0100H～01FFHが4ビット/16ビットデータアクセスが可能な領域、その他の領域は4ビットデータアクセスのみ可能な領域となっています。

プログラミングの際には以下の点に注意してください。

(1)データメモリの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データ領域とスタック領域が重ならないように注意してください。

(2)S1C63000コアCPUは、4ビットデータ用スタックポインタ(SP2)および16ビットデータ用スタックポインタ(SP1)によりスタック処理を行います。SP1によるスタック処理では16ビットデータアクセスが行われますので、このスタック領域の設定は4ビット/16ビットアクセスが可能な領域内(0100H～01FFH)で行ってください。スタックポインタは、SP1が0000H～03FFH、SP2が0000H～00FFHの範囲でサイクリックに動作します。このため、SP1はS1C63158の4ビット/16ビットアクセス領域を外れた0200H以上、あるいは00FFH以下の中にも設定される可能性がありますので注意してください。SP1によるスタック操作以外のメモリアクセスは4ビットデータアクセスとなります。

また、イニシャルリセット時は、スタックポインタSP1、SP2の両方がソフトウェアで設定されるまでNMIを含むすべての割り込みがマスクされます。また、SP1、SP2を設定後どちらか一方を再設定すると、もう一方が再設定されるまでNMIを含む割り込みは再びマスクされます。したがって、SP1およびSP2の設定は必ずペアで行ってください。

(3) サブルーチンコールでは16ビットデータ用スタック(SP1)を4ワード(PCの退避)消費します。

割り込みでは16ビットデータ用スタックエリアを4ワード(PCの退避)4ビットデータ用スタックエリアを1ワード(Fレジスタの退避)消費します。

図3.3.1 データRAMの構成

## 4 周辺回路と動作

S1C63158の周辺回路( タイマ、A/D、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

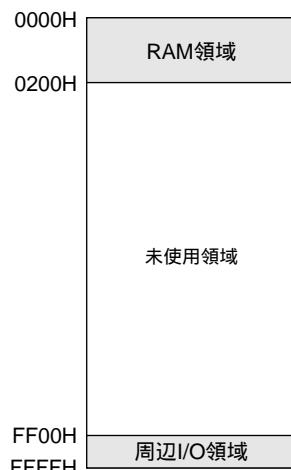

### 4.1 メモリマップ

S1C63158のデータメモリは512ワードのRAM、73ワードの周辺I/Oメモリ領域で構成されます。図4.1.1にS1C63158の全体のメモリマップ、表4.1.1( a )~( f )に周辺回路( I/O空間 )のメモリマップを示します。

図4.1.1 メモリマップ

注: メモリマップの未使用領域にはメモリが実装されていません。また、周辺I/O領域にも非実装領域、未使用( アクセス禁止 )領域が存在します。これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

周辺I/O領域については表4.1.1( a )~( f )に示すI/Oメモリマップを参照してください。

表4.1.1(a) I/Oメモリマップ(FF00H ~ FF28H)

| アドレス  | レジスタ   |       |       |       | Name                             | Init *1                      | 1                                    | 0                                        | 注 釈                                                                                                                                                                         |

|-------|--------|-------|-------|-------|----------------------------------|------------------------------|--------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | D3     | D2    | D1    | D0    |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF00H | CLKCHG | OSCC  | 0     | VDC   | CLKCHG<br>OSCC                   | 0                            | OSC3<br>On                           | OSC1<br>Off                              | CPUクロック切り換え<br>OSC3発振On/Off                                                                                                                                                 |

|       | R/W    |       | R     | R/W   | 0 *3<br>VDC                      | - *2                         | 2.1V                                 | 1.3V                                     | 未使用<br>CPU動作電圧切り換え(1.3V: OSC1, 2.1V: OSC3)                                                                                                                                  |

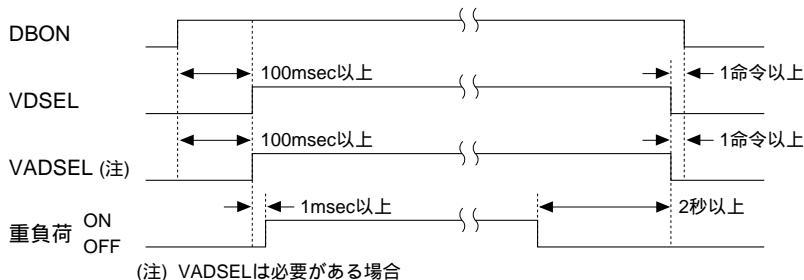

| FF01H | VADSEL | VDSEL | 0     | DBON  | VADSEL<br>VDSEL                  | 0                            | Vc2<br>Vc2                           | VDD<br>VDD                               | A/D変換器用電源選択<br>発振系定電圧回路用電源選択                                                                                                                                                |

|       | R/W    |       | R     | R/W   | 0 *3<br>DBON                     | - *2                         | On                                   | Off                                      | 未使用<br>昇圧回路On/Off                                                                                                                                                           |

| FF04H | SVDS3  | SVDS2 | SVDS1 | SVDS0 | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0 | 0<br>0<br>0<br>0             |                                      |                                          | SVD比較電圧設定<br>[SVDS3-0] 0 1 2 3 4 5 6 7<br>電圧(V) 1.05 1.10 1.15 1.20 1.25 1.30 1.40 1.60<br>[SVDS3-0] 8 9 10 11 12 13 14 15<br>電圧(V) 1.95 2.00 2.05 2.10 2.20 2.30 2.50 2.60 |

|       | R/W    |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF05H | 0      | 0     | SVDDT | SVDON | 0 *3<br>0 *3                     | - *2<br>- *2                 |                                      |                                          | 未使用<br>未使用                                                                                                                                                                  |

|       | R      |       | R/W   |       | SVDDT<br>SVDON                   | 0<br>0                       | Low<br>On                            | Normal<br>Off                            | SVD検出データ<br>SVD回路On/Off                                                                                                                                                     |

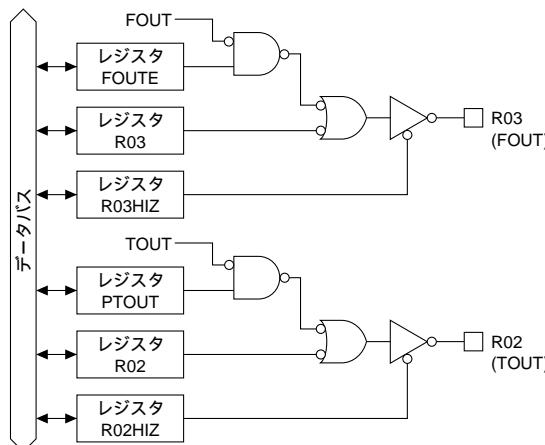

| FF06H | FOUTE  | 0     | FOFQ1 | FOFQ0 | FOUTE<br>0 *3                    | 0<br>- *2                    | Enable                               | Disable                                  | FOUT出力イネーブル<br>未使用                                                                                                                                                          |

|       | R/W    | R     | R/W   |       | FOFQ1<br>FOFQ0                   | 0<br>0                       |                                      |                                          | [FOFQ1, 0] 0 1 2 3<br>周波数選択 周波数 fosc1/64 fosc1/8 fosc1 fosc3                                                                                                                |

| FF07H | 0      | 0     | WDEN  | WDRST | 0 *3<br>0 *3                     | - *2<br>- *2                 |                                      |                                          | 未使用<br>未使用                                                                                                                                                                  |

|       | R      |       | R/W   | W     | WDEN<br>WDRST *3                 | 1<br>Reset                   | Enable<br>Reset                      | Disable<br>Invalid                       | ウォッチドッグタイマーニードル<br>ウォッチドッグタイマーセット(書き込み時)                                                                                                                                    |

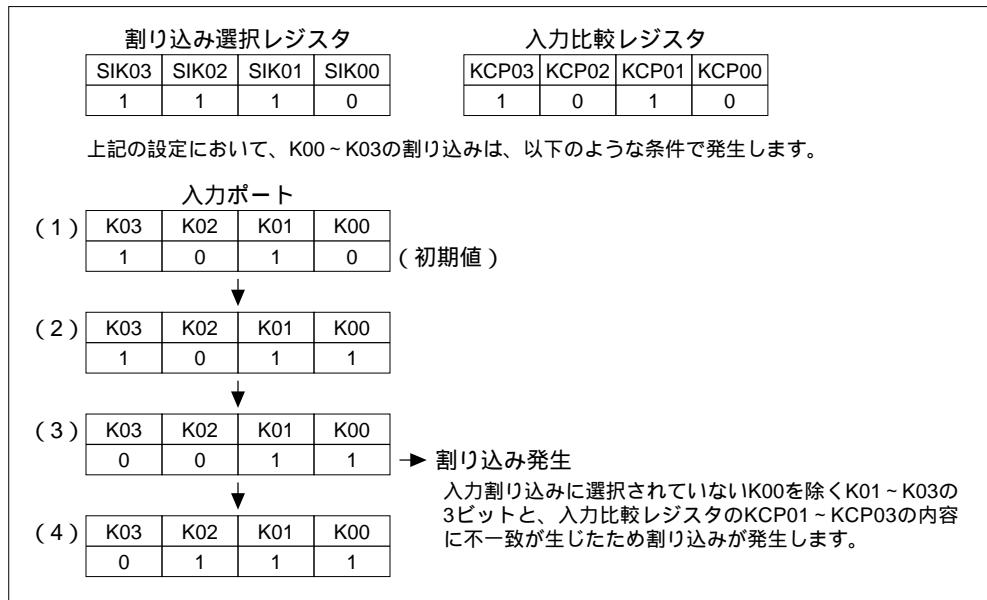

| FF20H | SIK03  | SIK02 | SIK01 | SIK00 | SIK03<br>SIK02<br>SIK01<br>SIK00 | 0<br>0<br>0<br>0             | Enable<br>Enable<br>Enable<br>Enable | Disable<br>Disable<br>Disable<br>Disable | K00 ~ K03割り込み選択レジスタ                                                                                                                                                         |

|       | R/W    |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF21H | K03    | K02   | K01   | K00   | K03<br>K02<br>K01<br>K00         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low                 | K00 ~ K03入力ポートデータ                                                                                                                                                           |

|       | R      |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF22H | KCP03  | KCP02 | KCP01 | KCP00 | KCP03<br>KCP02<br>KCP01<br>KCP00 | 1<br>1<br>1<br>1             |                                      |                                          | K00 ~ K03入力比較レジスタ                                                                                                                                                           |

|       | R/W    |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF24H | SIK13  | SIK12 | SIK11 | SIK10 | SIK13<br>SIK12<br>SIK11<br>SIK10 | 0<br>0<br>0<br>0             | Enable<br>Enable<br>Enable<br>Enable | Disable<br>Disable<br>Disable<br>Disable | K10 ~ K13割り込み選択レジスタ                                                                                                                                                         |

|       | R/W    |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF25H | K13    | K12   | K11   | K10   | K13<br>K12<br>K11<br>K10         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low                 | K10 ~ K13入力ポートデータ                                                                                                                                                           |

|       | R      |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

| FF26H | KCP13  | KCP12 | KCP11 | KCP10 | KCP13<br>KCP12<br>KCP11<br>KCP10 | 1<br>1<br>1<br>1             |                                      |                                          | K10 ~ K13入力比較レジスタ                                                                                                                                                           |

|       | R/W    |       |       |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

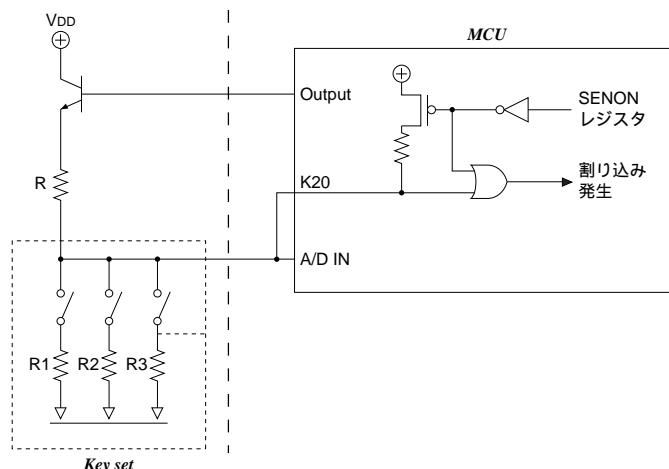

| FF28H | 0      | 0     | 0     | SIK20 | 0 *3<br>0 *3<br>0 *3<br>SIK20    | - *2<br>- *2<br>- *2<br>0    | Enable<br>Disable                    | 未使用<br>未使用<br>未使用<br>K20割り込み選択レジスタ       |                                                                                                                                                                             |

|       | R      |       | R/W   |       |                                  |                              |                                      |                                          |                                                                                                                                                                             |

## [ 注 釈 ]

\*1 イニシャルリセット時の初期値

\*2 回路上設定されない

\*3 読み出し時は常時"0"

表4.1.1( b ) I/Oメモリマップ( FF29H ~ FF44H )

| アドレス  | レジスタ   |        |        |        | Name   | Init *1 | 1      | 0                                                                                                                                                                  | 注釈                                                                                                                                                                                           |

|-------|--------|--------|--------|--------|--------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | D3     | D2     | D1     | D0     |        |         |        |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF29H | 0      | 0      | 0      | K20    | 0 *3   | - *2    | High   | Low                                                                                                                                                                | 未使用<br>未使用<br>未使用<br>K20入力ポートデータ                                                                                                                                                             |

|       | R      |        |        | K20    | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | 0      | 0      | 0      | KCP20  | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF2AH | R/W    |        |        | KCP20  | 0 *3   | - *2    | ↓      | ↓                                                                                                                                                                  | 未使用<br>未使用<br>未使用<br>K20入力比較レジスタ                                                                                                                                                             |

|       | 0      | 0      | 0      | SENON  | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | SENON  | 1      | On      |        |                                                                                                                                                                    |                                                                                                                                                                                              |

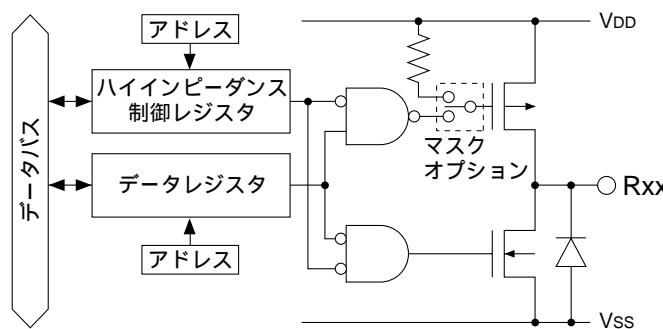

| FF2BH | R/W    |        |        | R03HIZ | 0      | High-Z  | Output | R03出力ハイインピーダンス制御( FOUTE=0 )<br>FOUT出力ハイインピーダンス制御( FOUTE=1 )<br>R02出力ハイインピーダンス制御( PTOUT=0 )<br>TOUT出力ハイインピーダンス制御( PTOUT=1 )<br>R01出力ハイインピーダンス制御<br>R00出力ハイインピーダンス制御 |                                                                                                                                                                                              |

|       | R03HIZ | R02HIZ | R01HIZ | R00HIZ | R02HIZ | 0       | High-Z |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R01HIZ | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R00HIZ | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF31H | R03    | R02    | R01    | R00    | R03    | 1       | High   | Low                                                                                                                                                                | R03出力ポートデータ( FOUTE=0 ) FOUT出力時は1に固定                                                                                                                                                          |

|       | R/W    |        |        | R02    | 1      | High    | Low    | R02出力ポートデータ( PTOUT=0 ) TOUT出力時は1に固定                                                                                                                                |                                                                                                                                                                                              |

|       | R01    | R01    | R01    | R00    | R01    | 1       | High   | Low                                                                                                                                                                | R01出力ポートデータ                                                                                                                                                                                  |

|       | R/W    |        |        | R00    | 1      | High    | Low    | R00出力ポートデータ                                                                                                                                                        |                                                                                                                                                                                              |

| FF32H | 0      | 0      | 0      | R1HIZ  | 0 *3   | - *2    | Output | 未使用<br>未使用<br>未使用<br>R1出力ハイインピーダンス制御                                                                                                                               |                                                                                                                                                                                              |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R1HIZ  | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R1HIZ  | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF33H | R13    | R12    | R11    | R10    | R13    | 1       | High   | Low                                                                                                                                                                | R10 ~ R13出力ポートデータ                                                                                                                                                                            |

|       | R/W    |        |        | R12    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R11    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R10    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF34H | 0      | 0      | 0      | R2HIZ  | 0 *3   | - *2    | Output | 未使用<br>未使用<br>未使用<br>R2出力ハイインピーダンス制御                                                                                                                               |                                                                                                                                                                                              |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R2HIZ  | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R2HIZ  | 0      | High-Z  |        |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF35H | R23    | R22    | R21    | R20    | R23    | 1       | High   | Low                                                                                                                                                                | R20 ~ R23出力ポートデータ                                                                                                                                                                            |

|       | R/W    |        |        | R22    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R21    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | R20    | 1      | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF40H | IOC03  | IOC02  | IOC01  | IOC00  | IOC03  | 0       | Output | Input                                                                                                                                                              | P00 ~ P03 I/O制御レジスタ                                                                                                                                                                          |

|       | R/W    |        |        | IOC02  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | IOC01  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | IOC00  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF41H | PUL03  | PUL02  | PUL01  | PUL00  | PUL03  | 1       | On     | Off                                                                                                                                                                | P00 ~ P03 プルアップ制御レジスタ                                                                                                                                                                        |

|       | R/W    |        |        | PUL02  | 1      | On      | Off    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | PUL01  | 1      | On      | Off    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | PUL00  | 1      | On      | Off    |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF42H | P03    | P02    | P01    | P00    | P03    | - *2    | High   | Low                                                                                                                                                                | P00 ~ P03入出力兼用ポートデータ                                                                                                                                                                         |

|       | R/W    |        |        | P02    | - *2   | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | P01    | - *2   | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | P00    | - *2   | High    | Low    |                                                                                                                                                                    |                                                                                                                                                                                              |

| FF44H | IOC13  | IOC12  | IOC11  | IOC10  | IOC13  | 0       | Output | Input                                                                                                                                                              | P13 I/O制御レジスタ<br>SIF(スレーブ)選択時、汎用レジスタとして機能<br>P12 I/O制御レジスタ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能<br>P11 I/O制御レジスタ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能<br>P10 I/O制御レジスタ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能 |

|       | R/W    |        |        | IOC12  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | IOC11  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

|       | R/W    |        |        | IOC10  | 0      | Output  | Input  |                                                                                                                                                                    |                                                                                                                                                                                              |

表4.1.1(c) I/Oメモリマップ( FF45H ~ FF51H )

| アドレス  | レジスタ  |       |       |       |       |         |        |       | 注 釈                                                                             |

|-------|-------|-------|-------|-------|-------|---------|--------|-------|---------------------------------------------------------------------------------|

|       | D3    | D2    | D1    | D0    | Name  | Init *1 | 1      | 0     |                                                                                 |

| FF45H | PUL13 | PUL12 | PUL11 | PUL10 | PUL13 | 1       | On     | Off   | P13ブルアップ制御レジスタ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                                      |

|       |       |       |       |       | PUL12 | 1       | On     | Off   | P12ブルアップ制御レジスタ(ESIF=0)<br>SIF(マスター)選択時、汎用レジスタとして機能                              |

|       |       |       |       |       | PUL11 | 1       | On     | Off   | SIF(スレーブ)選択時、SCLK(1)ブルアップ制御レジスタ<br>P11ブルアップ制御レジスタ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能 |

|       |       |       |       |       | PUL10 | 1       | On     | Off   | P10ブルアップ制御レジスタ(ESIF=0)<br>SIF選択時、SINブルアップ制御レジスタ                                 |

| FF46H | P13   | P12   | P11   | P10   | P13   | - *2    | High   | Low   | P13入出力兼用ポートデータ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                                      |

|       |       |       |       |       | P12   | - *2    | High   | Low   | P12入出力兼用ポートデータ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                                    |

|       |       |       |       |       | P11   | - *2    | High   | Low   | P11入出力兼用ポートデータ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                                    |

|       |       |       |       |       | P10   | - *2    | High   | Low   | P10入出力兼用ポートデータ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                                    |

| FF48H | IOC23 | IOC22 | IOC21 | IOC20 | IOC23 | 0       | Output | Input | P20～P23 I/O制御レジスタ                                                               |

|       |       |       |       |       | IOC22 | 0       | Output | Input |                                                                                 |

| FF49H | PUL23 | PUL22 | PUL21 | PUL20 | PUL23 | 1       | On     | Off   | P20～P23ブルアップ制御レジスタ                                                              |

|       |       |       |       |       | PUL22 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL21 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL20 | 1       | On     | Off   |                                                                                 |

| FF4AH | P23   | P22   | P21   | P20   | P23   | - *2    | High   | Low   | P20～P23入出力兼用ポートデータ                                                              |

|       |       |       |       |       | P22   | - *2    | High   | Low   |                                                                                 |

|       |       |       |       |       | P21   | - *2    | High   | Low   |                                                                                 |

|       |       |       |       |       | P20   | - *2    | High   | Low   |                                                                                 |

| FF4CH | IOC33 | IOC32 | IOC31 | IOC30 | IOC33 | 0       | Output | Input | P30～P33 I/O制御レジスタ                                                               |

|       |       |       |       |       | IOC32 | 0       | Output | Input |                                                                                 |

| FF4DH | PUL33 | PUL32 | PUL31 | PUL30 | PUL33 | 1       | On     | Off   | P30～P33ブルアップ制御レジスタ                                                              |

|       |       |       |       |       | PUL32 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL31 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL30 | 1       | On     | Off   |                                                                                 |

| FF4EH | P33   | P32   | P31   | P30   | P33   | - *2    | High   | Low   | P30～P33入出力兼用ポートデータ                                                              |

|       |       |       |       |       | P32   | - *2    | High   | Low   |                                                                                 |

|       |       |       |       |       | P31   | - *2    | High   | Low   |                                                                                 |

|       |       |       |       |       | P30   | - *2    | High   | Low   |                                                                                 |

| FF50H | IOC43 | IOC42 | IOC41 | IOC40 | IOC43 | 0       | Output | Input | P43 I/O制御レジスタ(PAD3=0)<br>A/Dイネーブル時、汎用レジスタとして機能                                  |

|       |       |       |       |       | IOC42 | 0       | Output | Input |                                                                                 |

|       |       |       |       |       | IOC41 | 0       | Output | Input |                                                                                 |

|       |       |       |       |       | IOC40 | 0       | Output | Input |                                                                                 |

| FF51H | PUL43 | PUL42 | PUL41 | PUL40 | PUL43 | 1       | On     | Off   | P43ブルアップ制御レジスタ(PAD3=0)<br>A/Dイネーブル時、汎用レジスタとして機能                                 |

|       |       |       |       |       | PUL42 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL41 | 1       | On     | Off   |                                                                                 |

|       |       |       |       |       | PUL40 | 1       | On     | Off   |                                                                                 |

表4.1.1( d ) I/Oメモリマップ( FF52H ~ FFC3H )

| アドレス  | レジスタ   |        |        |        | Name     | Init *1 | 1         | 0         | 注 釈                                               |

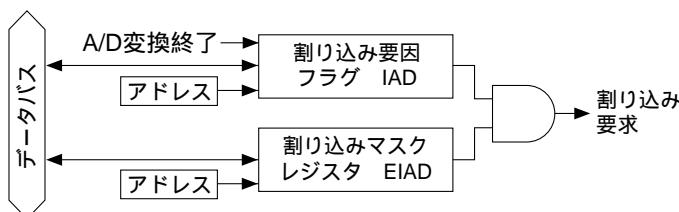

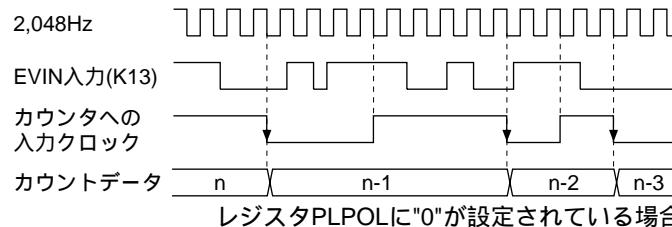

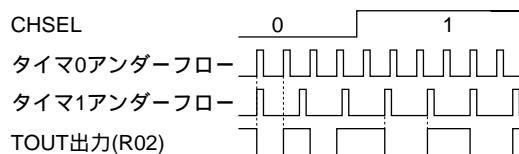

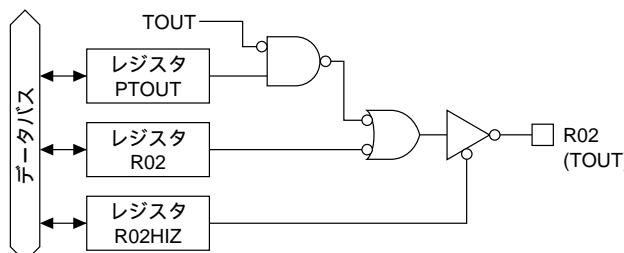

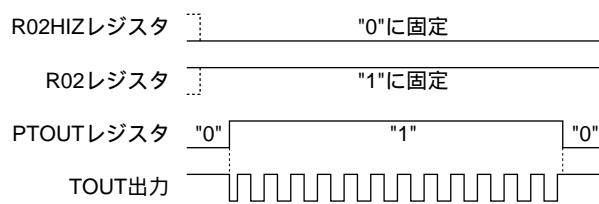

|-------|--------|--------|--------|--------|----------|---------|-----------|-----------|---------------------------------------------------|