**S1R72005/72015**

**On-The-Go デバイスコントローラ LSI

動作説明書**

本資料のご使用につきましては、次の点にご留意願います。

-

1. 本資料の内容については、予告無く変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性値の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## < 目次 >

|                                   |           |

|-----------------------------------|-----------|

| <b>1. はじめに .....</b>              | <b>1</b>  |

| <b>2. 用語 .....</b>                | <b>2</b>  |

| <b>3. ホスト機能 .....</b>             | <b>3</b>  |

| 3.1    VBUS制御 .....               | 3         |

| 3.2    HCステート制御 .....             | 4         |

| 3.2.1    リセット .....               | 5         |

| 3.2.2    オペレーション .....            | 5         |

| 3.2.3    サスPEND .....             | 5         |

| 3.2.4    リジューム .....              | 5         |

| 3.3    USB転送 .....                | 6         |

| 3.3.1    転送動作概略 .....             | 6         |

| 3.3.2    転送動作手順 .....             | 7         |

| 3.3.3    FIFOアクセス .....           | 11        |

| 3.3.4    自動コントロール転送（オートモード） ..... | 16        |

| 3.3.5    フレーム番号 .....             | 17        |

| 3.4    リモートウェイクアップ検出 .....        | 18        |

| <b>4. ペリフェラル機能 .....</b>          | <b>19</b> |

| 4.1    接続・切断検出 .....              | 19        |

| 4.2    USB転送 .....                | 20        |

| 4.2.1    転送動作概略 .....             | 20        |

| 4.2.2    転送動作手順 .....             | 21        |

| 4.2.3    FIFOアクセス .....           | 23        |

| 4.3    デバイスアドレスの設定 .....          | 26        |

| 4.4    エンドポイントのイネーブル／ディセーブル ..... | 27        |

| 4.5    ハンドシェーク制御 .....            | 28        |

| 4.6    SETUPトランザクション受信時の動作 .....  | 29        |

| 4.7    サスPEND .....               | 30        |

| 4.8    サスPEND復帰 .....             | 31        |

| 4.8.1    リモートウェイクアップ送出 .....      | 32        |

| 4.8.2    リジューム／リセット受信 .....       | 33        |

| 4.9    USBリセット .....              | 34        |

| <b>5. OTG制御 .....</b>             | <b>35</b> |

| 5.1    割り込み .....                 | 36        |

| 5.1.1    割り込みの種類 .....            | 36        |

| 5.1.2    OTGステートと割り込み .....       | 37        |

| 5.2    OTGデュアルロールデバイスの場合の制御 ..... | 38        |

| 5.2.1    遷移トリガー一覧 .....           | 38        |

|                                             |           |

|---------------------------------------------|-----------|

| 5.2.2 SPR .....                             | 44        |

| 5.3 ホストオンリーデバイスの場合の制御（＝ルートハブ制御） .....       | 46        |

| 5.3.1 常にVBUSをONとする場合 .....                  | 46        |

| 5.3.2 状況に応じVBUSをOFFする場合 .....               | 47        |

| 5.4 ペリフェラルオンリーデバイスの場合の制御.....               | 48        |

| <b>6. 低消費電力制御 .....</b>                     | <b>49</b> |

| 6.1 内部クロック供給制御 .....                        | 49        |

| 6.2 内蔵コンパレータ .....                          | 49        |

| 6.3 OTGステート別制御方法 .....                      | 50        |

| <b>付録 1. FAQ.....</b>                       | <b>51</b> |

| <b>付録 2. クロック制御方法 .....</b>                 | <b>53</b> |

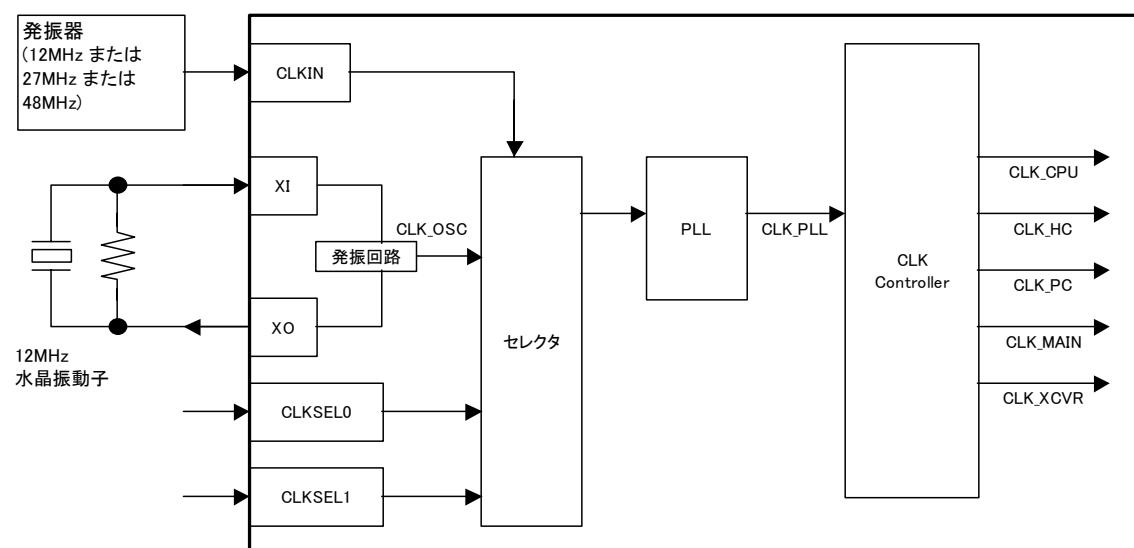

| 2.1 クロック概要 .....                            | 53        |

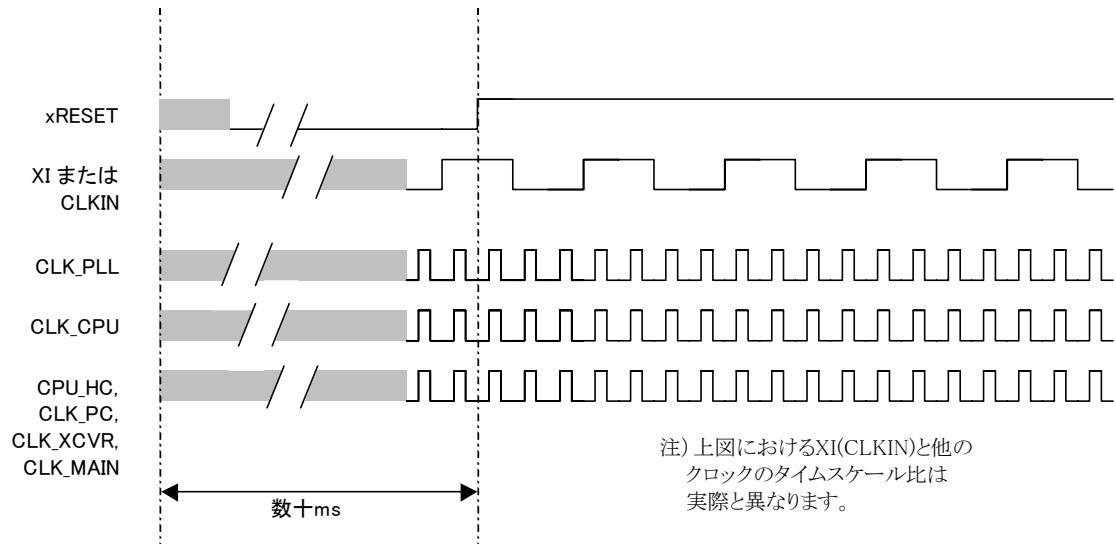

| 2.2 パワーオン後の状態 .....                         | 54        |

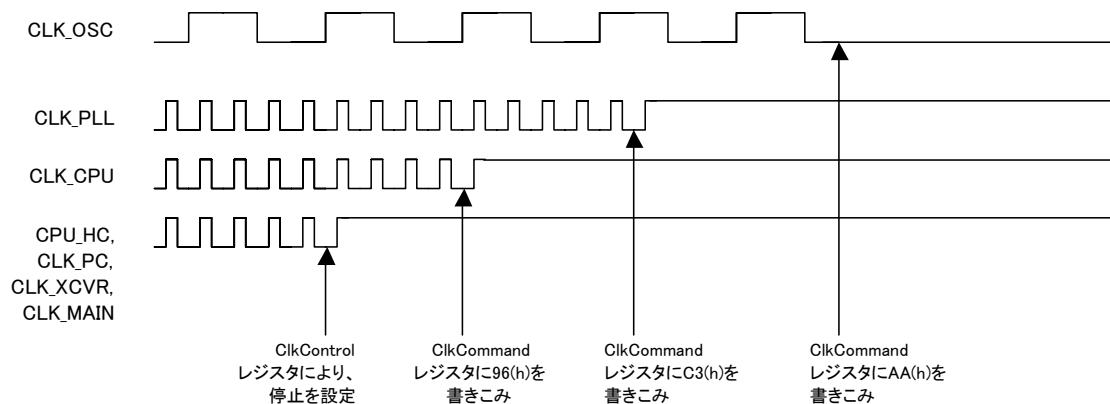

| 2.3 クロック停止方法 .....                          | 55        |

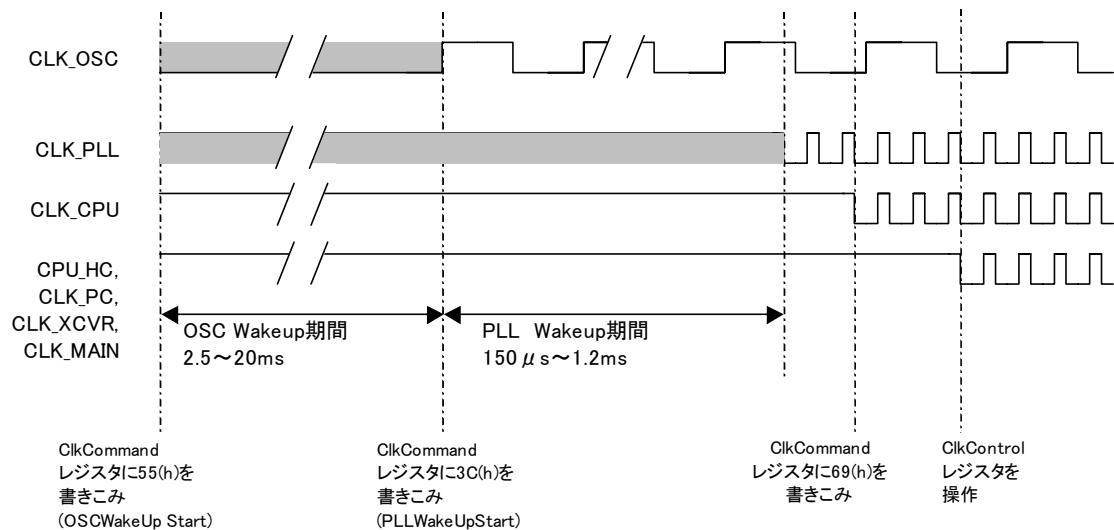

| 2.4 CPUからの制御によるクロック再開方法 .....               | 56        |

| 2.5 USBバスのステート検出によるクロックの再開について .....        | 57        |

| <b>付録 3. FIFO(パケットメモリ)制御方法 .....</b>        | <b>58</b> |

| 3.1 各Channel (EndPoint) に割り当てられるメモリ領域 ..... | 58        |

| 3.2 フロー制御及びFull / Empty .....               | 59        |

| <b>付録 4. DMAの概要 .....</b>                   | <b>61</b> |

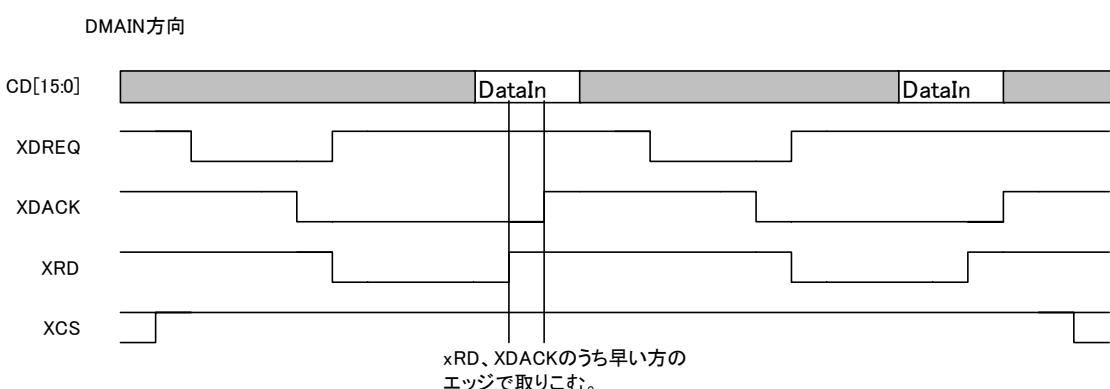

| 4.1 xRD, xWRストローブモード .....                  | 61        |

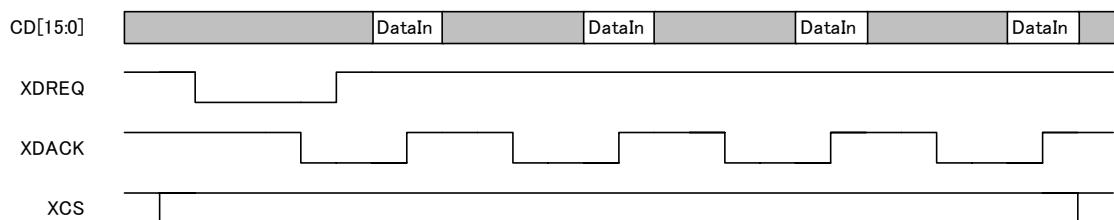

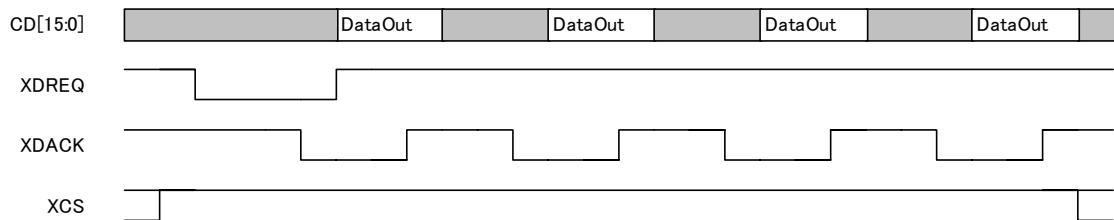

| 4.2 xDACKストローブモード .....                     | 62        |

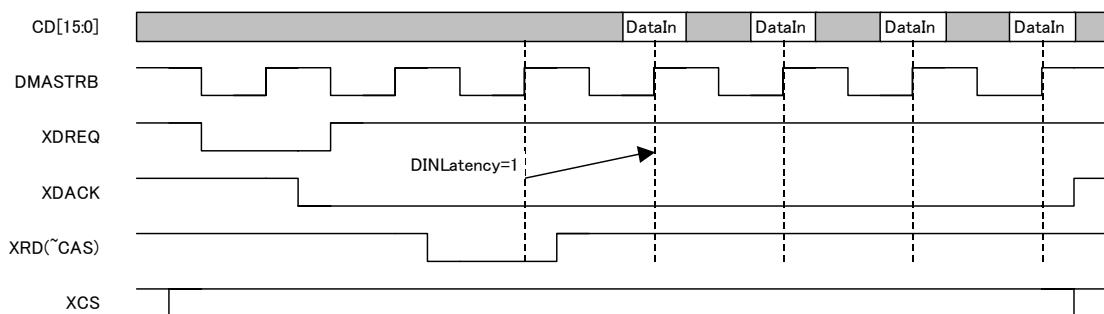

| 4.3 DMASTRB SDRAMモード .....                  | 63        |

| 4.4 DMASTRB 汎用モード .....                     | 64        |

| 4.5 DMA使用上の注意 .....                         | 65        |

| <b>改訂履歴 .....</b>                           | <b>66</b> |

### 1. はじめに

本ドキュメントは、S1R72005 および S1R72015(以下 72005/72015)の使用方法を提供するものです。

本ドキュメントをは、USB2.0 規格および On-The-Go(以下 OTG)規格の基本的な内容について理解されている方を対象として作成されています。

本ドキュメントは、以下の規格書をもとに作成されています。

- ▶ Universal Serial Bus Specification, Revision 2.0

- ▶ On-The-Go Supplement to the USB 2.0 Specification, Revision 1.0aRC5

※ 本ドキュメントの記載内容は、72005/72015 のドライバ S/W 作成における指標および推奨例であって、その使用方法を制限するものではありません。ただし、使用時の注意点等には従うことを推奨いたします。

※ 本ドキュメントに記載される内容は、USB 規格および OTG 規格に順ずることに留意していますが、認証を保証するものではありません。原則的には USB2.0 規格および OTG 規格の動作・内容に則って下さい。

※ 本ドキュメントの内容を予告なしに変更する場合があります。

## 2. 用語

---

### 2. 用語

本ドキュメント内における用語についての説明を Tab. 2-1 に示します。

Tab. 2-1 用語

| 語         | 意味                                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| xxxx.yyyy | xxxx レジスタの yyyy フィールドを示します。                                                                                                     |

| FIFO 領域   | 各転送チャネルに割り当てる LSI 内部のバッファ領域。                                                                                                    |

| HC        | 72005/72015 のホストコントローラ。                                                                                                         |

| PC        | 72005/72015 のペリフェラルコントローラ。                                                                                                      |

| チャネル      | ホスト時では USB 転送チャネル(パイプ)、ペリフェラル時ではエンドポイントをそれぞれ指します。                                                                               |

| デバイス      | 製品機器類。<br>【注意】<br>本ドキュメントでは、USB の接続トポジのスレーブを示す意味では用いていません。                                                                      |

| 転送サイズ     | PIPETotalSize_H～L.TotalSize レジスタフィールドに示す(示される)値。                                                                                |

| トータルサイズ   | “転送サイズ”と同義。                                                                                                                     |

| バッファ領域    | “FIFO 領域”と同義。                                                                                                                   |

| ペリフェラル    | USB の接続トポジにおけるスレーブを指します。<br>【注意】<br>本事項は、USB1.x／2.0 規格書では“デバイス”、OTG1.0 規格書では“ペリフェラル”とそれぞれ称されていますが、本ドキュメントでは“ペリフェラル”と統一することとします。 |

| ホスト       | USB の接続トポジにおけるマスタを指します。                                                                                                         |

なお、レジスタ名に関しては本ドキュメント内では全て 8 ビットアクセス時の名称を使用しています。

## 3. ホスト機能

72005/72015 が USB ホストとなった場合の動作について、主要機能別に解説します。

ホストの動作(HC ステート制御、USB 転送)が可能な OTG ステートコマンド(OTGCCControl.OTGStateCmd)は、“a\_host”または“b\_host”となります。ここで、“a\_host”はミニ A プラグが挿入される場合の通常のホストの場合で、“b\_host”は HNP によってアクティブとなったミニ B プラグが挿入されているホストの場合となります。これらの OTG ステートコマンド下でホスト機能に差異はありません。

### 3.1 VBUS 制御

ホスト時の VBUS 制御は、OTG ステート(OTGCCControl.OTGStateCmd)によって制御します。

VBUS が ON される OTG ステートは、“a\_wait\_vrise”、“a\_wait\_bcon”、“a\_host”、“a\_suspend”、“a\_peripheral”となります。それ以外のステートでは VBUS は OFF となります。VBUS が ON となるステートのうちホストコントローラが動作可能となるのは、“a\_host”、“a\_suspend”的みとなります。

※ 詳しくは本ドキュメント 5 章を参照下さい。

### 3. ホスト機能

#### 3.2 HC ステート制御

USB ホストは USB データラインのステート (HC ステート) を制御する必要があります。 HC ステートには次の 4 種類があります。

- ▶ リセット (SE0)

- ▶ オペレーションナル (SOF 出力状態; 転送可能状態)

- ▶ サスPEND (J 状態; アイドル)

- ▶ リジューム (K 状態)

これらの HC ステートは HCCControl.HCStateCmd レジスタフィールドに値を設定することで生成することができます。リセットとリジュームは S/W が時間管理を行います。また、ホスト動作可能状態 ("a\_host" または "b\_host") に OTG ステートを遷移した直後は、HC ステートはデフォルトのサスPEND状態となります。

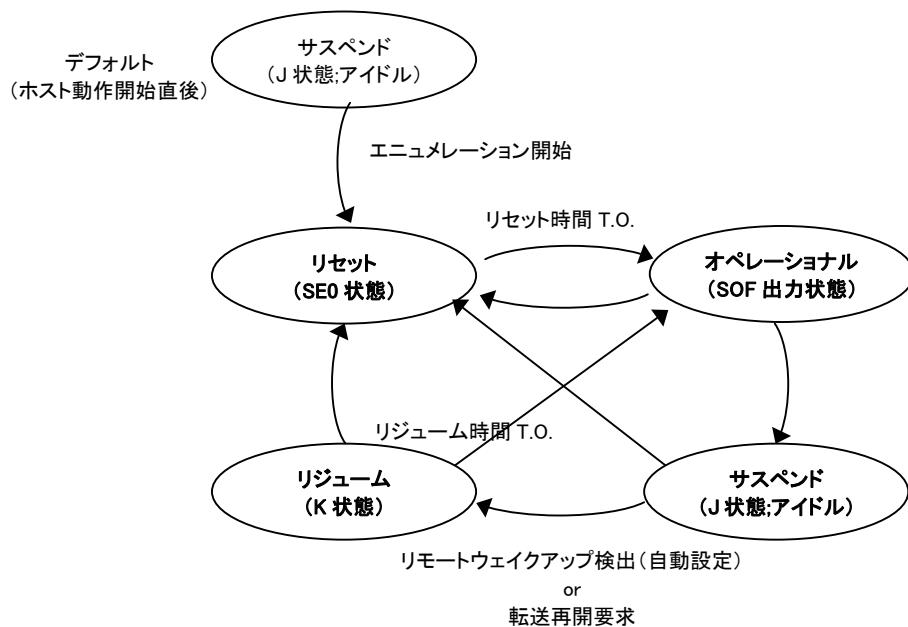

以下に HC ステート遷移を示します。

Fig. 3-1 HC ステート遷移

【注意】 OTGCControl.OTGStateCmd レジスタフィールドが "a\_host"、"a\_suspend"、"b\_host" 以外の場合では、 HCCControl.HCStateCmd レジスタフィールドに値を書き込むことはできません。

#### 3.2.1 リセット

USB 上にリセット信号(SE0)を出力します。リセット出力時間は最低 50ms とし(USB2.0 規格書 7.1.7.5)、S/W がその時間を管理します。

リセット完了後は HC ステートをオペレーションナルにします。

#### 3.2.2 オペレーションナル

USB 上に SOF を出力します。また、このステート下でのみ USB 転送が可能となります。USB 転送を行わない場合は HC ステートによりペリフェラルをサスペンドさせることもできます。

#### 3.2.3 サスペンド

USB のデータラインをアイドル(J 状態)に保ちます。

サスペンド状態からオペレーションナル状態に復帰させる場合は必ずリジュームステートまたはリセットステートを介して行ってください。なお、OTG ステートにおいて a\_host または b\_host に遷移直後は、HC ステートはサスペンド状態(デフォルト状態)でいることになります。

**【注意】** OTGCCControl.OTGStateCmd レジスタフィールドが“a\_host”、“a\_suspend”、“b\_host”からこれら以外の値に設定された場合は、HC ステートはデフォルト(サスペンド)の値に自動的にリセットされます。

#### 3.2.4 リジューム

USB 上にリジューム信号(K 状態)を出力します。リジューム時間は最低 20ms とし(USB2.0 規格書 7.1.7.7)、S/W がその時間を管理します。

リセット完了後は HC ステートをオペレーションナルにします。

**【注意】** リモートウェイクアップが検出された時は、HC ステート(HC ステート)は自動的にリジュームの値に設定されます。

### 3. ホスト機能

#### 3.3 USB 転送

72005/72015 のホスト時における USB 転送の方法を説明します。

##### 3.3.1 転送動作概略

72005/72015 は最大 6 つ(72005 は 5 つ)の USB 転送チャネルを持っています。1 つの転送チャネルは 1 つの USB 転送パイプに相当し、転送チャネル毎のレジスタ制御により転送を行います。

各転送チャネルはエンドポイント番号を任意に設定できます。よって、転送チャネルの設定をダイナミックに変更することでチャネル数以上のパイプ数を有する場合に対応することが可能となります。

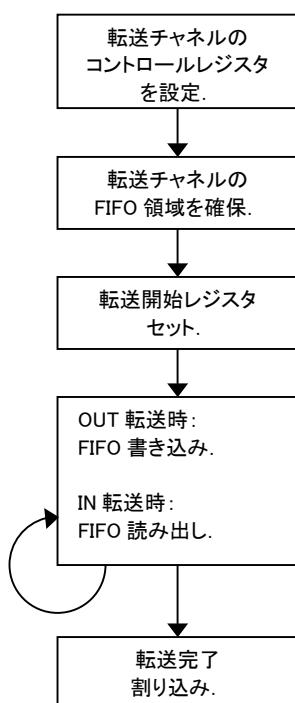

Fig. 3-2 に基本的な転送の流れを示します。

Fig. 3-2 ホスト転送の基本的な手順概略

USB 転送用のコントロールレジスタに適当な設定(ex.ファンクションアドレス、エンドポイント番号、転送種類、転送方向、転送サイズ等)を行い、転送開始レジスタビットをセットすることで転送を開始することができます。

OUT 転送の場合は、FIFO にデータペイロードを書き込むことにより USB 上にデータが出力されます。IN 転送の場合は、USB から受信したデータペイロードが FIFO に格納され、それを読み出すことによってデータを受け取ることができます。

転送開始時に指定した転送サイズ分の転送が完了すると、転送完了を示す割り込み要因がセットされます。この時、該当する割り込みを許可していれば、CPU に H/W 割り込みを通知することができます。

## 3.3.2 転送動作手順

ホスト時における転送の方法について解説します。基本的な操作の流れはOUT転送／IN転送とも同様となります。ただし、FIFOアクセスのタイミングや方法に多少の違いがありますが詳細は3.3.3に記述します。

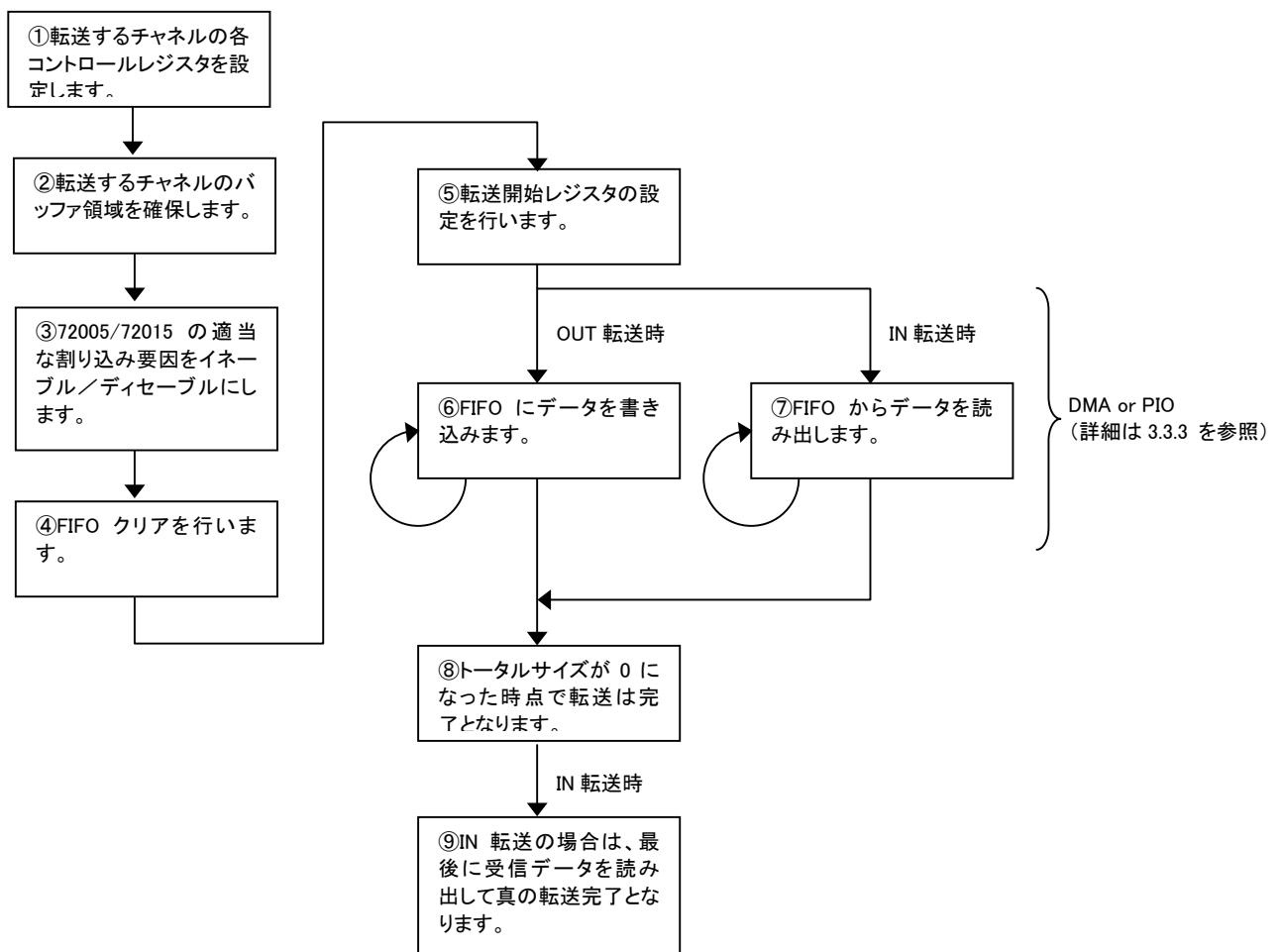

Fig. 3-3 に転送動作の手順を示します。

Fig. 3-3 USB 転送手順

次に各処理の詳細を記述します。(各項目の番号はFig. 3-3 の処理内の番号に対応しています。)

### 3. ホスト機能

---

① 転送するチャネルの各コントロールレジスタを設定します。

以下に示すレジスタの設定を行います。

Tab. 3-1 転送開始時のレジスタ設定(必須)

| 設定項目                       | 対応レジスタ・フィールド                                                                          | 条件        |

|----------------------------|---------------------------------------------------------------------------------------|-----------|

| DMA の使用有無                  | Config_0.JoinDMA                                                                      |           |

| 転送方向(OUT/IN/SETUP)         | Config_1.DirPID                                                                       |           |

| 転送種類(Control/Bulk/Int/Iso) | Config_1.TranType                                                                     | チャネル 0 以外 |

| エンドポイント番号                  | Config_1.EPNumber                                                                     |           |

| 連続転送回数                     | PIPETranConfig.Continuity                                                             |           |

| ファンクションアドレス                | PIPETranConfig.FuncAddr                                                               |           |

| トグル(初期値として 0)              | PIPEControl.Toggle                                                                    |           |

| 転送サイズ(トータルサイズ)             | PIPETotalSize_H.TotalSize,<br>PIPETotalSize_M.TotalSize,<br>PIPETotalSize_L.TotalSize |           |

また、必要に応じて以下の設定も行います。

Tab. 3-2 転送開始時のレジスタ設定(選択)

| 設定項目                       | 対応レジスタ・フィールド          | 条件         |

|----------------------------|-----------------------|------------|

| トグルモード                     | Config_0.ToggleMode   | インターラプト転送時 |

| ショートパケット終了のための 0 長パケット付与有無 | Config_0.AutoZeroLen  | OUT 転送時    |

| トークン発行フレーム間隔               | PIPEInterval.Interval | インターラプト転送時 |

【参考】 Tab. 3-1 および Tab. 3-2 の各設定項目について、その設定順序は問いません。

② 転送するチャネルのバッファ領域を確保します。

以下に示すレジスタの設定を行います。(方法はペリフェラル動作時と同様となります。)

Tab. 3-3 バッファ領域確保時のレジスタ設定

| 設定項目        | 対応レジスタ・フィールド                                        |

|-------------|-----------------------------------------------------|

| Max パケットサイズ | MaxPktSize_H.MaxPktSize,<br>MaxPktSize_L.MaxPktSize |

| バッファ領域面数    | MaxPktSize_H.BufferPage                             |

| バッファ領域確保実行  | PIPEEPCommon.SetBuffer                              |

Max パケットサイズとバッファ領域面数を設定後、PIPEEPCommon.SetBuffer レジスタビットに“1”をセットすることで、(Max パケットサイズ × バッファ領域面数)分のバッファ領域を確保します。

【注意】 Max パケットサイズやバッファ領域面数の設定を変更する場合、および SetBuffer を行う場合は、全てのチャネルの転送が停止している必要があります。

【注意】 全チャネルのバッファ領域サイズの総計が、FIFO の全領域サイズ(2.5k バイト)を超えない範囲で領域の確保を行う必要があります。

【注意】 SetBuffer を行うと、全チャネルのバッファ領域のデータがクリアされます。

③ 72005/72015 の適当な割り込み要因をイネーブル／ディセーブルにします。

必要に応じて該当する割り込みのイネーブルレジスタを設定します。

以下に、ホスト時に用いる割り込みを示します。各割り込み内容の詳細については、レジスタ詳細解説を確認ください。

Tab. 3-4 ホスト時使用割り込み

| カテゴリ           | 割り込み要因ビット名     | 内容                           | 備考                          |

|----------------|----------------|------------------------------|-----------------------------|

| 転送正常系          | TranCmp        | 指定サイズ転送完了                    | チャネル毎。                      |

|                | CTLTranCmp     | 自動コントロール転送完了                 | チャネル毎。詳細は後述。                |

|                | InShortRcv     | 予期せぬショートパケット受信               | チャネル毎。                      |

| 転送異常系          | NoResp         | デバイス無応答                      | チャネル毎。                      |

|                | Stalled        | デバイスストール応答                   | チャネル毎。                      |

|                | TranErr        | トランザクションエラー                  | チャネル毎。                      |

|                | InOverSize     | Max パケット超 受信                 | チャネル毎。                      |

|                | PortErr        | ポートエラー                       |                             |

| DMA 系          | DMACmp         | 指定サイズ DMA 完了                 | 詳細は後述。                      |

|                | DetFreezeDMA   | DMA サイズ残り有り、DMA 転送データ残 1 バイト | IN 転送で DMA 使用時必要。<br>詳細は後述。 |

| フレーム管理系        | SOF            | SOF 送出                       | フレーム管理しない場合は不要。             |

|                | FmNumberOver   | フレームナンバオーバフロー                | フレーム管理しない場合は不要。             |

| OTG 遷移(ルートハブ)系 | ChangeID       | ホスト側ケーブル挿抜検出                 |                             |

|                | ChangeConnStat | デバイス接続状態変化検出                 |                             |

|                | Cross44V       | VBUS 電圧変化検出                  |                             |

|                | DetRmtWkup     | リモートウェイクアップ検出                |                             |

| 間接参照           | MainIntStat_1  | MainIntStat_1 レジスタの間接参照      |                             |

|                | HCIntStat      | HCIntStat レジスタの間接参照          |                             |

|                | PIPEXIntStat   | PIPEXIntStat レジスタの間接参照       | チャネル毎。                      |

④ FIFO クリアを行います。

Config\_0.FIFOClr レジスタビットに“1”を設定して FIFO データをクリアします。

SetBuffer 直後であれば、これを行う必要はありませんが、一度転送を開始して、バッファの再構築なしに引き続き転送を開始する場合は必ず FIFO クリアを行ってください。

⑤ 転送開始レジスタの設定を行います。

PIPEControl.TranGo レジスタビットに“1”をセットすることで、ホストコントローラは転送レディ状態となります。この状態で FIFO にデータが存在する場合は、USB 上にデータが出力されることとなります。

**【参考】** ここで「FIFO にデータが存在する場合」とは、転送サイズ(トータルサイズ)が Max パケットサイズ以上の場合では少なくとも Max パケットサイズ相当量のデータが FIFO 内に存在することを指し、トータルサイズが Max パケットサイズ未満の場合ではトータルサイズ相当量のデータが FIFO 内に存在することを指します。

⑥ FIFO にデータを書き込みます。

FIFOへのデータの書き込みは、上記 ⑤を行う前に行っておいても構いません。転送開始以降のFIFOへのアクセスタイミング判断方法は大きく分けて 2 つあります。アクセス方法に関する詳細は 3.3.3 に記述します。

⑦ FIFO からデータを読み出します。

⑧ トータルサイズが 0 になった時点で転送は完了となります。

転送が完了すると TranCmp 割り込み要因がセットされ、TranGo ビットは“0”になります。各種エラー割り込み要因がセットさ

### 3. ホスト機能

---

れた場合も転送は停止されます。

⑨ IN 転送の場合は、最後に受信データを読み出して真の転送完了となります。

IN 転送の場合は、最終データを FIFO に受信した時点で TranCmp 要因がセットされるため、TranCmp 後にさらに FIFO 内のデータを全て読み出す必要があります。この読み出し完了をもって真の意味での転送完了と見なします。

### 3.3.3 FIFO アクセス

FIFO へのアクセス方法には、DMA と PIO アクセスの 2 種類があります。

DMA を用いる場合は、転送を開始させた後は、指定したサイズ分の転送が完了するまで CPU はその転送に全く関与せずに転送を完了することができます。

PIO アクセスで行う場合は、FIFO への書き込み、もしくは FIFO からの読み出しは PIO I/F レジスタのアクセスによって行う必要があります。

#### 3.3.3.1 PIO アクセス

##### 3.3.3.1.1 方法

FIFO アクセスを PIO アクセスで行う場合は、Tab. 3-5 に示すレジスタもしくはレジスタフィールドを設定・参照します。それぞれの詳しい内容はレジスタ詳細解説を確認下さい。

Tab. 3-5 PIO アクセスで使用するレジスタ

| 設定項目               | 対応レジスタ・フィールド                   | 説明                                                                 | 備考           |

|--------------------|--------------------------------|--------------------------------------------------------------------|--------------|

| PIO I/F            | FIFOforCPU_H/L                 | FIFO へのアクセスはこのレジスタで行います。                                           | 必須。          |

| 書き込みアクセスイネーブル      | FIFOControl_0.EnFIFOwr         | FIFOforCPU レジスタにライトする場合に設定します。                                     |              |

| 読み出しアクセスイネーブル      | FIFOControl_0.EnFIFOrd         | FIFOforCPU レジスタをリードする場合に設定します。                                     |              |

| バイトアクセス許可          | FIFOControl_0.EnIFOByteAccess  | 16 ビットアクセス時に末尾の 1 バイトをアクセスするような場合に設定します。                           | 必要に応じて参照/設定。 |

| FIFO エンプティ         | FIFOControl_0.Empty            | 該当チャネルの FIFO 領域が空の状態を示します。                                         |              |

| FIFO フル            | FIFOControl_0.Full             | 該当チャネルの FIFO 領域が満杯の状態を示します。                                        |              |

| FIFO 中のデータリメインカウンタ | FIFOControl_0/1.FIFODataRemain | OUT 転送の場合は FIFO 領域内の未転送データ残量、IN 転送の場合は FIFO 領域内の受信完了データ数をそれぞれ示します。 |              |

|                    |                                |                                                                    |              |

データを書き込む場合は、FIFOControl\_0.EnFIFOwr ビットをセットして FIFOforCPU\_H/L レジスタにデータをライトします。データを読み出す場合は、FIFOControl\_0.EnFIFOrd ビットをセットして FIFOforCPU\_H/L レジスタからデータをリードします。

FIFOforCPU\_H/L にアクセスすると、自動的に FIFO 内部のポインタが移動します。よって、このレジスタを任意の回数アクセスすることで、任意のサイズのデータの読み書きを行うことができます。

1 回の FIFO アクセス処理の最小単位は Max パケットサイズ(=1 面)とします。その面数は固定でも可変でも構いません。ただし 1 回の FIFO アクセスで複数面にアクセスする場合、アクセス面数が増大すると CPU の占有率もそれだけ長くなることになります。

ワードアクセス時にバイトデータを読み書きしたい場合は、EnIFOByteAccess ビットをセットして FIFOforCPU\_L レジスタにアクセスします。EnIFOByteAccess ビットをセットして FIFOforCPU\_L レジスタにアクセスした後は、必ず FIFOClr を行ってください。(下記注意参照)

基本的に EnIFOByteAccess ビットをセットしてアクセスする場合は、奇数データの最後の 1 バイトの読み書きする時のみとなります。

**【注意】** EnFIFOwr または EnFIFOrd ビットが設定されている場合に、不用意に FIFOforCPU\_H/L レジスタにアクセスすると FIFO 内部のポインタも不用意に移動することになり、データの整合が取れなくなることになるので注意が必要です。

### 3. ホスト機能

【注意】 8ビットアクセス時およびEnFIFOByteAccessビットをセットした場合では、FIFOforCPU\_Lレジスタのみにアクセスして下さい。FIFOforCPU\_Hレジスタにはアクセスしないで下さい。

【注意】 EnFIFOByteAccessビットをセットして FIFOforCPU\_Lレジスタにアクセスした場合、内部ポインタはバイトサイズ分しか移動しません。よって、その後そのまま FIFOへのアクセスおよびデータの USB送受信を行うと、データのワードバウンダリが保たれなくなります。そのため、EnFIFOByteAccessビットをセットして FIFOforCPU\_Lレジスタにアクセスした後は FIFOClrを行う必要があります。

FIFO領域に 1Max パケットサイズ以上のデータが存在するか(OUT転送)、1Max パケットサイズ以上の空きがある場合(IN転送)に、USB転送は行われます(ホストコントローラによりトークンが発行されます)。

#### 3.3.3.1.2 アクセスタイミングの取り方

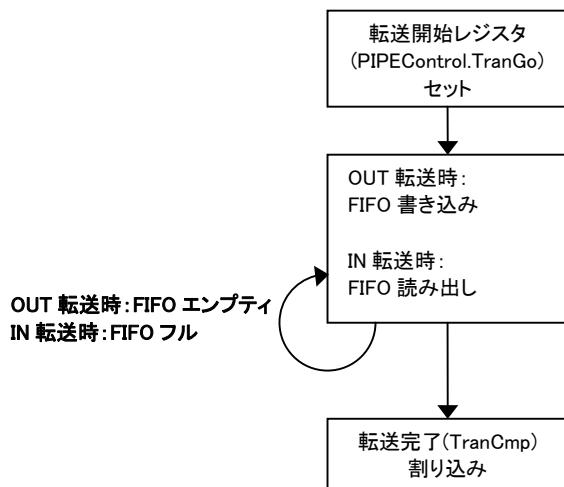

FIFOへのアクセスを PIOアクセスで行う場合、FIFOアクセスを開始するタイミングの取り方として次の二通り考えることができます。

##### (1) FIFO のフル／エンプティ、もしくは FIFO リメインカウンタをポーリングする方法

まず、転送トータルサイズに 1IRP サイズ(転送しようとする全データ数)を設定し、転送を行います。

転送開始後、OUT 転送の場合はエンプティ(FIFO エンプティビット=1 もしくは FIFO リメインカウンタ=0)、IN 転送の場合はフル(FIFO フルビット=1 もしくは FIFO リメインカウンタ=バッファ領域数)を判定することで、それぞれ FIFO にアクセスするタイミングを得る方法です。

FIFO リemainカウンタをポーリングする場合は、完全に FIFO がフル／エンプティになる前に FIFO にアクセスするタイミングを決めることが可能です。(バッファ領域を多面数確保時に有効です)

この方法は非 OS 環境でドライバを組み込む場合に有用です。

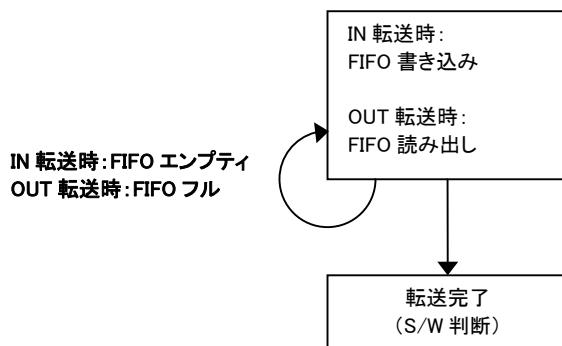

Fig. 3-4 FIFO アクセスタイミング (FIFO ポーリング)

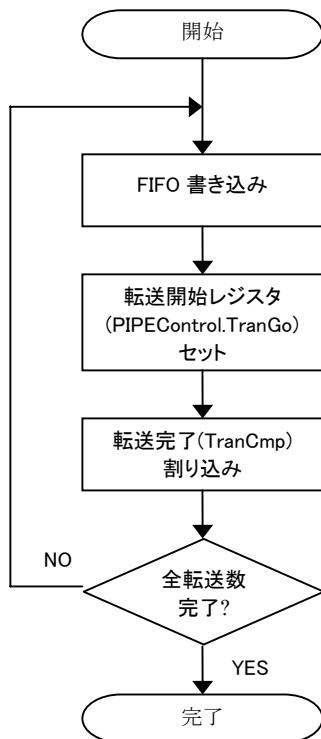

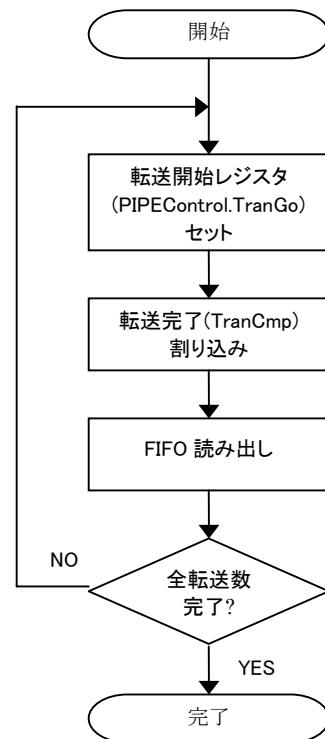

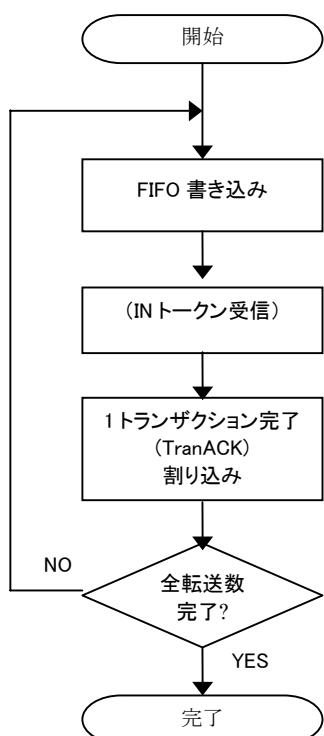

## (2) 転送完了割り込み(TranCmp 割り込み)による方法

アクセスしたいタイミング(転送数)毎に細切れに TranCmp 割り込みが上がるようになりますことで、FIFO アクセスのトリガを作り出す方法です。

転送トータルサイズは TranCmp 割り込みを上げたい転送数に設定します。全体の転送量(真のトータル転送量)は別途 S/W で管理するようにします。

TranCmp 割り込みの発生後、適当な FIFO アクセス処理を行い、なおも転送すべきデータがある場合は、再び適当な転送トータルサイズを設定して転送を開始させます。以降、全体の転送が終わるまでこれを繰り返します。

例えば、1 トランザクション毎に TranCmp 割り込みを上げたい場合は、転送トータルサイズを 1Max パケットサイズにすることで、1 トランザクション毎に割り込みを発生させることができます。

この場合よりも割り込み間隔をもう少し大きく取りたい場合は、バッファ領域数毎に TranCmp 割り込みを上げる(バッファページ数分のトランザクションで割り込みを上げる)方法があります。この場合、バッファ領域数が大きいと 1 回の FIFO 書き込み もしくは読み出し処理に、連続して CPU が割り当たる時間も増加することとなるので注意が必要です。

この方法は RTOS 環境下でドライバを組み込む場合に有用です。

Fig. 3-5 FIFO アクセスタイミング(割り込み; OUT 転送)

Fig. 3-6 FIFO アクセスタイミング(割り込み; IN 転送)

### 3. ホスト機能

---

#### 3.3.3.2 DMA

FIFOアクセスをDMAで行う場合は、Tab. 3-6 に示すレジスタもしくはレジスタフィールドを設定・参照します。それぞれの詳しい内容と動作説明はそれぞれレジスタ詳細解説、LSI動作説明を確認下さい。

Tab. 3-6 DMA で使用するレジスタ

|              | 設定項目                     | 対応レジスタ・フィールド                           | 説明                                                   |

|--------------|--------------------------|----------------------------------------|------------------------------------------------------|

| DMA<br>初期設定  | DMA バス幅                  | DMAConfig_1.DMABus8x16                 | DMA バス幅を指定します。                                       |

|              | ストローブモード                 | DMAConfig_1.StrobeMode                 | DMA 転送時の xRD/xWR 信号使用有無を指定します。                       |

|              | DMA エンディアン               | DMAConfig_1.DMAEndian                  | 16 ビット幅で DMA を行う時のエンディアンを指定します。                      |

|              | xDREQ 信号論理               | DMAConfig_1.DREQLevel                  | xDREQ 信号の論理を指定します。                                   |

|              | xDACK 信号による転送モード         | DMAConfig_1.DMATranMode                | xDACK 信号による DMA 転送方法を指定します。                          |

|              | DMASTRB 信号の位相反転有無        | DMAConfig_1.DMAClkPhase                | DMASTRB 信号の位相反転の有無を指定します。                            |

|              | DMA ハンドラ有無効設定            | DMAConfig_1.ActiveDMA                  | 72005/72015 の DMA ハンドラの有効/無効を指定します。                  |

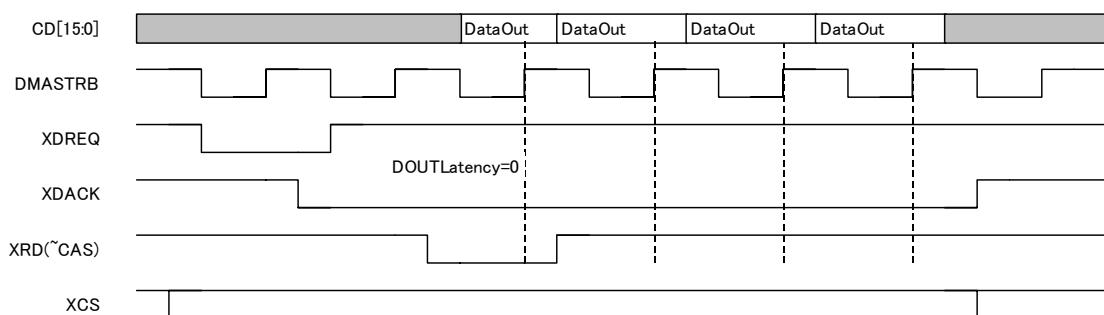

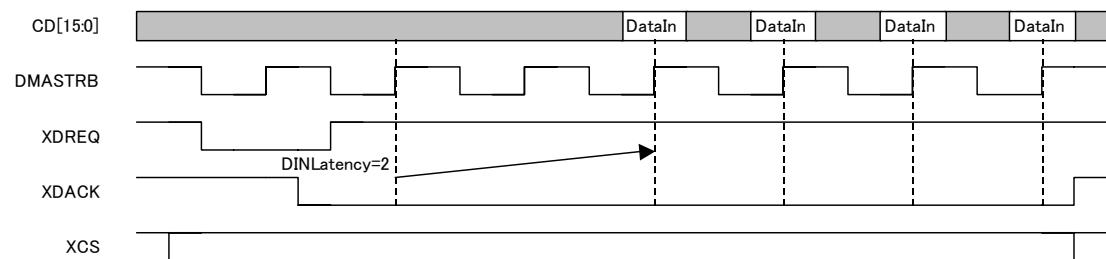

|              | DMA-IN レイテンシ             | DMAConfig_0.DINLatency                 | 外部メモリからのデータの取り込みタイミングを指定します。                         |

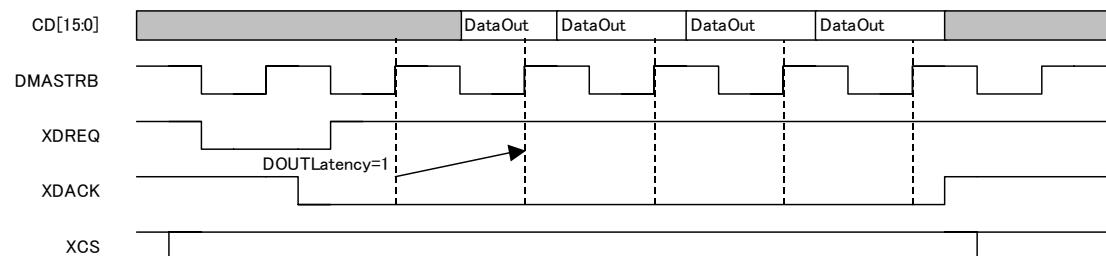

|              | DMA-OUT レイテンシ            | DMAConfig_0.DOUTLatency                | 外部メモリへのデータの出力タイミングを指定します。                            |

|              | DMA バースト長                | DMAControl_0.BurstLength               | DMA バースト転送時のバースト長を指定します。                             |

| 必要に応じて<br>参照 | DMA ハンドラローカル FIFO 残データ有無 | DMAControl_0.<br>BurstFIFORemain       | DMA バースト転送時における DMA ハンドラローカル FIFO 内の残データの有無を示します。    |

| DMA 実制御      | DMA 転送開始                 | DMAControl_1.DMAGo                     | DMA 転送の開始・停止を行います。                                   |

|              | DMA 転送強制中断               | DMAControl_1.DMAAbort                  | DMA 転送を強制中断します。通常は使用しません。                            |

|              | DMA カウンタ                 | DMACount_H<br>DMACount_M<br>DMACount_L | DMA 転送を行うサイズを指定します。<br>基本的には TotalSize と同様の値をセットします。 |

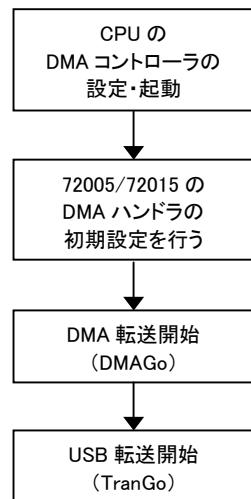

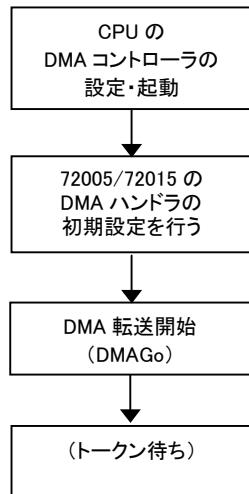

### 3.3.3.2.1 操作手順

DMA による FIFO への書き込み・読み出しへ次の手順で行います。

Fig. 3-7 DMA 転送開始手順

72005/72015 の DMA ハンドラの初期設定(一度でよい)と CPU の DMA コントローラの起動をそれぞれ行った後、DMA を開始します(DMAGo)。

DMAGo を設定する以前の 72005/72015 の DMA ハンドラの初期設定については、各項目の設定順序は問いません。

USB の帯域の有効活用の視点から USB 転送の開始前に予め DMA を起動しておくようにしますが、基本的には TranGo と DMAGo の順番が前後しても動作自体には支障はありません。

### 3.3.3.2.2 DMA 関連割り込み

DMA 転送が完了した時、その状況に応じて以下の割り込み要因がセットされます。

Tab. 3-7 DMA 割り込み

| 割り込み要因ビット名   | 内容          |

|--------------|-------------|

| DMACmp       | DMA 転送完了    |

| DetFreezeDMA | DMA 停止(ロック) |

#### (3) DMACmp

DMA カウンタ(DMACount\_H～L)が 0 になった場合にセットされます。また、DMA を停止した(DMAGo を 1 から 0 に設定した)場合で、その時点の DMA 転送が完結した時に DMACmp の要因がセットされます。

DMACmp 割り込み後は、必要に応じて CPU の DMA コントローラの停止処理を行います。

#### (4) DetFreezeDMA

DMA のバスサイズが 16 ビットでかつ IN 転送時に、奇数サイズの予期せぬショートパケットを受信した場合にセットされます。この割り込み要因が発生した場合、FIFO 内には最後の 1 バイトのデータが存在するので、PIO アクセスによりその 1 バイトのデータを読み出す必要があります。(読み出し方法は 3.3.3.1.1 を参照して下さい)

また、DetFreezeDMA の要因がセットされた時は DMAGo は 1 にセットされたままなので、0 にクリアします(この時 DMACmp の要因が立ちます)。必要に応じて CPU の DMA コントローラの停止処理を行います。

**【注意】 DetFreezeDMA 割り込み要因は、DMAGo をクリアするか、FIFO から 1 バイトデータの読み出しを行うまでクリアで**

### 3. ホスト機能

きません。(割り込みハンドラ内にて EnDetFreezeDMA ビットをクリアすることで、DetFreezeDMA 割り込みのアサートをブロックすることができます。)

DMA を使用している 72005/72015 の USB 転送チャネルの USB 転送が、異常系の終了 (Stalled, NoResp, TranErr, InOverSize) で終わった場合、DMA ハンドラは起動されたままとなっているので、DMA Go を 0 に設定し必要に応じて CPU の DMA コントローラの停止処理を行います。

#### 3.3.4 自動コントロール転送（オートモード）

72005/72015 のホストコントローラは、USB のコントロール転送(セットアップステージ～(データステージ)～ステータスステージ)を自動的に完結する機能があります。この機能を“オートモード”と呼びます。オートモードは、チャネル 0 のみ有しています。

オートモード機能を ON にし、データステージ有無、8 バイトのセットアップコマンドレジスタにリクエストコマンドを設定して、転送を開始 (TranGo) すれば、自動的にセットアップステージ～(データステージ)～ステータスステージが行われます。データステージがある場合は、データステージを有りとし、データステージの方向、セットアップコマンド、データステージのデータのトータルサイズをそれぞれ設定して TranGo します。

オートモードで転送を行う場合は、TranGo 前に必ずトグルを 0 にクリアしておくようにします。

**【注意】** オートモードで転送を開始する場合も、トグルレジスタに設定されているトグル値から転送が開始されます。従って、トグルは必ず 0 にクリアして転送を開始して下さい。

**【参考】** オートモードが ON の場合は、チャネル 0 の Config\_1.DirPID ビットの設定は無視されます。

Tab. 3-8 自動コントロール転送のレジスタ設定

| カテゴリ                  | 設定項目                     | 対応レジスタ・フィールド                                                                          | 条件           |

|-----------------------|--------------------------|---------------------------------------------------------------------------------------|--------------|

| オートモード関連              | 自動コントロール転送(オートモード)ON/OFF | PIPE0CTLAutoMode.EnCTLAuto                                                            |              |

|                       | データステージ有無                | PIPE0CTLAutoMode.NoDataStage                                                          |              |

|                       | データステージ方向                | PIPE0CTLAutoMode.DataStageDir                                                         | データステージ有りの場合 |

|                       | セットアップコマンドバッファ(8 バイト)    | PIPE0Setup_0～7                                                                        |              |

| 転送制御関連<br>(通常転送と同様)   | DMA の使用有無                | Config_0.JoinDMA                                                                      | データステージ有りの場合 |

|                       | エンドポイント番号                | Config_1.EPNumber                                                                     |              |

|                       | 連続転送回数                   | PIPETranConfig.Continuity                                                             |              |

|                       | ファンクションアドレス              | PIPETranConfig.FuncAddr                                                               |              |

|                       | トグル(初期値として 0)            | PIPEControl.Toggle                                                                    |              |

|                       | 転送サイズ(トータルサイズ)           | PIPETotalSize_H.TotalSize,<br>PIPETotalSize_M.TotalSize,<br>PIPETotalSize_L.TotalSize | データステージ有りの場合 |

| バッファ領域確保<br>(通常転送と同様) | Max パケットサイズ              | MaxPktSize_H.MaxPktSize,<br>MaxPktSize_L.MaxPktSize                                   | データステージ有りの場合 |

|                       | バッファ領域面数                 | MaxPktSize_H.BufferPage                                                               | データステージ有りの場合 |

|                       | バッファ領域確保実行               | PIPEPCommon.SetBuffer                                                                 | データステージ有りの場合 |

**【参考】** オートモードが OFF の場合は、オートモードに関わるその他のレジスタ(データステージ有無、データステージ方向、セットアップコマンドレジスタ)の設定は無視されます。

**【参考】** データステージの無い自動コントロール転送時は、チャネル 0 のバッファ領域確保の有無は問いません。

自動コントロール転送が正常にステータスステージを完了すると、CTLTranCmp 割り込み要因がセットされます。

途中、どのステージにおいても、NoResp, Stalled, TranErr, InOverSize の要因を検出した場合は、その時点で転送が停止され、該当の割り込み要因がセットされます。

データステージが有り方向が IN の場合、データステージで予期せぬショートパケットを受信(InShortRcv 要因)すると、自動的にステータスステージが実行され、それが完了すると最後に InShortRcv の割り込み要因がセットされます。この時は、CTLTranCmp 要因はセットされません。

(InShortRcv 要因がセットアップステージおよびステータスステージでセットされることとは、USB 規格上ありません。)

### 3.3.5 フレーム番号

アイソクロナス転送では、フレーム番号を意識して転送を行う場合があります。そういった場合には、SOF 割り込みやフレーム番号カウンタレジスタ(HCFmNumber\_H/L)を利用して転送を開始させます。

SOF 割り込みやフレーム番号レジスタによってフレーム番号を監視します。目的のフレーム番号より 1 少ないフレームの時に TranGo します。これは、TranGo のセットによる転送動作は実際には TranGo をセットした次のフレームから開始されるためです。

フレーム関連の割り込みとレジスタをそれぞれ以下に示します。

Tab. 3-9 フレーム関連のレジスタ

| 内容     | 対応レジスタビット                    |

|--------|------------------------------|

| フレーム番号 | HCFmNumber_H<br>HCFmNumber_L |

Tab. 3-10 フレーム関連の割り込み

| 割り込み要因ビット名   | 意味           | 内容                                |

|--------------|--------------|-----------------------------------|

| SOF          | SOF 送出       | SOF の送出が完了した時にセット。                |

| FmNumberOver | フレーム番号オーバフロー | フレーム番号が 0xFFFF→0x0000 に変化した時にセット。 |

### 3. ホスト機能

---

#### 3.4 リモートウェイクアップ検出

ペリフェラルがリモートウェイクアップをサポートしており、かつ SetFeature リクエストによってペリフェラルにリモートウェイクアップを許可している場合は、ホストはリモートウェイクアップに応答する必要があります。

リモートウェイクアップ関連のレジスタと割り込みをそれぞれ Tab. 3-11、Tab. 3-12 に示します。

Tab. 3-11 リモートウェイクアップ検出許可レジスタ

| 設定項目            | 対応レジスタビット                 |

|-----------------|---------------------------|

| リモートウェイクアップ検出許可 | OTGCCControl.AllowRmtWkup |

Tab. 3-12 リモートウェイクアップ検出割り込み

| 割り込み要因ビット名 | 意味            | 内容                          | 有効 OTG ステート<br>(括弧内 HC ステート)          |

|------------|---------------|-----------------------------|---------------------------------------|

| DetRmtWkup | リモートウェイクアップ検出 | ラインステートに 3us の K 状態を検出した場合。 | a_host(Suspend)<br>a_suspend(Suspend) |

リモートウェイクアップ検出の流れを以下に示します。

- ① 予め OTGCCControl.AllowRmtWkup ビットをセットして 72005/72015 のリモートウェイクアップ検出を有効にしておきます。

(リモートウェイクアップの検出は、HC ステートがサスPENDの時のみ行われます。)

- ② サスPENDステート中にウェイクアップ信号(K 状態)を検出すると、DetRmtWkup 割り込み要因がセットされます。

- ③ それと同時に、HC ステート(HCControl.HCStateCmd)が自動的にリジュームに設定されます。

- ④ DetRmtWkup 割り込み検出後、最低 20ms 経過後、S/W が HC ステートをオペレーションに復帰させます。

## 4. ペリフェラル機能

S1R72005/S1R72015 が USB ペリフェラルとなった場合の動作について、主要機能別に解説します。

ペリフェラルの動作(USB 転送)が可能な OTG ステートコマンド(OTGCCControl.OTGStateCmd)は、“b\_peripheral”または“a\_peripheral”となります。ここで、“b\_peripheral”はミニ B プラグが挿入される場合の通常のペリフェラルの場合で、“a\_peripheral”は HNP によってアクティブとなったミニ A プラグが挿入されているペリフェラルの場合となります。これら双方の OTG ステートコマンド下でペリフェラル機能に差異はありません。

### 4.1 接続・切断検出

ペリフェラルとしての通信相手(ホスト)の接続・切断の判断は、VBUS 電圧のモニタにより行います。VBUS 電圧が所定のしきい値を超えると接続とし、下回ると切断とみなします。

OTGCMonitor.Comp20V ビットの値が 1 であれば接続、0 であれば切断状態となります。

接続・切断判定に割り込みを用いる場合は、Cross44V の割り込み要因で判定します。Cross44V 割り込みが発生した時に Comp44V ビットが 1 であれば接続、0 であれば切断状態と判断できます。

※ 詳しくは本ドキュメント 5 章を参照下さい。

## 4. ペリフェラル機能

### 4.2 USB 転送

72005/72015 のペリフェラル時における USB 転送の方法を説明します。

#### 4.2.1 転送動作概略

72005/72015 は 1 つのコントロール転送専用エンドポイント(エンドポイント 0)と 6 つ(72005 は 5 つ)の汎用エンドポイントを持っています。

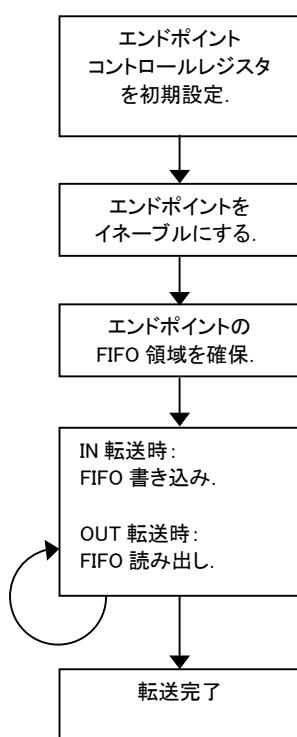

Fig. 4-1 に基本的な転送の流れを示します。

Fig. 4-1 ペリフェラル転送の基本的な手順概略

ペリフェラルが有する各エンドポイントディスクリプタの内容を 72005/72015 のエンドポイントコントロールレジスタに設定(ex.ファンクションアドレス、エンドポイント番号、転送種類、転送方向、転送サイズ等)し、エンドポイントを割り当てます。

転送開始レジスタビットをセットすることで転送を開始することができます。

OUT 転送の場合は、FIFO にデータペイロードを書き込むことにより USB 上にデータが出力されます。IN 転送の場合は、USB から受信したデータペイロードが FIFO に格納され、それを読み出すことによってデータを受け取ることができます。

転送開始時に指定した転送サイズ分の転送が完了すると、転送完了を示す割り込み要因がセットされます。この時、該当する割り込みを許可していれば、CPU に H/W 割り込みを通知することができます。

#### 4.2.2 転送動作手順

⑤ エンドポイントの各コントロールレジスタを設定します。(初期設定)

以下に示すレジスタの設定を行います。

Tab. 4-1 エンドポイントのレジスタ設定(必須)

| 設定項目                             | 対応レジスタ・フィールド                                                                                     |

|----------------------------------|--------------------------------------------------------------------------------------------------|

| DMA の使用有無                        | Config_0.JoinDMA                                                                                 |

| エンドポイントの方向(OUT/IN)               | Config_1.DirPID                                                                                  |

| エンドポイントの種類(Control/Bulk/Int/Iso) | Config_1.TranType                                                                                |

| エンドポイント番号                        | Config_1.EPNumber                                                                                |

| トグル(初期値として 0)                    | EPControl_1.ToggleClr<br>(以下エンドポイント 0 のみ)<br>EPControl_1.InToggleClr<br>EPControl_1.OutToggleClr |

また、必要に応じて以下の設定も行います。

Tab. 4-2 エンドポイントのレジスタ設定(選択)

| 設定項目                                             | 対応レジスタ・フィールド         |

|--------------------------------------------------|----------------------|

| トグルモード(インタラプトエンドポイント時)                           | Config_0.ToggleMode  |

| ショートパケット終了のための 0 長パケット付与有無(IN エンドポイント + DMA 使用時) | Config_0.AutoZeroLen |

【参考】 Tab. 4-1 および Tab. 4-2 の各設定項目について、その設定順序は問いません。

⑥ 各エンドポイントのバッファ領域を確保します。

以下に示すレジスタの設定を行います。(方法はホスト動作時と同様となります。)

Tab. 4-3 エンドポイントのバッファ領域確保時のレジスタ設定

| 設定項目        | 対応レジスタ・フィールド                                        |

|-------------|-----------------------------------------------------|

| Max パケットサイズ | MaxPktSize_H.MaxPktSize,<br>MaxPktSize_L.MaxPktSize |

| バッファ領域面数    | MaxPktSize_H.BufferPage                             |

| バッファ領域確保実行  | PIPEEPCommon.SetBuffer                              |

Max パケットサイズとバッファ領域面数を設定後、PIPEEPCommon.SetBuffer レジスタビットに“1”をセットすることで、(Max パケットサイズ × バッファ領域面数) 分のバッファ領域を確保します。

## 4. ペリフェラル機能

---

【注意】 Max パケットサイズやバッファ領域面数の設定を変更する場合、および SetBuffer を行う場合は、全てのエンドポイントの転送が停止している必要があります。

【注意】 全チャネルのバッファ領域サイズの総計が、FIFO の全領域サイズ(2.5k バイト)を超えない範囲で領域の確保を行う必要があります。

【注意】 SetBuffer を行うと、全チャネルのバッファ領域のデータがクリアされます。

### 4.2.3 FIFO アクセス

FIFO へのアクセス方法には、ホスト時同様、DMA と PIO アクセスの 2 種類があります。

DMA を用いる場合は、転送を開始させた後は、指定したサイズ分の転送が完了するまで CPU はその転送に全く関与せずに転送を完了することができます。

PIO アクセスで行う場合は、FIFO への書き込み、もしくは FIFO からの読み出しは PIO I/F レジスタのアクセスによって行う必要があります。

PIO アクセス・DMA ともにレジスタおよび使用方法はホストの場合と同様となります。ただし、PIO アクセスの場合において FIFO へのアクセスタイミングの取り方に多少の違いがあります。また、DMA ではペリフェラル用の割り込みがホスト時と比べて一つ追加されます。

#### 4.2.3.1 PIO アクセス

##### 4.2.3.1.1 方法

PIO アクセスは、レジスタとそれらの使用方法・注意点はホスト時と同様です。詳しくは 3.3.3.1.1 を参照して下さい。

FIFO 領域に 1Max パケットサイズ以上のデータが存在するか(IN エンドポイント)、1Max パケットサイズ以上の空きがある場合(OUT エンドポイント)に、該当するトーケンを受信すると USB 転送が自動的に行われます。

##### 4.2.3.1.2 アクセスタイミングの取り方

FIFO へのアクセスを PIO アクセスで行う場合、FIFO アクセスを開始するタイミングの取り方として次の二通り考えることができます。

###### (1) FIFO のフル／エンプティ、もしくは FIFO リメインカウンタをポーリングする方法

IN 転送の場合はエンプティ(FIFO エンプティビット=1 もしくは FIFO リメインカウンタ=0)で、OUT 転送の場合はフル(FIFO フルビット=1 もしくは FIFO リメインカウンタ=バッファ領域数)を判定することで、それぞれ FIFO にアクセスするタイミングを得る方法です。

FIFO リメインカウンタをポーリングする場合は、完全に FIFO がフル／エンプティになる前に FIFO にアクセスするタイミングを決めることも可能です。(バッファ領域を多面数確保時に有効です)

USB 転送数は S/W にて管理します。

この方法は非 OS 環境でドライバを組み込む場合に有用です。

Fig. 4-2 FIFO アクセスタイミング(FIFO ポーリング)

## 4. ペリフェラル機能

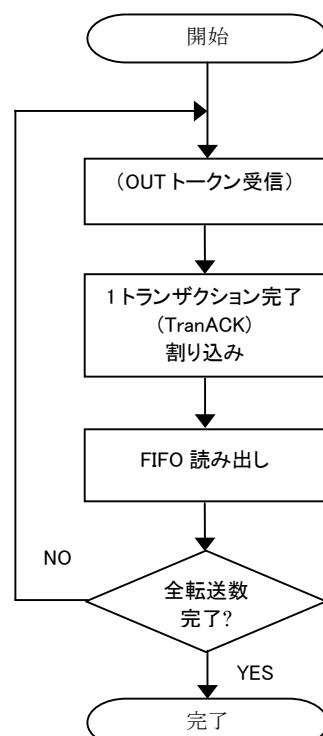

### (2) TranACK 割り込みと FIFO リメインカウンタによる方法

TranACK 割り込み(1 トランザクション完了割り込み)をトリガとして、FIFO にアクセスする方法です。

TranACK 割り込みが発生する最小の間隔は約 14us(Bulk, MPS:8byte)となります。よって全ての TranACK 割り込みを S/W で処理できるとは限りません。TranACK 割り込みの発生後、FIFO リメインカウンタ(FIFOControl\_0/1.FIFODataRemain)を参照して、FIFO にアクセスするサイズを決めます。1回の FIFO アクセス処理の最小単位は Max パケットサイズ(=1 面)とします。その面数は固定でも可変でも構いません。

トータルの転送数は S/W で管理します。

この方法は RTOS 環境下でドライバを組み込む場合に有用です。

Fig. 4-3 FIFO アクセスタイミング

(割り込み; IN 転送)

Fig. 4-4 FIFO アクセスタイミング

(割り込み; OUT 転送)

#### 4.2.3.2 DMA

FIFOアクセスをDMAで行う場合も、レジスタとそれらの使用方法・注意点はホスト時と同様です。詳しくは 3.3.3.1.1 を参照して下さい。

##### 4.2.3.2.1 操作手順

DMAによるFIFOへの書き込み・読み出しへ次の手順で行います。

Fig. 4-5 DMA 転送開始手順

72005/72015 の DMA ハンドラの初期設定(一度でよい)と CPU の DMA コントローラの起動をそれぞれ行った後、DMA を開始します(DMAGo)。

DMAGo を設定する以前の 72005/72015 の DMA ハンドラの初期設定については、各項目の設定順序は問いません。

#### 4.2.3.2.2 DMA 関連割り込み

DMA 転送が完了した時、その状況に応じて以下の割り込み要因がセットされます。

Tab. 4-4 DMA 割り込み

| 割り込み要因ビット名   | 内容                   | 備考        |

|--------------|----------------------|-----------|

| DMACmp       | DMA 転送完了             | (ホスト時と同様) |

| DetFreezeDMA | DMA 停止(ロック)          | (ホスト時と同様) |

| INTranCmp    | DMA を用いた USB-IN 転送完了 |           |

##### (3) DMACmp

(ホスト時と同様。)

DMA カウンタ(DMACount\_H~L)が 0 になった場合にセットされます。また、DMA を停止した(DMAGo を 1 から 0 に設定した)場合で、その時点の DMA 転送が完結した時に DMACmp の要因がセットされます。

DMACmp 割り込み後は、必要に応じて CPU の DMA コントローラの停止処理を行います。

## 4. ペリフェラル機能

---

### (4) DetFreezeDMA

(ホスト時と同様。)

DMA のバスサイズが 16 ビットでかつ IN 転送時に、奇数サイズの予期せぬショートパケットを受信した場合にセットされます。この割り込み要因が発生した場合、FIFO 内には最後の 1 バイトのデータが存在するので、PIO アクセスによりその 1 バイトのデータを読み出す必要があります。(読み出し方法は 3.3.3.1.1 を参照して下さい)

また、DetFreezeDMA の要因がセットされた時は DMAGo は 1 にセットされたままなので、0 にクリアします(この時 DMA Cmp の要因が立ちます)。その後、必要に応じて CPU の DMA コントローラの停止処理を行います。

**【注意】** DetFreezeDMA 割り込み要因は、DMAGo をクリアするか、FIFO から 1 バイトデータの読み出しを行うまでクリアできません。(割り込みハンドラ内にて EnDetFreezeDMA ビットをクリアすることで、DetFreezeDMA 割り込みのアサートをブロックすることができます。)

DMA を使用しているエンドポイントの USB 転送がエラー終了した場合(INTTranErr, OUTTranErr)、DMA ハンドラは起動されたままとなっているので、DMAGo を 0 に設定し必要に応じて CPU の DMA コントローラの停止処理を行います。

### (5) INTTranCmp

IN エンドポイントに DMA を使用している場合、DMA が完了し、FIFO 内のデータが全て USB 転送し終わり後にホストからの ACK を受信した場合に、この要因がセットされます。

INTTranCmp 要因のセット以前において、DMA が完了した時点で DMA Cmp 要因もセットされます。

### 4.2.3.2.3 IRP データの転送完了判断

ペリフェラル時の USB 転送サイズは基本的には S/W が管理することになりますが、DMA を用いる場合は、DMACount\_H～L にその役目を担わせることができます。従って、DMA 使用時は DMA の割り込みによって IRP データの転送完了を判断することができます。

IN 転送の場合は、最終データが FIFO に書き込まれ USB 上にデータが出力し終わりホストから ACK を受信した場合に、IRP データの転送完了となります。OUT 転送の場合は、最終データを USB 側から受信し FIFO からそれを読み出し終わって、IRP データの転送完了となります。以上のことから、以下のように DMA 使用時の IRP データ転送完了判断をまとめることができます。

- ▶ IN エンドポイントに DMA 使用時 → INTTranCmp で IRP データ転送完了

- ▶ OUT エンドポイントに DMA 使用時 → DMA Cmp で IRP データ転送完了

## 4.3 デバイスアドレスの設定

デバイスのアドレス設定は、以下のレジスタによって行います。

72005/72015 は設定できるデバイスアドレスは 1 つのみとなります。

Tab. 4-5 デバイスアドレス設定レジスタ

| 設定項目     | 対応レジスタ・フィールド |

|----------|--------------|

| デバイスアドレス | PCUSBAddress |

エニュメレーション前は必ず 0 に設定して下さい。

エニュメレーション時の SetAddress リクエストのステータスステージ完了直後に所定のアドレス値に設定します。

切断時に 0 に設定します。

**【注意】** 接続相手のホストによっては、ステータスステージ完了後すぐに次のトークンが発行される場合があるため、アドレスの設定は特に素早く行う必要があります。

#### 4.4 エンドポイントのイネーブル／ディセーブル

エンドポイントのイネーブル／ディセーブルの制御は、以下のレジスタによって行います。

なお、エンドポイント 0 は常にイネーブル状態である必要があるため、イネーブル制御ビットは持っていません。

Tab. 4-6 エンドポイントのイネーブル制御レジスタ

| 設定項目                                      | 対応レジスタ・フィールド           |

|-------------------------------------------|------------------------|

| エンドポイントイネーブル<br>(エンドポイント 0 を除く; ディセーブル不可) | EPControl_0.EnEndPoint |

エニュメレーションが完了するまでは、基本的には全ての汎用エンドポイントはディセーブルにします。

SetConfiguration または SetInterface リクエストによって選択されるエンドポイントのみイネーブルに設定します。

また、SetFeature リクエストで該当エンドポイントをイネーブルに、ClearFeature リクエストで該当エンドポイントをディセーブルにします。

切断時にディセーブルにします。

## 4. ペリフェラル機能

### 4.5 ハンドシェーク制御

72005/72015 は、OUT 転送時にトランザクションが正常に完了した場合に自動的に ACK を送信します。また、IN 転送時で FIFO がエンプティの場合と OUT 転送時で FIFO がフルの場合に自動的に NAK を送信します。

これら以外の場合のハンドシェーク制御は以下に示す制御ビットにより行います。

Tab. 4-7 ハンドシェーク制御ビット

| 重別    | ノジスタビット                                                                 | 幾能                                                                  |                                                                                       |

|-------|-------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| STALL | (汎用エンドポイントのみ)<br>EPControl_0.ForceSTALL                                 | 無条件に STALL 応答します。                                                   | 転送に応答できない、もしくは何かトラブルにより転送を継続できない場合等に使用します。                                            |

|       | (エンドポイント 0 のみ)<br>EPControl_0.InForceSTALL<br>EPControl_0.OutForceSTALL | 該当する方向のトーケンに対して STALL 応答します。(どちらの場合でも SETUP トランザクションには ACK 応答します)   | (同上)                                                                                  |

|       | EPCommon.AllForceSTALL                                                  | 全てのエンドポイントの ForceSTALL と In/OutForceSTALL ビットを 1 にします。              | 一度に ForceSTALL をセットしたい場合に使用します。                                                       |

| NAK   | (汎用エンドポイントのみ)<br>EPControl_0.ForceNAK                                   | 無条件に NAK 応答します。                                                     | S/W の転送準備が整っていない場合等に使用します。                                                            |

|       | (エンドポイント 0 のみ)<br>EPControl_0.InForceNAK<br>EPControl_0.OutForceNAK     | 該当する方向のトーケンに対して NAK 応答します。(どちらの場合でも SETUP トランザクションには ACK 応答します)     | (同上)                                                                                  |

|       | EPCommon.AllForceNAK                                                    | 全てのエンドポイントの ForceNAK と In/OutForceNAK ビットを 1 にします。                  | 一度に ForceNAK をセットしたい場合に使用します。                                                         |

|       | EPControl_0.AutoForceNAK                                                | 正常な 1 トランザクション完了時に同エンド ポイントの ForceNAK (In/OutForceNAK) ビットを 1 にします。 | 1 トランザクションずつ転送を保留したい場合に使用します。例えば、1 トランザクション毎に確実に S/W 処理を行いたい場合等に使用します。                |

|       | (汎用エンドポイントのみ)<br>EPControl_0.AutoForceNAKShort                          | OUT 転送時、最後に受信したパケットがショートパケットだった場合に、同エンドポイントの ForceNAK ビットを 1 にします。  | IRP データ毎にデータ受信を保留したい場合に使用します。例えば、1 つの IRP データの転送が完了したすぐ後に次の IRP データが送信されるような場合に使用します。 |

各制御ビットの優先度は以下の通りとなります。

高 (In/Out)ForceSTALL, AllForceSTALL > (In/Out)ForceNAK, AllForceNAK

高 AutoForceNAK > AutoForceNAKShort

低

低

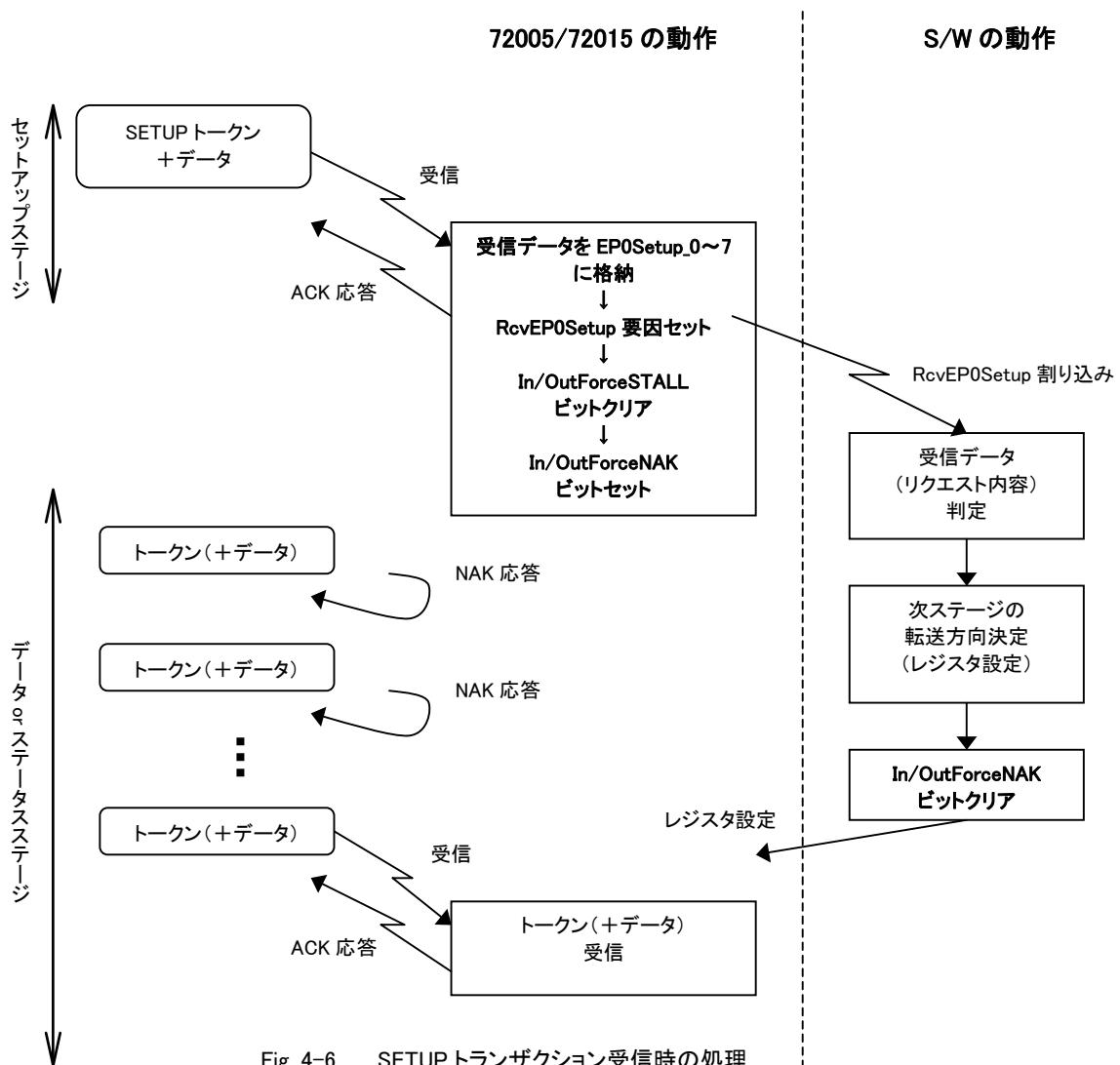

## 4.6 SETUP トランザクション受信時の動作

72005/72015 は、SETUP トーカンとそのデータを受信(セットアップステージを終了)すると、受信データを EP0Setup\_0~7 レジスタに格納し、RcvEP0Setup 割り込み要因がセットされます。

RcvEP0Setup 割り込み後、EP0Setup\_0~7 レジスタをリードすることによって受信したリクエストの内容を知ることができます。

また、RcvEP0Setup 割り込み要因のセットと同時に、In/OutForceSTALL ビットがクリアされ、In/OutForceNAK ビットが自動的にセットされます。

これにより、S/W が RcvEP0Setup 割り込み発生による処理を行っている間に次のステージのトーカンおよびデータが送信されてきても、ペリフェラルコントローラは即座に NAK 応答できることになります。

S/W のリクエスト解析等が終了した時点で In/OutForceNAK ビットをクリアすることで、次のステージのトーカンを受信しデータの送受信が可能となります。

Fig. 4-6 にSETUPトランザクション受信時の模式図を示します。

**【注意】** RcvEP0Setup 要因ビットが 1 である時に、In/OutForceNAK, In/OutForceSTALL ビットの値を変更しないで下さい。

**【注意】** In/OutForceNAK ビットが 1 であっても、SETUP トランザクションは無条件に受信されます。

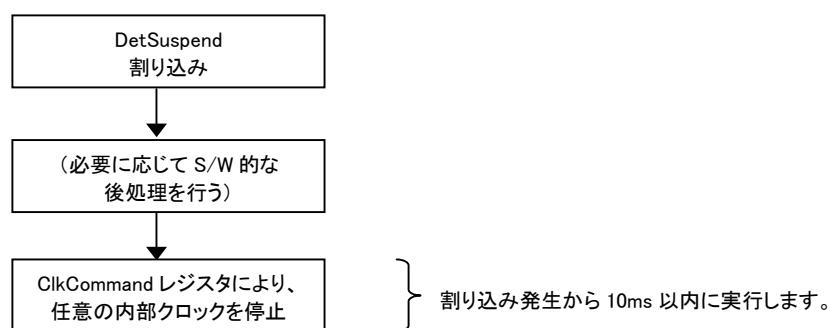

### 4.7 サスPEND

USB バスの状態が一定期間以上アイドル状態となった場合に、ペリフェラルはサスPENDする必要があります(→USB Specification Rev.2.0 – 7.1.7.6)。

サスPENDに入るトリガを DetSuspend 割り込み要因で判断します。

Tab. 4-8 サスPEND割り込み

| 割り込み要因ビット名 | 意味       | 内容                               | 有効 OTG ステート                  |

|------------|----------|----------------------------------|------------------------------|

| DetSuspend | サスPEND検出 | ラインステートに 5ms の J(アイドル)状態を検出した場合。 | b_peripheral<br>a_peripheral |

次にサスPENDの処理手順を記述します。

Fig. 4-7 デバイスサスPEND処理手順

**【注意】** サスPEND割り込みが発生した場合は、必ず ClkCommand レジスタにより何らかの内部クロックの停止を行ってください。そうしないと、以降サスPEND復帰のための割り込み(DetNonJ)が発生しない可能性があります。

**【注意】** サスPEND中(内部クロックを停止した状態)では、限られたレジスタのみアクセス可能です。(レジスタ内容説明参照)

**【参考】** クロック復帰後は、レジスタにはクロック停止以前の値が残っています。(モニタ関連レジスタ、割り込み要因を除く)

### 4.8 サスPEND復帰

サスPENDからの復帰要因として以下の 3つがあります。

- ▶ リモートウェイクアップ信号送出

- ▶ リジューム信号受信

- ▶ リセット信号受信

以下に復帰要因別に説明します。

## 4. ペリフェラル機能

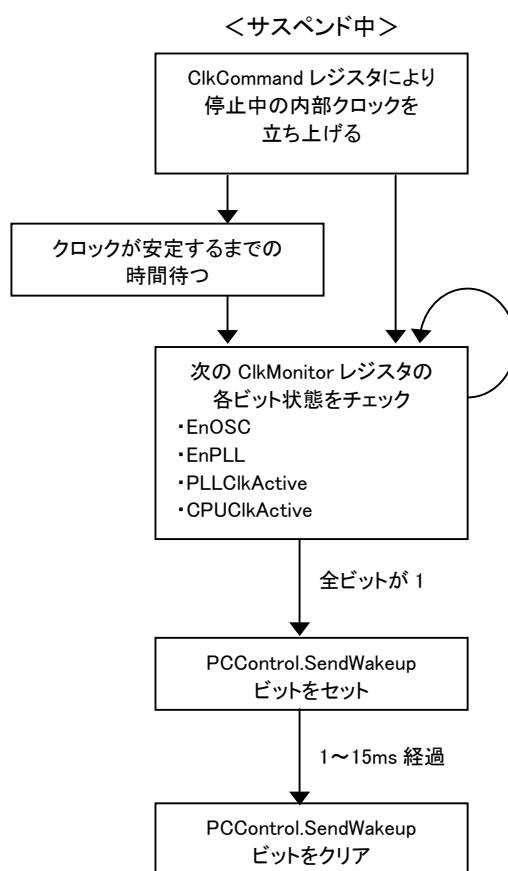

### 4.8.1 リモートウェイクアップ送出

ホストからリモートウェイクアップが許可されている場合には、ペリフェラル側の意思でサスPENDからの復帰を行うことができます。

リモートウェイクアップ信号(K状態)の送出は、PCControl.SendWakeupビットの設定によって行います。このレジスタは内部クロック停止中はアクセス不可となるので、レジスタにアクセスする以前に停止しているクロックを起動する必要があります。少なくとも ClkControl.OSCWakeupTime または PLLWakeupTime レジスタで指定した時間経過後、SendWakeup ビットを設定してウェイクアップ信号を送出します。ウェイクアップ信号送出時間は S/W が管理します。1~15ms 経過後(→USB Specification Rev.2.0 – 7.1.7.7) SendWakeup ビットをクリアしてウェイクアップ信号を停止します。

これらの手順を以下に示します。

Fig. 4-8 リモートウェイクアップ手順

通常、ペリフェラルがウェイクアップ信号の送出を中止しても、ホスト(ダウンストリーム)のリジューム制御によってラインステートは K 状態に一定時間保たれたままとなります。そのリジューム信号の出力が完了した時点でリジューム完となります。

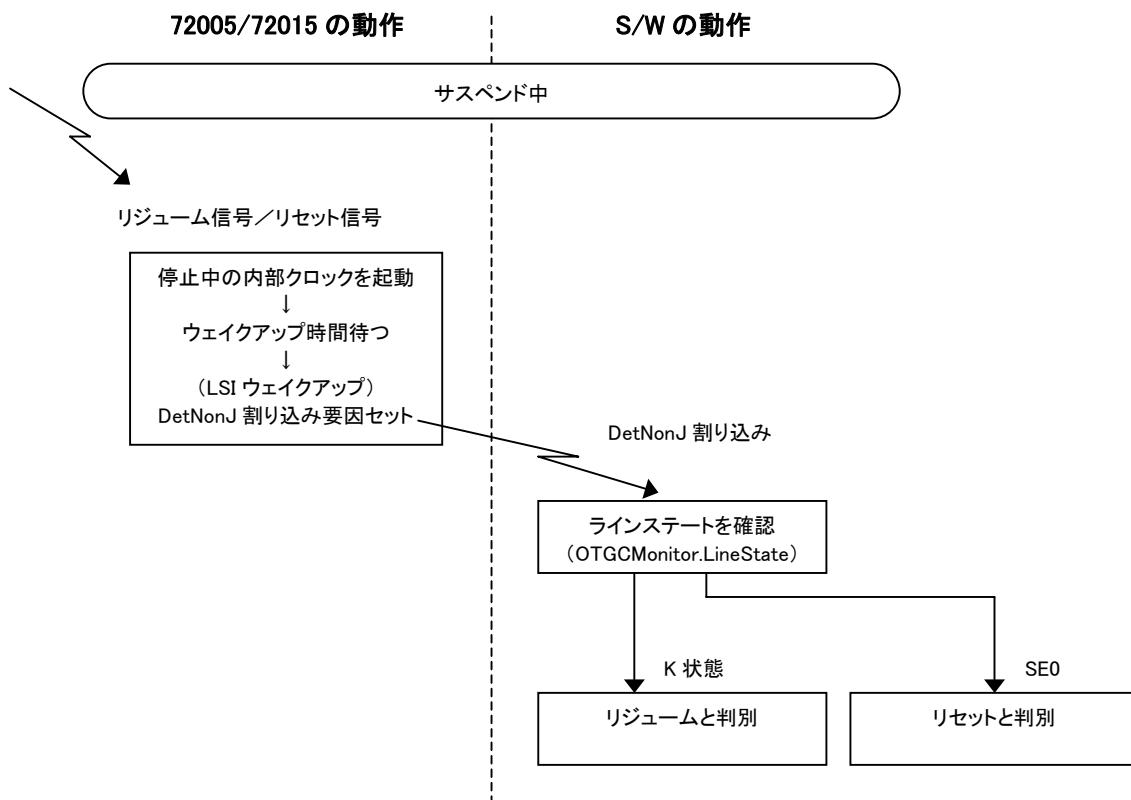

#### 4.8.2 リジューム／リセット受信

ペリフェラルは、サスPEND中にホスト(ダウンストリーム)からリジューム信号(K 状態)またはリセット信号(SE0)を受信した場合はサスPENDから復帰しなければなりません。

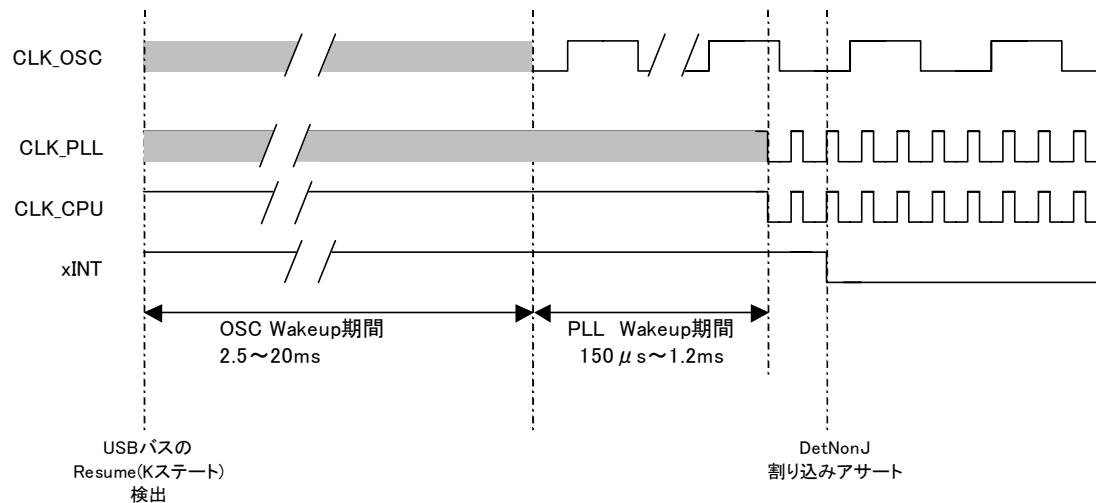

サスPEND中にリジューム信号／リセット信号が検出されると、停止していた内部クロックが自動的に所定のウェイクアップ時間を経て立ち上がります。その時点で DetNonJ の割り込み要因がセットされます。

S/W は DetNonJ 割り込みをトリガにして、OTGCMonitor.LineState フィールドから USB のラインステートをチェックします。ラインステートが K 状態であればリジューム信号を、SE0 であればリセット信号を受信していることになります。

Fig. 4-9 サスPEND中のリジューム／リセット信号受信動作

【注意】通常のサスPEND時におけるリジューム検出では DetResume 割り込み要因はセットされません。DetResume 要因は、HNP 動作時の OTG ステート“b\_wait\_acon”時のみでセットされます。

【注意】72005/72015 がリジューム信号(J 状態以外)を検出してから、実際に DetNonJ 割り込み要因がセットされるまでの時間は、最大で ClkControl.OSCWakeupTime と PLLWakeuoTime の合計の時間掛かることになります。また、この時間は、サスPEND時の ClkCommand レジスタの設定内容によって変動します。

【注意】S/W は、ホストが出力するリジューム信号およびリセット信号の最小出力時間(理論値)から LSI のクロック復帰に必要な時間を差し引いた時間以内に、ラインステートのチェックを行う必要があります。そうしないと、ホストの信号出力終了後にラインステートチェックを行うこととなり、信号内容を正しく判定できることになります。

【参考】DetNonJ 要因の検出は、ラインステートが J 状態から J 状態以外になった場合に行っています。

### 4.9 USB リセット

ペリフェラルは、ホストの出力する USB リセット信号を検出し、それに対する処理を行う必要があります。

USB リセットは DetReset 割り込み要因で判断します。

Tab. 4-9 USB リセット割り込み

| 割り込み要因ビット名 | 意味         | 内容                          | 有効 OTG ステート                  |

|------------|------------|-----------------------------|------------------------------|

| DetReset   | USB リセット検出 | ラインステートに 5ms の SE0 を検出した場合。 | b_peripheral<br>a_peripheral |

ペリフェラルは、USB リセットでデバイスアドレスを 0 にリセットします。また、エンドポイント 0 によるエニュメレーション動作がいつでも開始できる状態でいる必要があります。

## 5. OTG 制御

OTG 制御には次のような項目があります。

- ▶ VBUS の制御

- ▶ プルアップ抵抗の ON/OFF

- ▶ ホスト／ペリフェラルコントローラのイネーブル／ディセーブル

- ▶ VBUS 電圧の監視

- ▶ ラインステートの監視(接続／切断(接続相手のプルアップ ON/OFF)の監視)

- ▶ ID ピン状態の監視

これらの項目の動作内容は OTG 規格で定められる OTG ステート毎に一意に決まっています。

72005/72015 は、これらの制御を OTG 規格に則り OTG ステートコマンドにより一括して制御するようにしています。各OTGステートにおけるOTG制御をまとめたものを Tab. 5-1 に示します。

Tab. 5-1 各 OTG ステートの制御内容

|           | ステート名         | ステート内容              | レジスタ値 | プルアップ | VBUS 供給 | ラインステート監視内容                                | 割り込み                                            |

|-----------|---------------|---------------------|-------|-------|---------|--------------------------------------------|-------------------------------------------------|

| A<br>デバイス | a_idle        | A アイドル              | 0x0   | OFF   | OFF     | SRP(データラインパルシング)検出                         | DetSRP                                          |

|           | a_wait_vrise  | VBUS 起動開始&立ち上がり待ち   | 0x1   | OFF   | ON (5V) | —                                          | —                                               |

|           | a_wait_bcon   | B デバイス接続待ち          | 0x2   | OFF   | ON (5V) | 接続検出<br>切断検出                               | ChangeConnStat                                  |

|           | a_host        | ホスト機能イネーブル          | 0x3   | OFF   | ON (5V) | 切断検出                                       | ChangeConnStat                                  |

|           | a_suspend     | ホスト機能イネーブル(サスペンド)   | 0x4   | OFF   | ON (5V) | 切断検出                                       | ChangeConnStat                                  |

|           | a_peripheral  | ペリフェラル機能イネーブル       | 0x5   | ON    | ON (5V) | サスPEND検出                                   | DetSuspend                                      |

|           | a_vbus_err    | VBUS エラー(電圧降下＝過電流)  | 0x6   | OFF   | OFF     | —                                          | —                                               |

| B<br>デバイス | a_wait_vfall  | VBUS 電圧完全降下待ち       | 0x7   | OFF   | OFF     | —                                          | —                                               |

|           | b_idle        | B アイドル              | 0x8   | OFF   | OFF     | —                                          | —                                               |

|           | b_srp_init_d  | データラインパルシング起動       | 0x9   | OFF   | OFF     | —                                          | —                                               |

|           | b_srp_init_v  | VBUS パルシング起動(3V 出力) | 0xA   | OFF   | ON (3V) | —                                          | —                                               |

|           | b_srp_init_v5 | VBUS パルシング起動(5V 出力) | 0xE   | OFF   | ON (5V) | —                                          | —                                               |

|           | b_peripheral  | ペリフェラル機能イネーブル       | 0xB   | ON    | OFF     | リセット検出<br>サスPEND検出<br>サスPEND中のリセット・リジューム検出 | DetReset<br>DetSuspend<br>DetNonJ <sup>※1</sup> |

|           | b_wait_acon   | A デバイス接続待ち          | 0xC   | OFF   | OFF     | 接続検出<br>リジューム検出                            | ChangeConnStat<br>DetResume                     |

|           | b_host        | ホスト機能イネーブル          | 0xD   | OFF   | OFF     | 切断検出                                       | ChangeConnStat                                  |

VBUS 電圧の監視(Cross44V 割り込み要因)、および ID ピン状態の監視(ChangeID 割り込み要因)は、OTG ステートに関わらず行われます。

**【注意】** ラインステート監視機能(ラインステートによる割り込み要因)は、一度該当するラインステートの状態が検出されると、OTG ステートコマンドレジスタにライトアクセスが発生するか、ラインステートに変化が生じるまで、その検出は行われません。

※1 サスPEND中における ClkCommand レジスタによるクロック停止中のみ検出されます。

## 5. OTG 制御

---

### 5.1 割り込み

#### 5.1.1 割り込みの種類

OTG の割り込み要因として、72005/72015 は以下のようなものがあります。

Tab. 5-2 OTG 割り込み一覧

|         | 割り込み要因         | 意味               | 要因セットタイミング                          |

|---------|----------------|------------------|-------------------------------------|

| 共通      | ChangeID       | ID ピン状態変化検出      | OTGCMonitor.ID:<br>0→1 または 1→0      |

|         | Cross44V       | VBUS 4.4V しきい値通過 | OTGCMonitor.Comp44V:<br>0→1 または 1→0 |

|         | ChangeConnStat | 接続状態検出           | J:3us(接続)または<br>SE0:3us(切断)         |

| ホスト時    | DetSRP         | SRP 検出           | J:5ms 以上 10ms 以下                    |

|         | DetRmtWkup     | リモートウェイクアップ検出    | K:3us                               |

| ペリフェラル時 | DetReset       | リセット検出           | SE0:5ms                             |

|         | DetSuspend     | サスPEND検出         | J:5ms                               |

|         | DetNonJ        | サスPEND時 J 状態以外検出 | J→J 以外                              |

|         | DetResume      | リジューム検出          | SE0→K                               |

## 5.1.2 OTG ステートと割り込み

72005/72015 で用意している OTG 割り込みは、ある特定のステートの時のみで検出が行われます。

**【注意】** ラインステートの監視による割り込み要因は、一度該当するラインステートの状態が検出されると、新たに OTG ステートコマンドレジスタにライトアクセスが発生するか、ラインステートに変化が生じるまで、その検出は行われません。

OTGステートと検出が有効なOTG割り込みの対応関係を Tab. 5-3 に示します。

Tab. 5-3 OTG ステートと割り込み対応表

|                   | OTG ステート             | その他条件       | 共通                |                        |                |                 | ホスト時        |             | ペリフェラル時    |             |          |            |

|-------------------|----------------------|-------------|-------------------|------------------------|----------------|-----------------|-------------|-------------|------------|-------------|----------|------------|

|                   |                      |             | Change ID         | Cross44V               | ChangeConnStat |                 | DetSRP      | Det RmtWkup | Det Reset  | Det Suspend | Det NonJ | Det Resume |

|                   |                      |             | ID:<br>0→1<br>1→0 | Comp44V:<br>0→1<br>1→0 | J 3us<br>(接続)  | SE0 3us<br>(切断) | J<br>5-10ms | K 3us       | SE0<br>5ms | J 5ms       | J→J 以外   | J→K        |

| A<br>デ<br>バイ<br>ス | a_idle               |             | ○                 | ○                      | ×              | ×               | ○           | ×           | ×          | ×           | ×        | ×          |

|                   | a_wait_vrise         |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | a_wait_bcon          |             | ○                 | ○                      | ○              | ○               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | a_host/<br>a_suspend | Reset       | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   |                      | Operational | ○                 | ○                      | ×              | ○               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | Suspend              |             | ○                 | ○                      | ×              | ○               | ×           | ○           | ×          | ×           | ×        | ×          |

|                   | Resume               |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | a_peripheral         | Normal      | ○                 | ○                      | ×              | ×               | ×           | ×           | ○          | ○           | ×        | ×          |

|                   |                      | ClockStop   | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ○        | ×          |

|                   | a_vbus_err           |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | a_wait_vfall         |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

| B<br>デ<br>バイ<br>ス | b_idle               |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | b_srp_init_d         |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | b_srp_init_v         |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | b_srp_init_v5        |             | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   | b_peripheral         | Normal      | ○                 | ○                      | ×              | ×               | ×           | ×           | ○          | ○           | ×        | ×          |

|                   |                      | ClockStop   | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ○        | ×          |

|                   | b_wait_acon          |             | ○                 | ○                      | ○              | ×               | ×           | ×           | ×          | ×           | ×        | ○          |

|                   | b_host               | Reset       | ○                 | ○                      | ×              | ×               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   |                      | Operational | ○                 | ○                      | ×              | ○               | ×           | ×           | ×          | ×           | ×        | ×          |

|                   |                      | Suspend     | ○                 | ○                      | ×              | ○               | ×           | ○           | ×          | ×           | ×        | ×          |

## 5. OTG 制御

### 5.2 OTG デュアルロールデバイスの場合の制御

OTG デュアルロールデバイスの場合、OTG ステートの管理は原則的に OTG 規格書(Revision 1.0aRC5)内に記載されている遷移に従うものとします。

#### 5.2.1 遷移トリガ一覧

OTG 規格書に記載されている遷移の条件に相当するイベントを、カレントステート別に以下に示します。以下の一覧は、OTG ステートの遷移のみに着眼しています。このほかに、ホスト／ペリフェラルになった場合の処理が加わることとなります。

※ これらの一覧はあくまで指標です。OTG 規格を満足する保証はありません。また、これらはシステムや S/W 設計内容により異なる場合もあります。

イベントには大きく分けて、72005/72015 の H/W 割り込みと S/W の要求があります。カレントステートと、そのとき発生したイベントによって遷移先が決まります。

##### 5.2.1.1 a\_idle ~ a\_wait\_vrise

Tab. 5-4 遷移トリガ(a\_idle～a\_wait\_vrise)

|   | カレントステート     | 上段: 規格書遷移条件<br>下段: 相当するイベント                        | その他必要条件<br>(アンド条件)                      | 遷移先          | 備考          |

|---|--------------|----------------------------------------------------|-----------------------------------------|--------------|-------------|

| 1 | a_idle       | a_bus_drop/<br>(S/W)VBUS起動要求                       | a_bus_req<br>(S/W) USB使用要求が既にある         | a_wait_vrise |             |

| 2 |              | a_bus_drop/<br>(S/W)VBUS起動要求                       | a_srp_det<br>(S/W) DetSRP割り込み発生後5s以内である |              | Max5s       |

| 3 |              | a_bus_req/<br>(S/W)USB使用要求                         | a_bus_drop/<br>(S/W) VBUS起動要求が既にある      |              |             |

| 4 |              | a_srp_det/<br>(H/W)DetSRP割り込み                      | a_bus_drop/<br>(S/W) VBUS起動要求が既にある      |              |             |

| 5 |              | id/<br>(H/W)ChangeID割り込み                           | -                                       | b_idle       | ID:0→1      |

| 6 | a_wait_vrise | id<br>(H/W)ChangeID割り込み                            | -                                       | a_wait_bcon  | ID:0→1      |

| 7 |              | a_bus_drop<br>(S/W)VBUS停止要求                        | -                                       |              |             |

| 8 |              | a_vbus_vld<br>(H/W)Cross44V割り込み                    | -                                       |              | Comp44V:0→1 |

| 9 |              | a_wait_vrise_tmout<br>(S/W)a_wait_vrise_tmrタイムT.O. | -                                       |              | Max100ms    |

## 5.2.1.2 a\_wait\_bcon ~ a\_host

Tab. 5-5 遷移トリガ(a\_wait\_bcon~a\_host)

|    | カレント<br>ステート | 上段:規格書遷移条件<br>下段:相当するイベント                          | その他必要条件<br>(アンド条件)           | 遷移先 | 備考                                                                                                                   |

|----|--------------|----------------------------------------------------|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| 1  | a_wait_bcon  | b_conn (Long debounce)<br>(H/W)ChangeConnStat割り込み  | -<br>(S/W) (Min100ms間 切断検出無) | -   | a_host<br>LineState:J 3us<br>a_wait_vrise, a_host から遷移時。<br>割り込み後Min100msの間、切断が検出されなかつたら初めて a_host に遷移する。            |

| 2  |              | b_conn (Short debounce)<br>(H/W)ChangeConnStat割り込み | -                            | -   | a_host<br>LineState:J 3us<br>a_host, a_suspend, a_peripheral から遷移時。<br>割り込み後Min100msの間、切断が検出されなかつたら初めて a_host に遷移する。 |

| 3  |              | id<br>(H/W)ChangeID割り込み                            | -                            | -   | a_wait_vfall<br>ID:0→1                                                                                               |

| 4  |              | id<br>(H/W)ID=1                                    | -                            | -   | a_wait_vrise, a_host から遷移時                                                                                           |

| 5  |              | a_bus_drop<br>(S/W)VBUS停止要求                        | -                            | -   |                                                                                                                      |

| 6  |              | a_bus_drop<br>(S/W)VBUS停止要求が既にある                   | -                            | -   | a_wait_vrise, a_host から遷移時                                                                                           |

| 7  |              | a_wait_bcon_tmout<br>(S/W)a_wait_bcon_tmrタイムT.O.   | -                            | -   | Min1s                                                                                                                |

| 8  |              | a_vbus_vld/<br>(H/W)Cross44V割り込み                   | -                            | -   | a_vbus_err<br>Comp44V:1→0                                                                                            |

| 9  |              | (Long debounce時間中の切断)<br>(H/W)ChangeConnStat割り込み   | -<br>LineState=SE0           | -   | a_wait_bcon<br>LineState:SE0 3us<br>Long debounce時間中の切断時は a_wait_bcon へ再帰。                                           |

| 10 | a_host       | a_bus_req/<br>(S/W)USB使用停止要求                       | -                            | -   | a_suspend                                                                                                            |

| 11 |              | a_suspend_req<br>(S/W)サスPEND要求                     | -                            | -   |                                                                                                                      |

| 12 |              | id<br>(H/W)ChangeID割り込み                            | -                            | -   | a_wait_bcon<br>ID:0→1                                                                                                |

| 13 |              | b_conn/<br>(H/W)ChangeConnStat割り込み                 | -                            | -   | LineState:SE0 3us                                                                                                    |

| 14 |              | a_bus_drop<br>(S/W)VBUS停止要求                        | -                            | -   |                                                                                                                      |

| 15 |              | a_vbus_vld/<br>(H/W)Cross44V割り込み                   | -                            | -   | a_vbus_err<br>Comp44V:1→0                                                                                            |

## 5. OTG 制御

### 5.2.1.3 a\_suspend ~ a\_peripheral

Tab. 5-6 遷移トリガ(a\_suspend～a\_peripheral)

|    | カレント<br>ステート | 上段:規格書遷移条件<br>下段:相当するイベント                              | その他必要条件<br>(アンド条件)                                          | 遷移先          | 備考                                |

|----|--------------|--------------------------------------------------------|-------------------------------------------------------------|--------------|-----------------------------------|

| 1  | a_suspend    | b_conn/<br>(H/W)ChangeConnStat割<br>り込み                 | a_set_b_hnp_en<br>(S/W)<br>SetFeature(b_hnp_enable)<br>送信済み | -            | a_peripheral<br>LineState:SE0 3us |

| 2  |              | b_conn/<br>(H/W)ChangeConnStat割<br>り込み                 | a_set_b_hnp_en/<br>(S/W)<br>SetFeature(b_hnp_enable)<br>未送信 | -            | a_wait_bcon<br>LineState:SE0 3us  |

| 3  |              | a_bus_req<br>(S/W)USB使用要求                              | -                                                           | a_host       |                                   |

| 4  |              | b_bus_resume<br>(H/W)DetRmtWkup割り込<br>み                | -                                                           |              | LineState:K 3us                   |

| 5  |              | id<br>(H/W)ChangeID割り込み                                | -                                                           | a_wait_vfall | ID:0→1                            |

| 6  |              | a_bus_drop<br>(S/W)VBUS停止要求                            | -                                                           |              |                                   |

| 7  |              | a_aidl_bdis_tmout<br>(S/W)a_aidl_bdis_tmoutタ<br>イマT.O. | -                                                           |              | Min200ms                          |

| 8  |              | a_vbus_vld/<br>(H/W)Cross44V割り込み                       | -                                                           | a_vbus_err   | Comp44V:1→0                       |

| 9  | a_peripheral | b_bus_suspend<br>(H/W)DetSuspend割り込み                   | -                                                           | a_wait_bcon  | LineState:J 5ms                   |

| 10 |              | id<br>(H/W)ChangeID割り込み                                | -                                                           |              | ID:0→1                            |

| 11 |              | a_bus_drop<br>(S/W)VBUS停止要求                            | -                                                           | a_vbus_err   |                                   |

| 12 |              | a_vbus_vld/<br>(H/W)Cross44V割り込み                       | -                                                           |              | Comp44V:1→0                       |

## 5.2.1.4 a\_vbus\_err ~ a\_wait\_vfall

Tab. 5-7 遷移トリガ(a\_vbus\_err~a\_wait\_vfall)

|   | カレント<br>ステート | 上段:規格書遷移条件<br>下段:相当するイベント              | その他必要条件<br>(アンド条件)       |   | 遷移先          | 備考                              |  |

|---|--------------|----------------------------------------|--------------------------|---|--------------|---------------------------------|--|

| 1 | a_vbus_err   | id<br>(H/W)ChangeID割り込み                | -                        | - | a_wait_vfall | ID:0→1                          |  |

| 2 |              | a_bus_drop<br>(S/W)VBUS停止要求            | -                        | - |              |                                 |  |

| 3 |              | a_clr_err<br>(S/W)過電流エラー解除<br>要求       | -                        | - |              | 過電流通知後の対応で発生する要求                |  |

| 4 | a_wait_vfall | id<br>(H/W)ChangeID割り込み                | -                        | - | a_idle       | ID:0→1                          |  |

| 5 |              | a_bus_req<br>(S/W)USB使用要求              | -                        | - |              |                                 |  |

| 6 |              | b_conn/<br>(H/W)ChangeConnStat割<br>り込み | a_sess_vld/<br>Comp20V=0 | - |              | Comp20Vポーリング周期は数ms～數十<br>msでもよい |  |

| 7 |              | b_conn/<br>(H/W)LineState=SE0          | a_sess_vld/<br>Comp20V=0 | - |              |                                 |  |

## 5. OTG 制御

### 5.2.1.5 b\_idle ~ b\_init\_srp\_d ~ b\_init\_srp\_v ~ b\_init\_srp\_v5

Tab. 5-8 遷移トリガ(b\_idle~b\_init\_srp\_d~b\_init\_srp\_v~b\_init\_srp\_v5)

|    | カレントステート     | 上段:規格書遷移条件<br>下段:相当するイベント                           | その他必要条件<br>(アンド条件)                              |                                        | 遷移先          | 備考                                                                                                                           |

|----|--------------|-----------------------------------------------------|-------------------------------------------------|----------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| 1  | b_idle       | b_bus_req<br>(S/W)USB使用要求(SRP起動要求)                  | b_sess_end<br>(S/W) vfall_tmr(1.1s) タイマT.O.既に完了 | b_se0_srp<br>(LSI) LineStat=SE0 2ms 確認 | b_srp_init_d | SE0の監視は最初と2ms(Min)後だけでよい                                                                                                     |

| 2  |              | b_sess_end<br>(S/W)vfall_tmr タイマT.O.                | b_bus_req<br>(S/W) USB使用要求(SRP起動要求)が既にある        | b_se0_srp<br>(LSI) LineStat=SE0 2ms 確認 |              | SE0の監視は最初と2ms(Min)後だけでよい<br>Min1.1s                                                                                          |

| 3  |              | b_sess_vld/<br>(H/W)Cross44V割り込み<br>or<br>Comp20V=1 | -                                               | -                                      | b_peripheral | Comp44V:1→0<br>本来はComp20V=0をトリガしたいが、割り込みを使いたい場合はこれで代用する。                                                                     |

| 4  |              | b_sess_vld<br>(H/W)Comp44V=0                        | -                                               | -                                      |              | b_srp_init_d/v から遷移時                                                                                                         |

| 5  |              | id/<br>(H/W)ChangeID割り込み                            | -                                               | -                                      | a_idle       | ID:1→0                                                                                                                       |

| 6  |              | id/<br>(H/W)ID=0                                    | -                                               | -                                      |              | b_srp_init_d/v, b_host, b_wait_acon, b_peripheral から遷移時                                                                      |

| 7  |              | -<br>(S/W)VBUS起動待ちタイマ(5s)T.O. :TB_SRP_FAIL          | -                                               | -                                      | 遷移無し         | 上位にSRP応答無しを通知<br>Min5s~Max30s                                                                                                |

| 8  | b_srp_init_d | id/<br>(H/W)ChangeID割り込み                            | -                                               | -                                      | b_idle       | ID:1→0                                                                                                                       |

| 9  |              | b_srp_done<br>(H/W)Cross44V割り込み                     | -                                               | -                                      |              | DataLinePulsing中にAデバイスがVBusを立ち上げてきた場合。<br>VB_SESS_VLDはMax4.0Vなので<br>Comp20Vを参照するのが正当だが、割り込みを用いなければならない場合は<br>Cross44V で代用する。 |

| 10 |              | b_srp_done<br>(H/W)Comp20V=1                        | -                                               | -                                      |              |                                                                                                                              |

| 11 |              | -<br>(S/W)DataLinePulsingタイマT.O. :TB_DATA_PLS       | -                                               | -                                      | b_srp_init_v | 次VBusPulsingへ<br>Min5ms~Max10ms                                                                                              |

| 12 | b_srp_init_v | id/<br>(H/W)ChangeID割り込み                            | -                                               | -                                      | b_idle       | ID:1→0                                                                                                                       |

| 13 |              | b_srp_done<br>(S/W)TB_SRP_INIT T.O.                 | -                                               | -                                      |              | Max100ms                                                                                                                     |

| 14 |              | b_srp_done<br>(H/W)Cross44V割り込み                     | -                                               | -                                      |              | VBusPulsing中にAデバイスがVBusを立ち上げてきた場合                                                                                            |

| 15 |              | -<br>(S/W)SessionValid(2.0V)<br>確認タイマ(TBD)T.O.      | A_SESS_VLD<br>(LSI) Comp20V=1                   | -                                      |              | 相手が標準Hostの場合 :SRP Abort(TB_SRP_FAILタイマ停止)                                                                                    |

## 5.2.1.6 b\_peripheral ~ b\_wait\_acon ~ b\_host

Tab. 5-9 遷移トリガ(b\_peripheral~b\_wait\_acon~b\_host)

|    | カレントステート     | 上段:規格書遷移条件<br>下段:相当するイベント                                | その他必要条件<br>(アンド条件)                    |                                                    | 遷移先          | 備考                                                       |

|----|--------------|----------------------------------------------------------|---------------------------------------|----------------------------------------------------|--------------|----------------------------------------------------------|

| 1  | b_peripheral | a_bus_suspend<br>(H/W)DetSuspend割り込み                     | b_bus_req<br>(S/W) USB使用要求が既にある       | b_hnp_en<br>(S/W)<br>SetFeature(b_hnp_enable) 受信済み | b_wait_acon  |                                                          |

| 2  |              | b_bus_req<br>(S/W)USB使用要求                                | a_bus_suspend<br>(S/W) 既にSuspend状態である | b_hnp_en<br>(S/W)<br>SetFeature(b_hnp_enable) 受信済み |              |                                                          |

| 3  |              | id/<br>(H/W)ChangeID割り込み                                 | -                                     | -                                                  |              | ID:1→0                                                   |

| 4  |              | b_sess_vld/<br>(H/W)Cross44V割り込み<br>or<br>Comp20V=0      | -                                     | -                                                  |              | Comp44V:1→0<br>本来はComp20V=0をトリガしたいが、割り込みを使いたい場合はこれで代用する。 |

| 5  | b_wait_acon  | a_conn<br>(H/W)ChangeConnStat割り込み                        | -                                     | -                                                  | b_host       | LineState:J 3us                                          |

| 6  |              | a_bus_resume<br>(H/W)DetResume割り込み                       | -                                     | -                                                  | b_peripheral | LineState:SE0→K                                          |

| 7  |              | b_ase0_brst_tmout<br>(S/W)b_ase0_brst_tmrタイマT.O.         | -                                     | -                                                  |              | Min3.125ms                                               |

| 8  |              | id/<br>(H/W)ChangeID割り込み                                 | -                                     | -                                                  | b_idle       | ID:1→0                                                   |

| 9  |              | b_sess_vld/<br>(H/W)Cross44V割り込み<br>or<br>(H/W)Comp20V=0 | -                                     | -                                                  |              | Comp44V:1→0<br>本来はComp20V=0をトリガしたいが、割り込みを使いたい場合はこれで代用する。 |

| 10 |              | b_bus_req/<br>(S/W)USB使用停止要求                             | -                                     | -                                                  | b_peripheral | ≠b_hostでのSuspend                                         |

| 11 |              | a_conn/<br>(H/W)ChangeConnStat割り込み                       | -                                     | -                                                  |              | LineState:SE0 3us                                        |

| 12 |              | id/<br>(H/W)ChangeID割り込み                                 | -                                     | -                                                  | b_idle       | ID:1→0                                                   |

| 13 |              | b_sess_vld/<br>(H/W)Cross44V割り込み<br>or<br>(H/W)Comp20V=0 | -                                     | -                                                  |              | Comp44V:1→0<br>本来はComp20V=0をトリガしたいが、割り込みを使いたい場合はこれで代用する。 |

## 5. OTG 制御

### 5.2.2 SPR

B デバイス時では、Session-Request-Protocol(SRP)に対応する必要があります。SRP の実行は OTG ステートによって行います。

SRP はデータラインパルシングと VBUS パルシングの両方をサポートする必要があります。

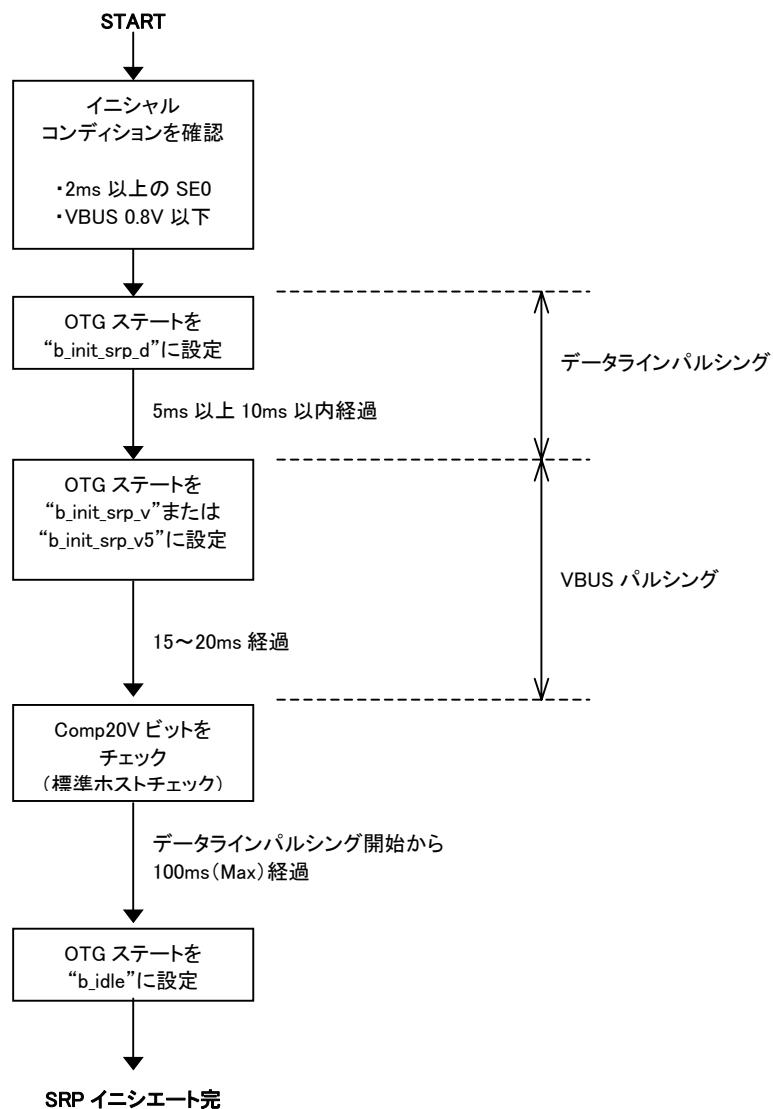

SRPのイニシエート手順を Fig. 5-1 に示します。

Fig. 5-1 SRP イニシエート手順

- ⑦ SRP を開始する前にイニシャルコンディション(2ms 以上の SE0 と VBUS 0.8V 以下)を確認します。

- ⑧ OTG ステートコマンドを“b\_srp\_init\_d”に設定します。これにより、データラインパルシング実行状態となり、USB データライン上に J 状態を作り出します。データラインパルシングの時間(5ms 以上 10ms 以下)は S/W が管理します。

データラインパルシング中に VBUS 電圧が既に B デバイスのセッション電圧に達している場合は、その時点で SRP を終了し、“b\_idle”→“b\_peripheral”的遷移を行います。

- ⑨ データラインパルシング時間経過後、OTG ステートコマンドを“b\_srp\_init\_v”または“b\_srp\_init\_v5”に設定します。これにより、VBUS パルシング実行状態となり、VBUS が出力されます。

データラインパルシングの開始から最高 100ms までの期間持続させます。

- ⑩ VBUS パルシングの開始から 15~20ms 経過しても B デバイスのセッション電圧に達しない(Comp20V が 1 とならない)場合は、SRP の相手は標準ホストであると考えられるため、直ちに OTG ステートを“b\_idle”にして SRP を終了させます。

**【注意】** SRP(VBUS パルシング)の相手が標準ホストの場合、許容時間以上 VBUS を出力し続けると、標準ホストを破損することになります。VBUS パルシング開始後は必ず、15~20ms 後に Comp20V の値をチェックするようにして下さい。

- ⑪ VBUS パルシング時間経過後、OTG ステートコマンドを“b\_idle”に設定して SRP のイニシエート終了となります。

この時点で VBUS 電圧が B デバイスのセッション電圧を超えている場合は、OTG ステートを“b\_peripheral”に設定してペリフェラル動作に移行することとなります。

**【参考】** OTG ステートの“b\_srp\_init\_v”と“b\_srp\_init\_v5”的違いは、VBUS の到達電圧が異なる点のみです。前者は 3.0V まで、後者は 5.0V まで上昇します。システムの VBUS 回路が 3.0V 電圧を作り出さ(せ)ない場合(外付けの場合等)に“b\_srp\_init\_v5”を使用し、通常の場合は“b\_srp\_init\_v”を使用するようにします。

### 5.3 ホストオンリーデバイスの場合の制御（＝ルートハブ制御）

VBUS の ON/OFF、ペリフェラルの接続・切断検出制御を行います。

#### 5.3.1 常に VBUS を ON とする場合

この方法では、ペリフェラルデバイスをケーブルによって物理的に接続された時点で VBUS の供給が行われ、ペリフェラルの接続検出となります。ただし、USB 転送が無い場合でも、ペリフェラルが物理的に接続されている限り、常に VBUS の供給が行われることになります。

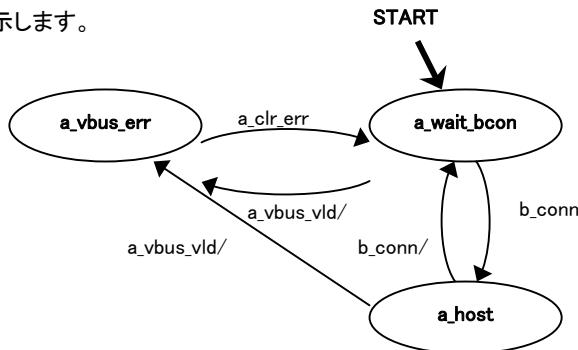

遷移の様子を Fig. 5-2 に示します。

Fig. 5-2 OTG ステート遷移(ホストオンリーデバイス; VBUS 常時 ON)

イニシャルステートを“a\_wait\_bcon”とし、ペリフェラルの接続で“a\_host”に遷移、切断で再び“a\_wait\_bcon”に戻るという OTG ステートの遷移を行います。

### 5.3.2 状況に応じ VBUS を OFF する場合

この方法では、ペリフェラルデバイスをケーブルで物理的に接続しても、ホスト側で USB 転送の要求が発生しない限り、VBUS の供給は行われなく、ペリフェラルも接続されたとは見なされないことになります。

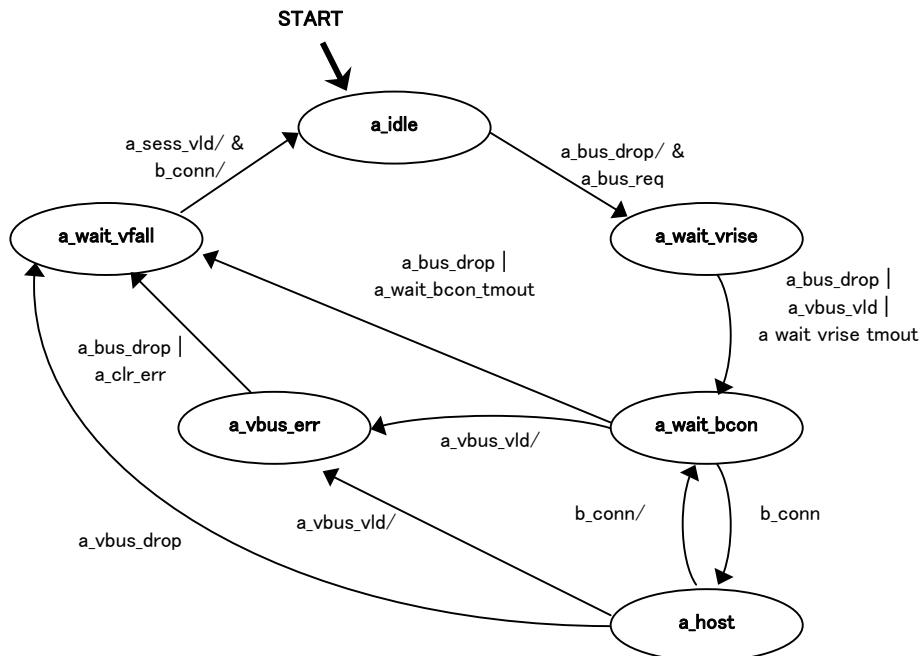

遷移の様子を Fig. 5-3 に示します。

Fig. 5-3 OTG ステート遷移(ホストオンリーデバイス; VBUS 選択 ON)

イニシャルステートは“a\_idle”とします。

USB 転送要求(a\_bus\_req)により VBUS を立ち上げます。(a\_wait\_vrise)

VBUS がバリッド電圧に達したら(a\_vbus\_vld)接続検出状態にします。(a\_wait\_bcon)

ペリフェラルの接続(b\_conn)を検出したら a\_host に遷移します。

一定時間ペリフェラルの接続が認められなかった場合(a\_wait\_bcon\_tmout)は、“a\_wait\_vfall”に遷移します。

a\_host 時に切断を検出した場合(b\_conn/)は“a\_wait\_bcon”に戻ります。

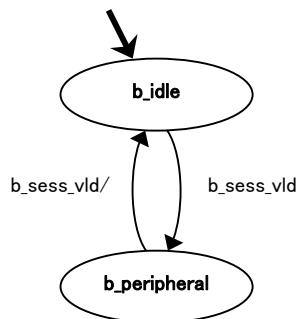

### 5.4 ペリフェラルオンリーデバイスの場合の制御

VBUS電圧変化のみを監視させます。すなわち、ホストの接続・切断のみを監視することになります。遷移の様子を Fig. 5-4 に示します。

Fig. 5-4 OTG ステート遷移(ペリフェラルオンリーデバイス)

イニシャルステートは“*b\_idle*”とします。VBus のセッション電圧を検出、すなわち OTGCMonitor.Comp20V ビットを監視して、1 となれば“*b\_peripheral*”に遷移させます。“*b\_peripheral*”時にセッション電圧が低下、すなわち OTGCMonitor.Comp20V ビットを監視して、0 となれば“*b\_idle*”に戻します。

## 6. 低消費電力制御

72005/72015 の各内部ブロックおよび回路は、OTG ステートによってそのアクティブ／非アクティブが一意に決定します。従って、不用なブロック・回路へのクロック供給や電源供給を停止することにより、LSI 全体としての消費電力を抑えることができます。

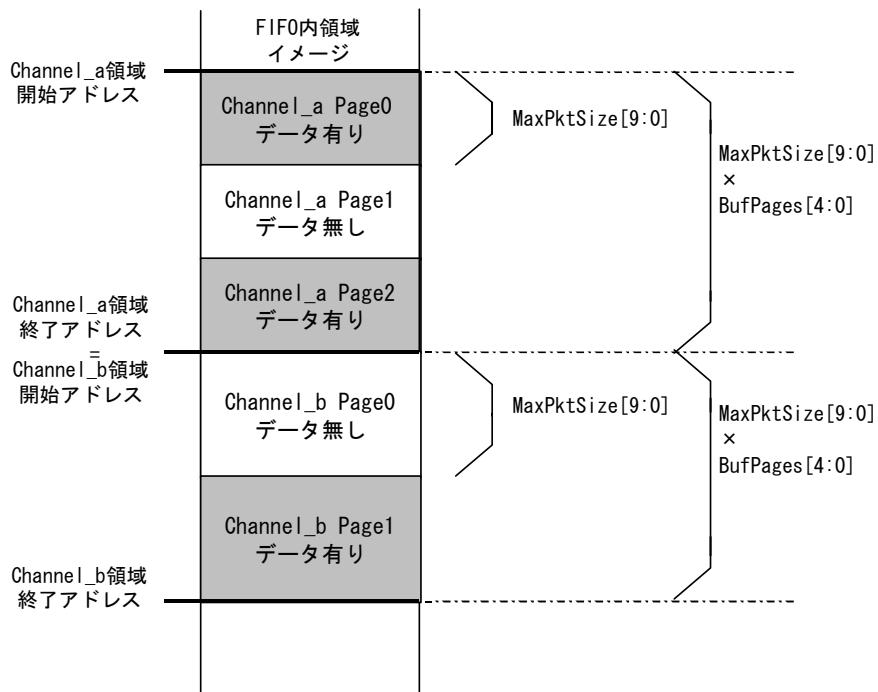

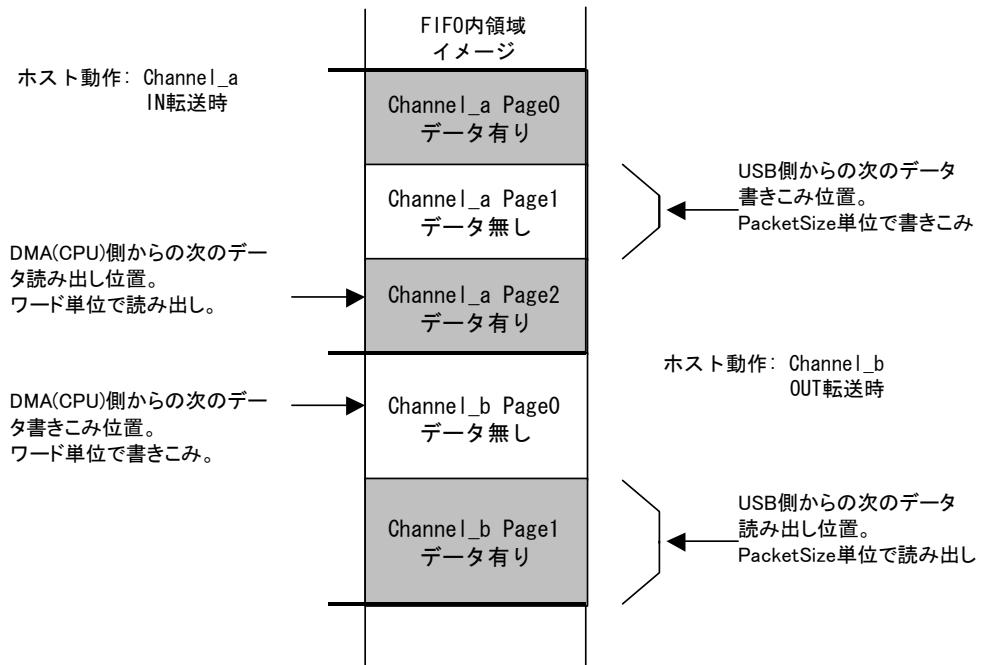

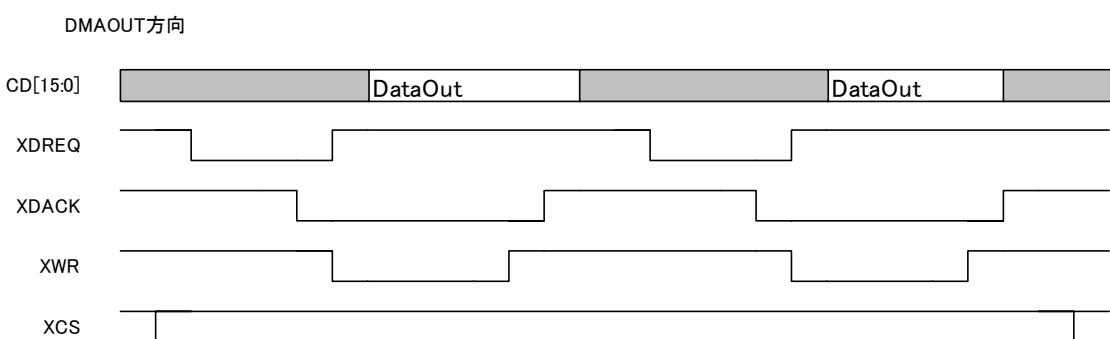

### 6.1 内部クロック供給制御