# **S1R72005B00A300/F00A300**

## **テクニカルマニュアル**

本資料のご使用につきましては、次の点にご留意願います。

-

1. 本資料の内容については、予告無く変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性値の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## 総則

- ・適用範囲

本仕様書は、セイコーエプソン株式会社 半導体事業部製

USB OnTheGo コントローラ 「S1R72005B00A300」 および「S1R72005F00A300」 に適用する。

## 目次

|                                        |    |

|----------------------------------------|----|

| 1. 概要 .....                            | 1  |

| 2. 特長 .....                            | 1  |

| 3. ブロック図 .....                         | 2  |

| 4. 端子配置図 .....                         | 3  |

| 4.1 CSPパッケージ .....                     | 3  |

| 4.2 QFPパッケージ .....                     | 4  |

| 5. 端子機能説明 .....                        | 5  |

| 5.1 CPU インタフェース .....                  | 5  |

| 5.2 USBインターフェース .....                  | 6  |

| 5.3 システム系 .....                        | 7  |

| 5.4 テスト信号 .....                        | 7  |

| 5.5 電源・GND・その他 .....                   | 8  |

| 6. 機能概要 .....                          | 9  |

| 6.1 Host Controller (HC) .....         | 9  |

| 6.2 Peripheral Controller (PC) .....   | 9  |

| 6.3 OTG Controller .....               | 9  |

| 6.4 HC/PC Common .....                 | 9  |

| 6.5 USB Transceiver .....              | 9  |

| 6.6 Control Registers .....            | 9  |

| 6.7 FIFO Manager .....                 | 10 |

| 6.8 FIFO SRAM .....                    | 10 |

| 6.9 CPU I/F .....                      | 10 |

| 6.10 DMA Handler .....                 | 10 |

| 6.11 CLK Controller .....              | 10 |

| 6.12 Test Module .....                 | 10 |

| 7. 電気的特性 .....                         | 11 |

| 7.1 絶対最大定格 .....                       | 11 |

| 7.2 推奨動作条件 .....                       | 11 |

| 7.3 DC特性 .....                         | 12 |

| 7.4 AC特性 .....                         | 15 |

| 7.4.1 クロックタイミング .....                  | 15 |

| 7.4.1.1 パワーオン発振安定時間 .....              | 15 |

| 7.4.1.2 CLKIN(27MHz)クロック入力タイミング .....  | 15 |

| 7.4.1.3 CLKIN(48MHz) クロック入力タイミング ..... | 16 |

| 7.4.1.4 CLKIN(12MHz) クロック入力タイミング ..... | 16 |

| 7.4.2 CPU I/F アクセス タイミング .....         | 17 |

|           |                                |           |

|-----------|--------------------------------|-----------|

| 7.4.2.1   | リード タイミング（外部xWAITモード） .....    | 17        |

| 7.4.2.2   | ライト タイミング（外部xWAITモード） .....    | 18        |

| 7.4.2.3   | リード タイミング（外部 xREADYモード） .....  | 19        |

| 7.4.2.4   | ライト タイミング（外部 xREADYモード） .....  | 20        |

| 7.4.2.5   | リード タイミング（固定WAITモード） .....     | 21        |

| 7.4.2.6   | ライト タイミング（固定 WAITモード） .....    | 22        |

| 7.4.3     | DMAタイミング .....                 | 23        |

| 7.4.3.1   | xRD・xWR ストローブモード(DMAOUT) ..... | 23        |

| 7.4.3.2   | xRD・xWR ストローブモード(DMAIN) .....  | 24        |

| 7.4.3.3   | DACKストローブモード(DMAOUT) .....     | 25        |

| 7.4.3.4   | DACK ストローブモード(DMAIN) .....     | 26        |

| 7.4.3.5   | DMASTRB SDRAMモード(DMAOUT) ..... | 27        |

| 7.4.3.6   | DMASTRB SDRAM モード(DMAIN) ..... | 28        |

| 7.4.3.7   | DMASTRB 汎用モード (DMAOUT) .....   | 29        |

| 7.4.3.8   | DMASTRB 汎用モード (DMAIN) .....    | 30        |

| 7.4.4     | USB I/F タイミング .....            | 31        |

| <b>8.</b> | <b>外形寸法図 .....</b>             | <b>32</b> |

| 8.1       | CSPパッケージ .....                 | 32        |

| 8.2       | QFPパッケージ .....                 | 33        |

| <b>9.</b> | <b>接続例.....</b>                | <b>34</b> |

| 9.1       | OTG I/F端子接続例 .....             | 34        |

| 9.2       | クロック端子接続例 .....                | 36        |

| 9.3       | CPU I/F端子接続例 .....             | 38        |

| 9.4       | 電源およびグランド端子接続例 .....           | 39        |

| 9.5       | テスト端子接続例 .....                 | 40        |

## 1. 概要

本 LSI は USB2.0 準拠の Full Speed (12Mbps) モードに対応した On-The-Go デバイスコントローラ LSI です。Host と Peripheral の両機能に加え On-The-Go の機能を 1 chip に集積し、Dual-role device としての動作を実現します。

USB 機器と PC との汎用的な接続性を従来どおりに提供すると共に、USB 機器同士による自由な接続性を新たに提供します。USB インタフェース電源(3.3V)と独立して CPU インタフェース用電源(2.8V～3.3V)を供給でき、さまざまな外部 CPU と接続可能です。

## 2. 特長

- Host 機能、Peripheral 機能、On-The-Go 機能をワンチップに搭載。

- I/O 2 電源対応 (USB 3.3V / CPUIF 2.8V～3.3V)

- On-The-Go (Supplement to the USB2.0) 1.0 版準拠。

- USB2.0 Full Speed (12Mbps) モードをサポート。

- On-The-Go ポート 1 個を装備。

- コントロール、バルク、インターラプト、およびアイソクロナス転送をサポート。

- USB 転送時の CPU 負荷低減と高スループットを実現するコントローラ・インターフェース。

- Peripheral 動作時、Endpoint 0 および 5 本の汎用 Endpoint をサポート。

- データ転送用 2.5kByteFIFO を内蔵。

- FIFO はリング・バッファ方式を採用。

- 16bit 幅の汎用 CPU I/F を搭載。

- 16bit 幅の汎用 DMA スレーブとして動作可能 (CPU I/F とバスを共用)。

- クロック入力 12MHz の発振子に対応 (発振回路内蔵)。

- 通倍 PLL 回路を内蔵。

- 水晶発振器からの外部クロック入力 12MHz、27MHz、48MHz にも対応。

- 徹底したクロック制御による低消費電力の実現。

- 81pin CSP パッケージまたは 64pin QFP パッケージ

※耐放射線設計はされておりません。

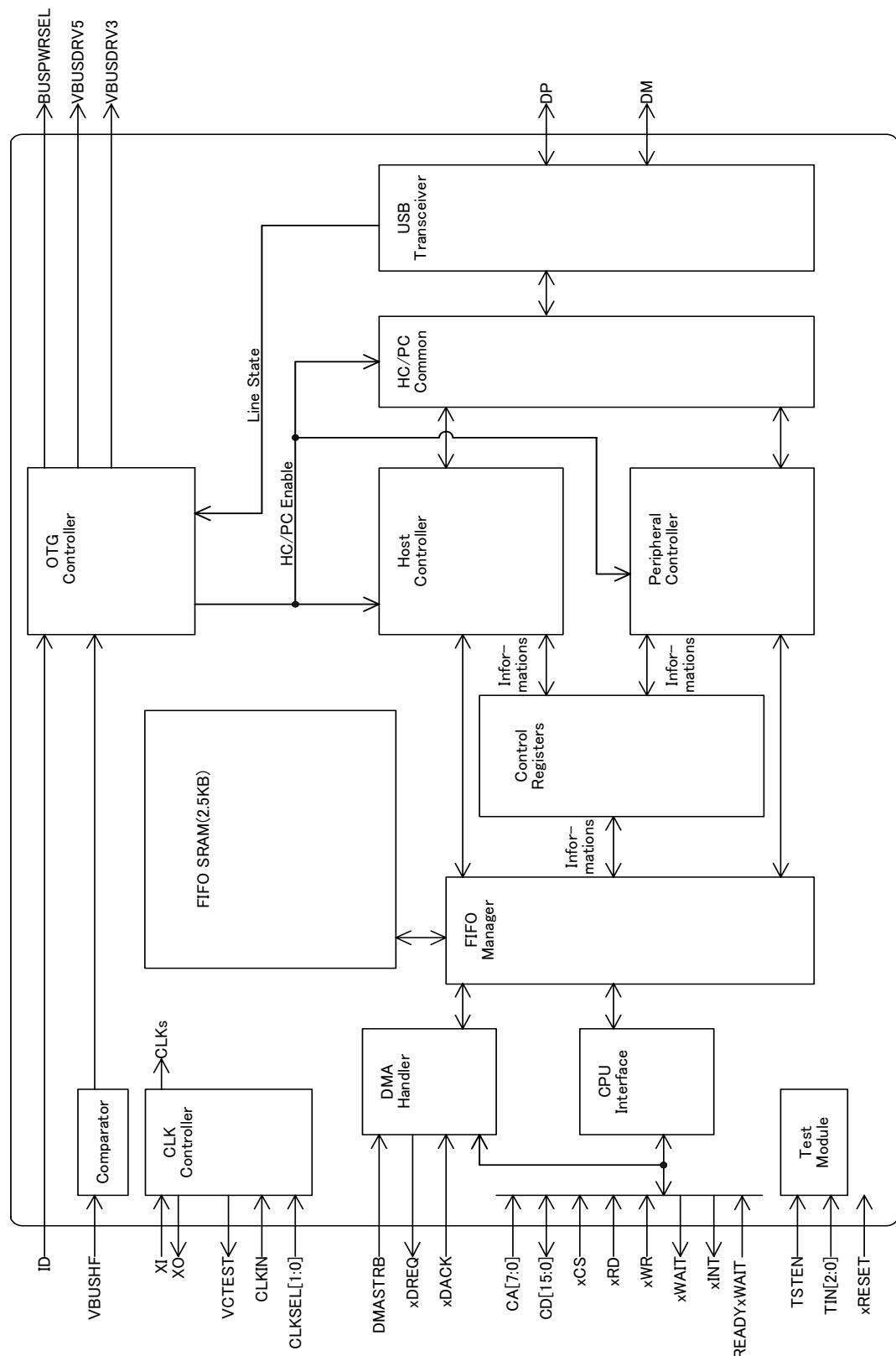

### 3. ブロック図

#### 3. ブロック図

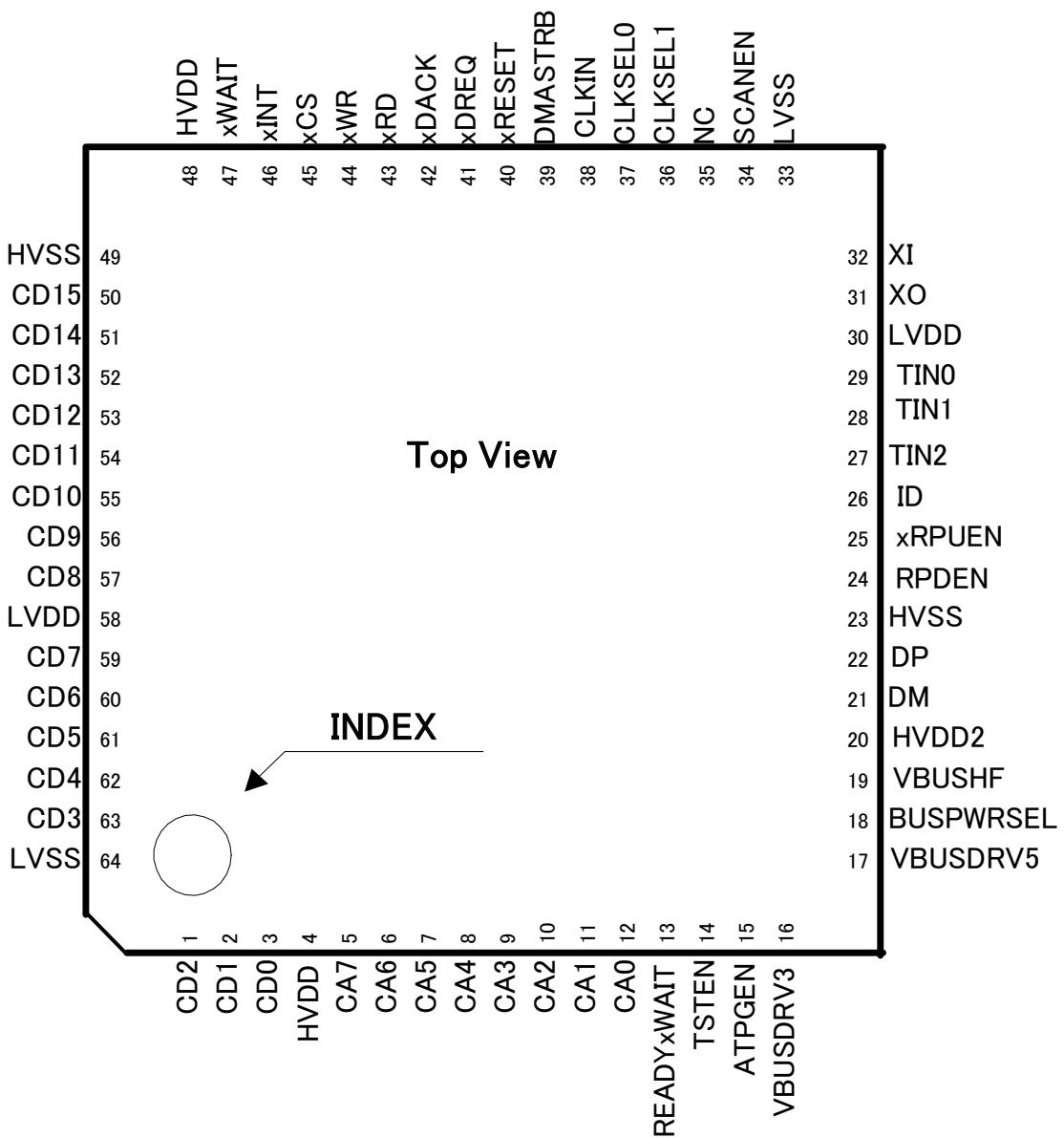

## 4. 端子配置図

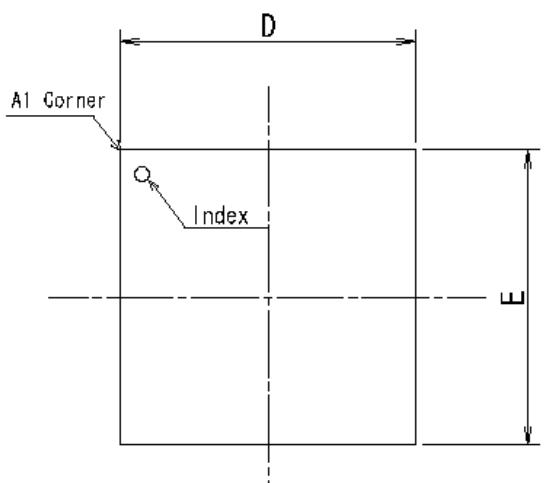

### 4.1 CSP パッケージ

| J |           | VBUS DRV5   | VBUSHF     | DM   | RPDEN  | ID        | LVDD     | XI     |          |

|---|-----------|-------------|------------|------|--------|-----------|----------|--------|----------|

| H | VBUS DRV3 | READYx WAIT | BUS PWRSEL | DP   | HVSS   | TIN2      | XO       | TIN0   | LVSS     |

| G | TSTEN     | ATPGEN      | HVDD2      |      |        | TIN1      | CLKSEL 1 | SCANEN |          |

| F | CA2       | CA1         | CA0        |      | XRPUEN |           |          | CLKIN  | CLKSEL 0 |

| E | CA3       | CA4         | CA5        |      |        | COMPIN 22 | DMA STRB | XRESET | XDREQ    |

| D | CA7       | CA6         |            |      |        | COMPIN 10 | XWR      | XRD    | XDACK    |

| C | CD0       | CD1         | HVDD       | CD6  | CD10   |           | CD13     | XWAIT  | XINT     |

| B | CD2       | CD5         | CD3        | CD7  | CD9    | CD11      | CD15     | XCS    | HVDD     |

| A |           | LVSS        | CD4        | LVDD | CD8    | CD12      | CD14     | HVSS   |          |

|   | 1         | 2           | 3          | 4    | 5      | 6         | 7        | 8      | 9        |

Bottom View

※READYxWAIT および HVDD, HVDD2 は、S1R72005B00A100 より変更が生じた端子です。

## 4. 端子配置図

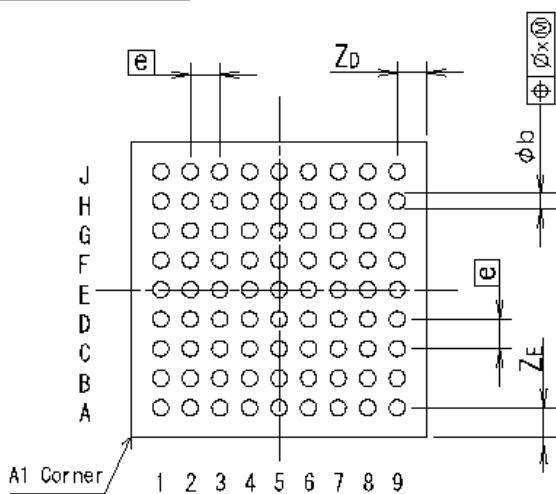

### 4.2 QFP パッケージ

※READYxWAIT および HVDD、HVDD2 は、S1R72005B00A100 より変更が生じた端子です。

## 5. 端子機能説明

### 5.1 CPU インタフェース

| 記号                                                                                                                 | 端子名称             | 端子番号                                                                                         |                                                                                           | 端子種類                    | 機能説明                                                                                      |

|--------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------|

|                                                                                                                    |                  | CSP                                                                                          | QFP                                                                                       |                         |                                                                                           |

| DMASTRB                                                                                                            | DMA Strobe       | E7                                                                                           | 39                                                                                        | I(Gated CMOS)           | バースト DMA 転送用のストローブ信号<br>未使用時は GND(HVSS)に接続                                                |

| xDREQ                                                                                                              | DMA Request      | E9                                                                                           | 41                                                                                        | O(3-state 3mA)          | DMA 転送要求<br>初期状態は HiZ<br>レジスタ設定によりロー・アクティブ／ハイ・アクティブが選択可能                                  |

| xDACK                                                                                                              | DMA Acknowledge  | D9                                                                                           | 42                                                                                        | I (Gated CMOS)          | DMA 転送許可                                                                                  |

| xRD                                                                                                                | Read Strobe      | D8                                                                                           | 43                                                                                        | I (Gated CMOS)          | CPU リードストローブ                                                                              |

| xWR                                                                                                                | Write Strobe     | D7                                                                                           | 44                                                                                        | I (Gated CMOS)          | CPU ライトストローブ                                                                              |

| xCS                                                                                                                | Chip Select      | B8                                                                                           | 45                                                                                        | I(CMOS)                 | チップセレクト信号                                                                                 |

| xINT                                                                                                               | Interrupt signal | C9                                                                                           | 46                                                                                        | O(3-state 3mA)          | CPU への割り込み信号<br>初期状態は HiZ<br>レジスタ設定により HiZ／0、1／0 が選択可能                                    |

| xWAIT                                                                                                              | Wait signal      | C8                                                                                           | 47                                                                                        | O(3-state 3mA)          | CPU へのウェイト信号<br>初期状態は HiZ<br>レジスタ設定により HiZ／0、1／0 が選択可能                                    |

| READYxWAIT                                                                                                         | ReadySelect      | H2                                                                                           | 13                                                                                        | I(CMOS シュミット)           | xWAIT 信号を READY モードで使用する場合に "H" を入力する。初期設定端子であり、動作中に変化させてはならない。                           |

| CD15<br>CD14<br>CD13<br>CD12<br>CD11<br>CD10<br>CD9<br>CD8<br>CD7<br>CD6<br>CD5<br>CD4<br>CD3<br>CD2<br>CD1<br>CD0 | CPU Data         | B7<br>A7<br>C7<br>A6<br>B6<br>C5<br>B5<br>A5<br>B4<br>C4<br>B2<br>A3<br>B3<br>B1<br>C2<br>C1 | 50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>59<br>60<br>61<br>62<br>63<br>1<br>2<br>3 | I/O<br>(Gated CMOS 3mA) | CPU データバス<br>初期状態は入力モード<br>リード時には、レジスタデータが出力され、ライト時には、CPU によりレジスタデータを設定する<br>DMA データバスと共用 |

| CA7<br>CA6<br>CA5<br>CA4<br>CA3<br>CA2<br>CA1<br>CA0                                                               | CPU Address      | D1<br>D2<br>E3<br>E2<br>E1<br>F1<br>F2<br>F3                                                 | 5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                   | I(Gated CMOS)           | CPU アドレスバス。<br>レジスタアドレスを指定する                                                              |

## 5. 端子機能説明

---

### 5.2 USB インタフェース

| 記号        | 端子名称         | 端子番号 |     | 端子種類                          | 機能説明                                                                            |

|-----------|--------------|------|-----|-------------------------------|---------------------------------------------------------------------------------|

|           |              | CSP  | QFP |                               |                                                                                 |

| VBUSDRV3  | VBUS Drive   | H1   | 16  | O (3mA)                       | VBUS3.3V ドライブのイネーブル<br>0 : ディセーブル、1 : イネーブル<br>初期状態はディセーブル<br>未使用時はオープン         |

| VBUSDRV5  | VBUS Drive   | J2   | 17  | O (3mA)                       | VBUS5V ドライブ(max 8mA)のイネーブル<br>0 : ディセーブル、1 : イネーブル<br>初期状態はディセーブル               |

| BUSPWRSEL | VBUS Drive   | H3   | 18  | O (3mA)                       | VBUS5V ドライブ(over 8mA)のイネーブル<br>0 : ディセーブル、1 : イネーブル<br>初期状態はディセーブル              |

| COMPIN10  | 1.0V レベル検出信号 | D6   | —   | I(CMOS 120KΩ pull down 付)     | VBUS/2 レベル検出結果(1.0V)<br>0 : VBUS/2<1.0V、1 : VBUS/2≥1.0V<br>内蔵コンパレータ使用時は GND に接続 |

| COMPIN22  | 2.2V レベル検出信号 | E6   | —   | I(CMOS 120KΩ pull down 付)     | VBUS/2 レベル検出結果(2.2V)<br>0 : VBUS/2<2.2V、1 : VBUS/2≥2.2V<br>内蔵コンパレータ使用時は GND に接続 |

| DM        | USB 負極信号     | J4   | 21  | I/O (special)                 | USB データライン D-                                                                   |

| DP        | USB 正極信号     | H4   | 22  | I/O (special)                 | USB データライン D+                                                                   |

| RPDEN     | Rpd Enable   | J5   | 24  | O (3mA)                       | D+プルダウンのイネーブル<br>0 : ディセーブル、1 : イネーブル<br>内蔵抵抗使用時はオープン                           |

| xRPUEN    | Rpu Enable   | F5   | 25  | O (3mA)                       | D+プルアップのイネーブル<br>0 : イネーブル、1 : ディセーブル<br>内蔵抵抗使用時はオープン                           |

| ID        | ID 信号        | J6   | 26  | I(CMOS シュミット 120KΩ pull up 付) | ID 信号<br>0 : A-Device、1 : B-Device                                              |

| VBUSHF    | VBUS/2       | J3   | 19  | I (special)                   | VBUS/2 レベル<br>外部コンパレータ使用時は GND に接続                                              |

### 5.3 システム系

| 記号                 | 端子名称       | 端子番号     |          | 端子種類                             | 機能説明                                                                                                                                   |

|--------------------|------------|----------|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                    |            | CSP      | QFP      |                                  |                                                                                                                                        |

| XO                 | 発振子出力      | H7       | 31       | O (special)                      | 内部発振回路用出力<br>未使用時はオープン                                                                                                                 |

| XI                 | 発振子入力      | J8       | 32       | I (special)                      | 内部発振回路用入力<br>未使用時は、プルダウン抵抗を介して GND(LVSS)に接続                                                                                            |

| CLKSEL1<br>CLKSEL0 | クロック選択     | G7<br>F9 | 36<br>37 | I(CMOS シュミット)                    | 発振子使用および外部クロック使用の選択端子<br>CLKSEL[1:0]<br>00 : 12MHz 発振子使用<br>01 : 外部 27MHz クロック入力使用<br>10 : 外部 48MHz クロック入力使用<br>11 : 外部 12MHz クロック入力使用 |

| CLKIN              | 外部クロック入力   | F8       | 38       | I(TTL)                           | 外部クロック入力。<br>未使用時は、GND(HVSS)に接続<br>外部クロック入力使用時は、リセット解除までに安定したクロック供給を行っていること                                                            |

| XRESET             | Chip reset | E8       | 40       | I(CMOS シュミット<br>120KΩ pull up 付) | チップリセット                                                                                                                                |

### 5.4 テスト信号

| 記号                   | 端子名称        | 端子番号           |                | 端子種類                                | 機能説明                                                                           |

|----------------------|-------------|----------------|----------------|-------------------------------------|--------------------------------------------------------------------------------|

|                      |             | CSP            | QFP            |                                     |                                                                                |

| TIN2<br>TIN1<br>TIN0 | Test mode   | H6<br>G6<br>H8 | 27<br>28<br>29 | I (CMOS シュミット<br>120KΩ pull down 付) | モード設定入力端子<br>000 : Normal<br>その他 : Internal test mode<br>通常使用時は GND(HVSS)に接続する |

| TSTEN                | Test enable | G1             | 14             | I (TEST I/O)                        | テストイネーブル端子<br>0 : Normal、1 : Test<br>通常使用時は GND(HVSS)に接続する                     |

| ATPGEN               | Test ATPG   | G2             | 15             | I (CMOS シュミット<br>120KΩ pull down 付) | テスト端子<br>通常使用時は GND(HVSS)に接続する                                                 |

| SCANEN               | Test SCAN   | G8             | 34             | I (CMOS シュミット<br>120KΩ pull down 付) | テスト端子<br>通常使用時は GND(HVSS)に接続する                                                 |

## 5. 端子機能説明

### 5.5 電源・GND・その他

| 記号    | 端子名称                        | 端子番号                                                                                                        |           | 端子種類 | 機能説明                    |

|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------|-----------|------|-------------------------|

|       |                             | CSP                                                                                                         | QFP       |      |                         |

| HVDD  | Power Supply for I/O Part   | C3,<br>B9                                                                                                   | 4,<br>48  | P    | I/O 用 2.8~3.3V 電源端子     |

| HVDD2 | Power Supply for USB Part   | G3                                                                                                          | 20        | P    | USB インターフェース用 3.3V 電源端子 |

| HVSS  | Ground for I/O Part         | H5,<br>A8                                                                                                   | 23,<br>49 | P    | I/O 用接地端子               |

| LVDD  | Power Supply for Logic part | J7,<br>A4                                                                                                   | 30,<br>58 | P    | 内部用 2.5V 電源端子           |

| LVSS  | Ground for Logic part       | H9,<br>A2                                                                                                   | 33,<br>64 | P    | 内部用接地端子                 |

| NC    | None Connect                | C6,<br>D3,<br>D4,<br>D5,<br>E4,<br>E5,<br>F4,<br>F6,<br>F7,<br>G4,<br>G5,<br>G9,<br>A1,<br>A9,<br>J1,<br>J9 | 35        | —    | 未使用端子<br>通常使用時はオープン     |

※READYxWAIT および HVDD、HVDD2 は、S1R72005B00A100 より変更が生じた端子です。

### 6. 機能概要

#### 6.1 Host Controller (HC)

- 複数トランザクション間の調停、フレームにおける時間管理、転送のスケジューリング、および再送の管理を行います。

- トランザクション管理を行います。

- パケットを生成／分解します。

- サスPEND／レジューム／リセット状態生成の指示を行います。

#### 6.2 Peripheral Controller (PC)

- エンドポイントのオペレーション情報をレジスタを介して管理します。

- トランザクション管理を行います。

- パケットを生成／分解します。

- リモートウェイクアップ信号生成の指示を行います。

#### 6.3 OTG Controller

- USB データライン状態（コネクト／ディスコネクトを含む）を監視します。

- VBUS レベルを監視します。

- ID を監視します。

- OTG 動作を実施するための VBUS 駆動／停止、プルアップ／プルダウン抵抗 (D+) 接続／切断、HC／PC のイネーブル／ディセーブルを制御します。

#### 6.4 HC/PC Common

- USB データライン状態生成の指示を行います。

- USB Transceiver に対し、HC または PC との接続切替を行います。

#### 6.5 USB Transceiver

- パラレル／シリアル変換処理を行います。

- ビットスタッフィング／アンスタッフィング処理を行います。

- NRZI エンコード／デコード 処理を行います。

- USB データ信号の送受信を行います。

- USB データライン状態を生成します。

#### 6.6 Control Registers

- トランザクションおよびエンドポイントの制御に関するレジスタ群を保有します。

## 6. 機能概要

---

### 6.7 FIFO Manager

- CPU/DMA、USB による FIFO アクセス用アドレスを管理します。

- CPU/DMA、USB による FIFO アクセスのアビトレーションを管理します。

### 6.8 FIFO SRAM

- データ転送用 FIFO（計 2.5kByte）として使用します。

### 6.9 CPU I/F

- PIO 転送の制御を行います。

- CPU へのインターフェト信号を生成します。

### 6.10 DMA Handler

- DMA 転送（DMA スレーブ）の制御を行います。

-

### 6.11 CLK Controller

- 通常 PLL（発振子使用時）により、または外部からの入力クロックにより、内部で使用する各種クロックを生成します。

- ブロック毎に使用するクロック動作の制御を行います。

### 6.12 Test Module

- 内部の動作確認テストを行います。

## 7. 電氣的特性

### 7.1 絶対最大定格

| (VSS=0V) |       |                |    |

|----------|-------|----------------|----|

| 項目       | 記号    | 定格値            | 単位 |

| 電源電圧     | HVDD* | -0.3~4.0       | V  |

|          | HVDD2 | -0.3~4.0       | V  |

|          | LVDD* | -0.3~3.0       | V  |

| 入力電圧     | HVI1  | -0.3~HVDD+0.5  | V  |

|          | HVI2  | -0.3~HVDD2+0.5 | V  |

|          | LVI   | -0.3~LVDD+0.5  | V  |

| 出力電圧     | HVO1  | -0.3~HVDD+0.5  | V  |

|          | HVO2  | -0.3~HVDD2+0.5 | V  |

|          | LVO   | -0.3~LVDD+0.5  | V  |

| 出力電流／端子  | IOUT  | ±30            | mA |

| 保存温度     | Tstg  | -65~150        | °C |

\*HVDD2、 HVDD  $\geq$  LVDD

### 7.2 推奨動作条件

| 項目   | 記号    | MIN  | TYP  | MAX  | 単位 |

|------|-------|------|------|------|----|

| 電源電圧 | HVDD2 | 3.00 | 3.30 | 3.60 | V  |

|      | HVDD  | 2.70 | —    | 3.60 | V  |

|      | LVDD  | 2.30 | 2.50 | 2.70 | V  |

| 入力電圧 | HVI1  | VSS  | —    | HVDD | V  |

|      | HVI2  | VSS  | —    | HVDD | V  |

|      | LVI   | VSS  | —    | LVDD | V  |

| 周囲温度 | Ta    | -40  | 25   | 85   | °C |

## 7. 電気的特性

### 7.3 DC 特性

DC 特性(推奨動作条件による) (1)

| 項目                      | 記号     | 条件                                                                                                                        | Min. | Typ. | Max. | 単位      |

|-------------------------|--------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

| 消費電流                    |        |                                                                                                                           |      |      |      |         |

| 電源電流                    | IDDH   | HVDD = 3.6V                                                                                                               | -    | -    | 10   | mA      |

|                         | IDDH2  | HVDD2 = 3.6V                                                                                                              | -    | -    | 10   | mA      |

|                         | IDDL   | LVDD = 2.7V                                                                                                               | -    | -    | 40   | mA      |

| 静止電流 (HVDD~VSS 間の静止電流)  |        |                                                                                                                           |      |      |      |         |

| 電源電流                    | IDDSH  | VIN = HVDD or<br>HVDD2 or VSS<br><br>HVDD = 3.6V<br>LVDD = 2.7V                                                           | -    | -    | 30   | $\mu$ A |

| 静止電流 (HVDD2~VSS 間の静止電流) |        |                                                                                                                           |      |      |      |         |

| 電源電流                    | IDDSH2 | VIN = HVDD or<br>HVDD2 or VSS<br><br>HVDD2 = 3.6V<br>LVDD = 2.7V                                                          | -    | -    | 30   | $\mu$ A |

| 静止電流 (LVDD~VSS 間の静止電流)  |        |                                                                                                                           |      |      |      |         |

| 電源電流                    | IDDSL  | VIN = HVDD or<br>HVDD2 or VSS<br><br>HVDD = 3.6V<br>LVDD = 2.7V                                                           | -    | -    | 60   | $\mu$ A |

| 入力リーク                   |        |                                                                                                                           |      |      |      |         |

| 入力リーク電流                 | IL     | VIN = HVDD or<br>HVDD2 or VSS<br><br>HVDD = 3.6V<br>HVDD = 3.6V<br>LVDD = 2.7V<br>HVIH = HVDD<br>LVIL = LVDD<br>VIL = VSS | -5   | -    | 5    | $\mu$ A |

DC 特性(推奨動作条件による) (2)

| 項目                 | 記号       | 条件                                                                            | Min. | Typ. | Max. | 単位 |

|--------------------|----------|-------------------------------------------------------------------------------|------|------|------|----|

| 入力特性 (CMOS)        | 端子名 :    | CA7..CA0, CD15..CD0, TSTEN, xCS, xDACK, xRD, xWR, DMASTRB, COMPIN10, COMPIN22 |      |      |      |    |

| "H"レベル入力電圧         | VIH1H    | HVDD = 3.6V                                                                   | 2.2  | -    | -    | V  |

| "L"レベル入力電圧         | VIL1H    | HVDD = 2.7V                                                                   | -    | -    | 0.8  | V  |

| シュミット入力特性 (CMOS)   | 端子名 :    | xRESET, CLKSEL1, CLKSEL0, TIN2, TIN1, TIN0, SCANEN, ATPGEN                    |      |      |      |    |

| "H"レベルトリガ電圧        | VT1+     | HVDD = 3.6V                                                                   | 1.4  | -    | 2.7  | V  |

| "L"レベルトリガ電圧        | VT1-     | HVDD = 2.7V                                                                   | 0.6  | -    | 1.8  | V  |

| ヒステリシス電圧           | ΔV1      | HVDD = 2.7V                                                                   | 0.3  | -    | -    | V  |

| シュミット入力特性 (CMOS)   | 端子名 :    | ID                                                                            |      |      |      |    |

| "H"レベルトリガ電圧        | VT2+     | HVDD2 = 3.6V                                                                  | 1.4  | -    | 2.7  | V  |

| "L"レベルトリガ電圧        | VT2-     | HVDD2 = 3.0V                                                                  | 0.6  | -    | 1.8  | V  |

| ヒステリシス電圧           | ΔV2      | HVDD2 = 3.0V                                                                  | 0.3  | -    | -    | V  |

| 入力特性 (LVTT)        | 端子名 :    | CLKIN                                                                         |      |      |      |    |

| "H"レベル入力電圧         | VIH2H    | HVDD = 3.6V                                                                   | 2.0  | -    | -    | V  |

| "L"レベル入力電圧         | VIL2H    | HVDD = 2.7V                                                                   | -    | -    | 0.8  | V  |

| シュミット入力特性 (USB:FS) | 端子名 :    | DP, DM                                                                        |      |      |      |    |

| "H"レベルトリガ電圧        | VT+(USB) | HVDD2 = 3.6V                                                                  | 1.1  | -    | 1.8  | V  |

| "L"レベルトリガ電圧        | VT-(USB) | HVDD2 = 3.0V                                                                  | 1.0  | -    | 1.5  | V  |

| ヒステリシス電圧           | ΔV(USB)  | HVDD2 = 3.0V                                                                  | 0.1  | -    | -    | V  |

| 入力特性 (USB:FS 差動入力) | 端子名 :    | DP, DM のペア                                                                    |      |      |      |    |

| 差動入力の感度            |          | HVDD2 = 3.0V                                                                  |      |      |      |    |

|                    | VDS(USB) | 差動入力電圧<br>0.8V~2.5V                                                           | -    | -    | 0.2  | V  |

| 入力プルアップ特性          | 端子名 :    | xRESET                                                                        |      |      |      |    |

| プルアップ抵抗値           | RP2      | HVDD = 3.3V                                                                   | 60   | 120  | 288  | kΩ |

|                    |          | VIH = VSS                                                                     |      |      |      |    |

| 入力プルアップ特性          | 端子名 :    | ID                                                                            |      |      |      |    |

| プルアップ抵抗値           | RP2      | HVDD2 = 3.3V<br>VIH = VSS                                                     | 60   | 120  | 288  | kΩ |

| 入力プルダウン特性          | 端子名 :    | SCANEN, ATPGEN, TIN2, TIN1, TIN0, COMPIN10, COMPIN22                          |      |      |      |    |

| プルダウン抵抗値           | RPD2     | HVDD = 3.3V<br>VIH = VSS                                                      | 60   | 120  | 288  | kΩ |

## 7. 電気的特性

DC 特性(推奨動作条件による) (3)

| 項目              | 記号       | 条件                                                                          | MIN     | TYP | MAX | 単位      |

|-----------------|----------|-----------------------------------------------------------------------------|---------|-----|-----|---------|

| 出力特性            | 端子名 :    | CD15..CD0, xINT, xWAIT, xDREQ                                               |         |     |     |         |

| "H" レベル出力電圧     | VOH1H    | HVDD = 2.7V<br>IOH = -3mA                                                   | VDD-0.4 | -   | -   | V       |

| "L" レベル出力電圧     | VOL1H    | HVDD = 2.7V<br>IOL = 3mA                                                    | -       | -   | 0.4 | V       |

| 出力特性            | 端子名 :    | xRPUEN, RPDEN, VBUSDRV3, VBUSDRV5, BUSPWRSEL                                |         |     |     |         |

| "H" レベル出力電圧     | VOH1H    | HVDD = 3.0V<br>IOH = -3mA                                                   | VDD-0.4 | -   | -   | V       |

| "L" レベル出力電圧     | VOL1H    | HVDD = 3.0V<br>IOL = 3mA                                                    | -       | -   | 0.4 | V       |

| 出力特性 (USB:FS)   | 端子名 :    | DP, DM                                                                      |         |     |     |         |

| "H" レベル出力電圧     | VOH(USB) | HVDD = 3.0V                                                                 | 2.8     | -   | -   | V       |

| "L" レベル出力電圧     | VOL(USB) | HVDD = 3.6V                                                                 | -       | -   | 0.3 | V       |

| 出力特性            | 端子名 :    | xRPUEN, RPDEN, VBUSDRV3, VBUSDRV5, BUSPWRSEL, CD15..CD0, xINT, xWAIT, xDREQ |         |     |     |         |

| OFF-STATE リーク電流 | IOZ1H    | HVDD = 3.6V<br>VOH = VDD<br>VOL = VSS                                       | -5      | -   | 5   | $\mu$ A |

| 端子容量            | 端子名 :    | 全入力端子                                                                       |         |     |     |         |

| 入力端子容量          | CI       | f = 1MHz<br>VDD = VSS                                                       | -       | -   | 8   | pF      |

| 端子容量            | 端子名 :    | 全出力端子                                                                       |         |     |     |         |

| 出力端子容量          | CO       | f = 1MHz<br>VDD = VSS                                                       | -       | -   | 8   | pF      |

| 端子容量            | 端子名 :    | 全入出力端子                                                                      |         |     |     |         |

| 入出力端子容量         | CIO      | f = 1MHz<br>VDD = VSS                                                       | -       | -   | 8   | pF      |

## 7.4 AC 特性

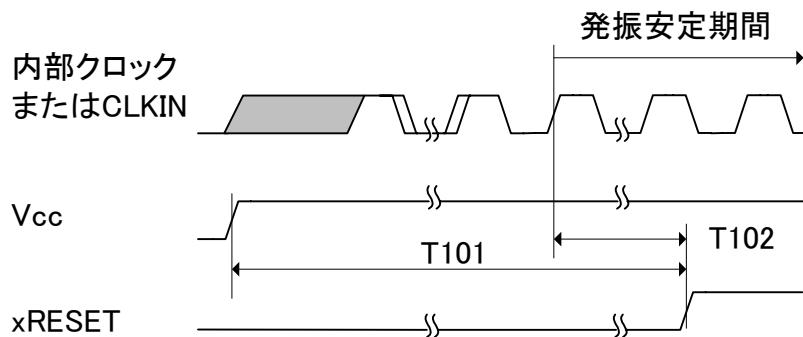

### 7.4.1 クロックタイミング

#### 7.4.1.1 パワーオン発振安定時間

| 記号   | 説明              | min | typ | max | 単位 |

|------|-----------------|-----|-----|-----|----|

| T101 | パワーオン発振安定時間     | 10  | -   | -   | ms |

| T102 | XRESET セットアップ時間 | 200 | -   | -   | us |

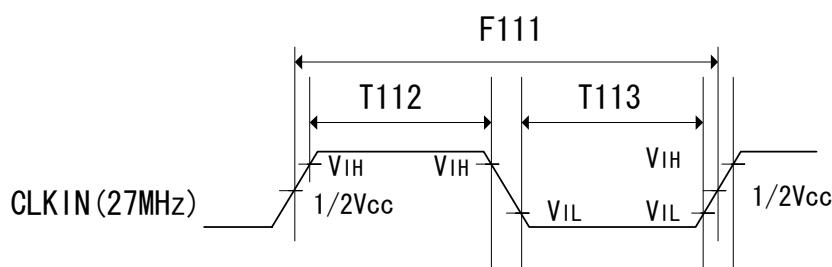

#### 7.4.1.2 CLKIN(27MHz)クロック入力タイミング

| 記号   | 説明                  | min    | typ    | max    | 単位  |

|------|---------------------|--------|--------|--------|-----|

| F111 | クロック入力周波数           | 26.933 | 27.000 | 27.068 | MHz |

| T112 | クロック入力 High レベルパルス幅 | 12     | -      | 23     | ns  |

| T113 | クロック入力 Low レベルパルス幅  | 12     | -      | 23     | ns  |

## 7. 電気的特性

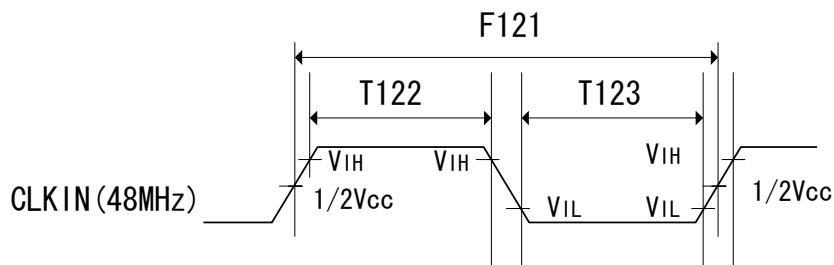

### 7.4.1.3 CLKIN(48MHz) クロック入力タイミング

| 記号   | 説明                  | min    | typ | max    | 単位  |

|------|---------------------|--------|-----|--------|-----|

| F121 | クロック入力周波数(中心周波数)    | 47.880 | 48  | 48.120 | MHz |

| T122 | クロック入力 High レベルパルス幅 | 7      | -   | 13     | ns  |

| T123 | クロック入力 Low レベルパルス幅  | 7      | -   | 13     | ns  |

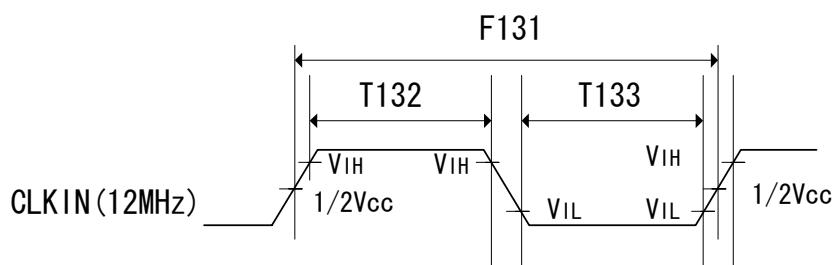

### 7.4.1.4 CLKIN(12MHz) クロック入力タイミング

| 記号   | 説明                  | min    | typ    | max    | 単位  |

|------|---------------------|--------|--------|--------|-----|

| F131 | クロック入力周波数 (中心周波数)   | 11.970 | 12.000 | 12.030 | MHz |

| T132 | クロック入力 High レベルパルス幅 | 28     | -      | 52     | ns  |

| T133 | クロック入力 Low レベルパルス幅  | 28     | -      | 52     | ns  |

### 7.4.2 CPU I/F アクセス タイミング

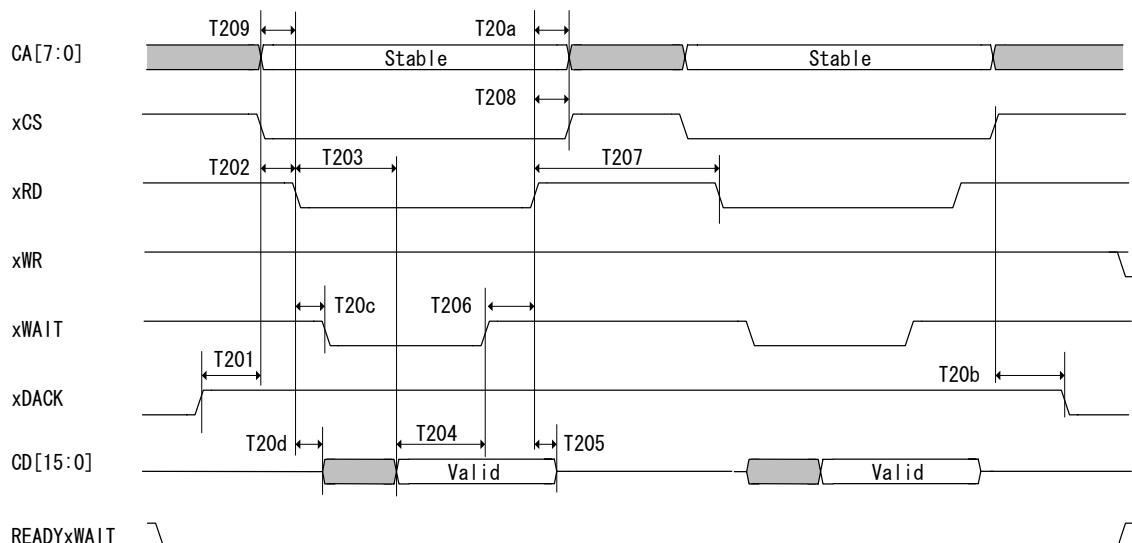

#### 7.4.2.1 リード タイミング（外部 xWAIT モード）

| 記号   | 説明                             | min | typ | max  | 単位 |

|------|--------------------------------|-----|-----|------|----|

| T201 | xDACK ネゴートに対する xCS アサート時間      | 10  | -   | -    | ns |

| T202 | xCS アサートに対する xRD アサート時間        | 0   | -   | -    | ns |

| T203 | xRD アサートに対する CD 有効データ遅延時間(注 1) | -   | -   | 62.5 | ns |

| T204 | CD 出力に対する xWAIT ネゴート時間         | 20  | -   | -    | ns |

| T205 | xRD ネゴートに対する CD 出力ホールド時間       | 2.5 | -   | -    | ns |

| T206 | xWAIT ネゴートに対する xRD ネゴート時間      | 0   | -   | -    | ns |

| T207 | xRD ネゴート期間                     | 25  | -   | -    | ns |

| T208 | xRD ネゴートに対する xCS ネゴート時間        | 0   | -   | -    | ns |

| T209 | xRD アサートに対する CA セットアップ時間       | 0   | -   | -    | ns |

| T20a | xRD ネゴートに対する CA ホールド時間         | 0   | -   | -    | ns |

| T20b | xCS ネゴートに対する xDACK アサート時間      | 10  | -   | -    | ns |

| T20c | xRD アサートに対する xWAIT アサート時間      | -   | -   | 8    | ns |

| T20d | xRD アサートに対する CD 出力遅延時間         | -   | -   | 8    | ns |

(注 1)

通常レジスタアクセス時の規定 (FIFO forCPU レジスタへのアクセス時を除く) です。

FIFO forCPU レジスタへのアクセス時は、内蔵 FIFO メモリへのアクセス競合の状況より、データ出力までの時間が伸びます。

## 7. 電気的特性

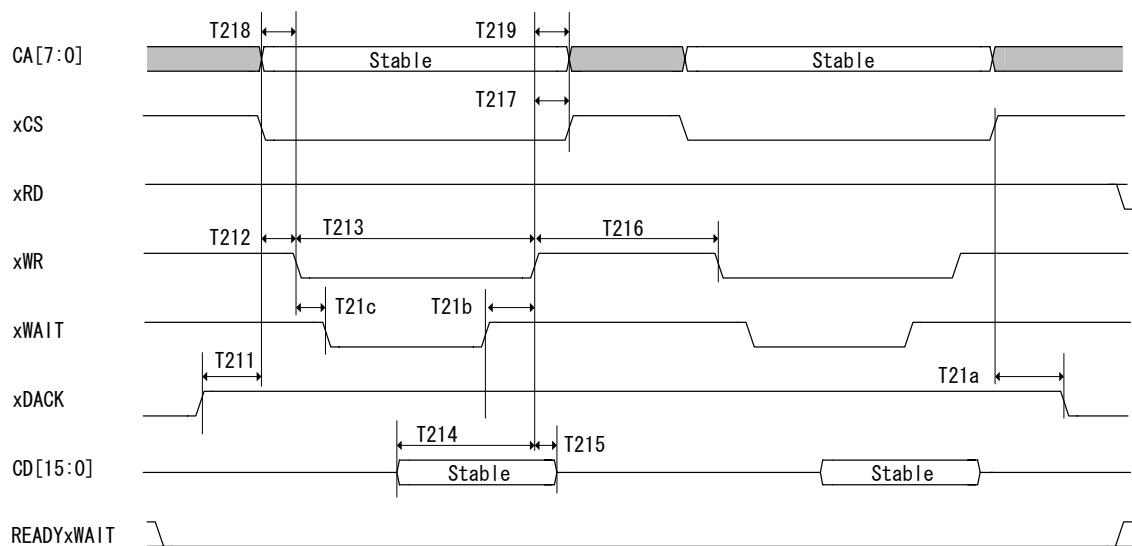

### 7.4.2.2 ライト タイミング (外部 xWAIT モード)

| 記号   | 説明                             | min | typ | max | 単位 |

|------|--------------------------------|-----|-----|-----|----|

| T211 | xDACK ネガートに対する xCS アサート時間      | 10  | -   | -   | ns |

| T212 | xCS アサートに対する xWR アサート時間        | 0   | -   | -   | ns |

| T213 | xWR アサートパルス幅                   | 32  | -   | -   | ns |

| T214 | xWR ネガートに対する CD セットアップ時間       | 10  | -   | -   | ns |

| T215 | xWR ネガートに対する CD ホールド時間         | 0   | -   | -   | ns |

| T216 | xWR ネガート期間                     | 25  | -   | -   | ns |

| T217 | xWR ネガートに対する xCS ネガート時間        | 0   | -   | -   | ns |

| T218 | xWR アサートに対する CA セットアップ時間       | 0   | -   | -   | ns |

| T219 | xWR ネガートに対する CA ホールド時間         | 0   | -   | -   | ns |

| T21a | xCS ネガートに対する xDACK アサート時間      | 10  | -   | -   | ns |

| T21b | xWAIT ネガートに対する xWR ネガート時間      | 0   | -   | -   | ns |

| T21c | xWR アサートに対する xWAIT アサート時間(注 2) | -   | -   | 8   | ns |

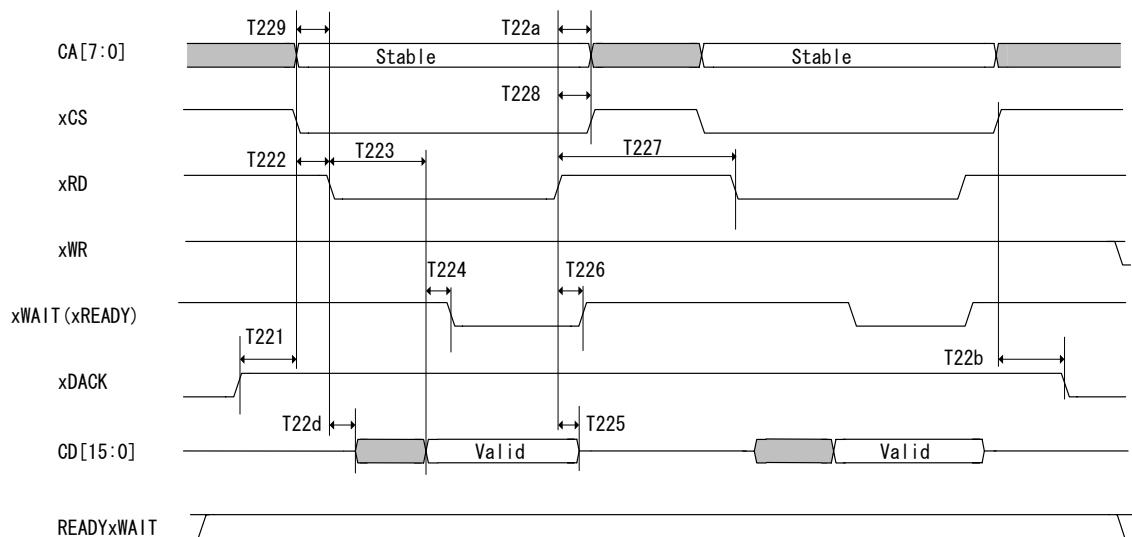

## 7.4.2.3 リード タイミング (外部 xREADY モード)

| 記号   | 説明                             | min | typ | max  | 単位 |

|------|--------------------------------|-----|-----|------|----|

| T221 | xDACK ケーブルに対する xCS アサート時間      | 10  | -   | -    | ns |

| T222 | xCS アサートに対する xRD アサート時間        | 0   | -   | -    | ns |

| T223 | xRD アサートに対する CD 有効データ遅延時間(注 1) | -   | -   | 62.5 | ns |

| T224 | CD 出力に対する xREADY アサート時間        | 15  | -   | -    | ns |

| T225 | xRD ケーブルに対する CD 出力ホールド時間       | 2.5 | -   | -    | ns |

| T226 | xRD ケーブルに対する xREADY ケーブル時間     |     | -   | 8    | ns |

| T227 | xRD ケーブル期間                     | 25  | -   | -    | ns |

| T228 | xRD ケーブルに対する xCS ケーブル時間        | 0   | -   | -    | ns |

| T229 | xRD アサートに対する CA セットアップ時間       | 0   | -   | -    | ns |

| T22a | xRD ケーブルに対する CA ホールド時間         | 0   | -   | -    | ns |

| T22b | xCS ケーブルに対する xDACK アサート時間      | 10  | -   | -    | ns |

| T22c | -                              | -   | -   | -    | ns |

| T22d | xRD アサートに対する CD 出力遅延時間         | -   | -   | 8    | ns |

(注 1)

通常レジスタアクセス時の規定 (FIFO forCPU レジスタへのアクセス時を除く) です。

FIFO forCPU レジスタへのアクセス時は、内蔵 FIFO メモリへのアクセス競合の状況より、データ出力までの時間が伸びます。

## 7. 電気的特性

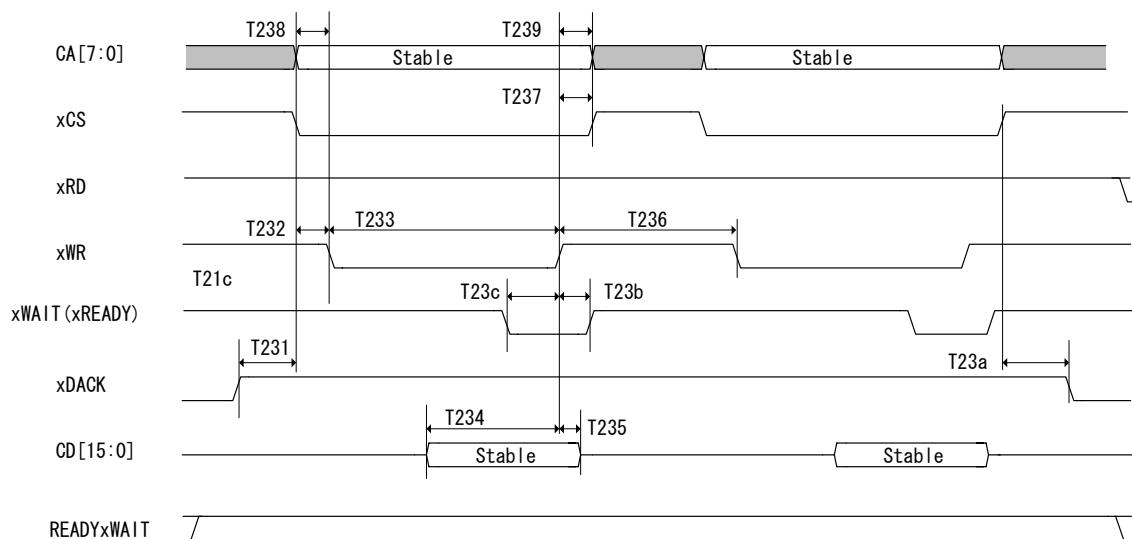

### 7.4.2.4 ライト タイミング（外部 xREADY モード）

| 記号   | 説明                        | min | typ | max | 単位 |

|------|---------------------------|-----|-----|-----|----|

| T231 | xDACK エッジに対する xCS アサート時間  | 10  | -   | -   | ns |

| T232 | xCS アサートに対する xWR アサート時間   | 0   | -   | -   | ns |

| T233 | xWR アサートパルス幅              | 32  | -   | -   | ns |

| T234 | xWR エッジに対する CD セットアップ時間   | 10  | -   | -   | ns |

| T235 | xWR エッジに対する CD ホールド時間     | 0   | -   | -   | ns |

| T236 | xWR エッジ期間                 | 25  | -   | -   | ns |

| T237 | xWR エッジに対する xCS エッジ時間     | 0   | -   | -   | ns |

| T238 | xWR アサートに対する CA セットアップ時間  | 0   | -   | -   | ns |

| T239 | xWR エッジに対する CA ホールド時間     | 0   | -   | -   | ns |

| T23a | xCS エッジに対する xDACK アサート時間  | 10  | -   | -   | ns |

| T23b | xWR エッジに対する xREADY エッジ時間  | -   | -   | 8   | ns |

| T23c | xREADY アサートに対する xWR エッジ時間 | 0   | -   | -   | ns |

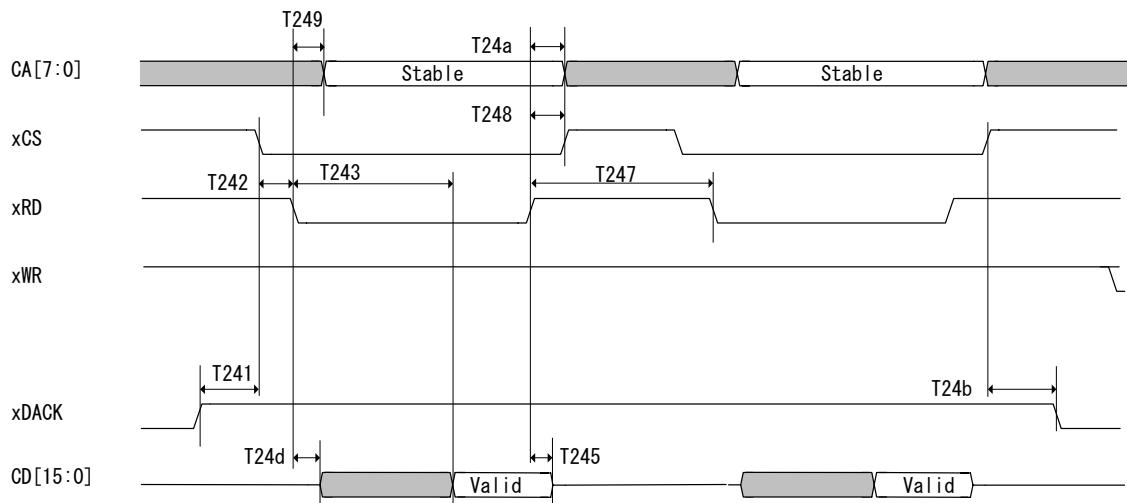

## 7.4.2.5 リード タイミング（固定 WAIT モード）

| 記号   | 説明                          | min | typ | max | 単位 |

|------|-----------------------------|-----|-----|-----|----|

| T241 | xDACK ネゴートに対する xCS アサート時間   | 10  | -   | -   | ns |

| T242 | xCS アサートに対する xRD アサート時間     | 0   | -   | -   | ns |

| T243 | xRD アサートに対する CD 有効データ出力遅延時間 | -   | -   | 110 | ns |

| T244 | -                           | -   | -   | -   | ns |

| T245 | xRD ネゴートに対する CD 出力ホールド時間    | 2.5 | -   | -   | ns |

| T246 | -                           | -   | -   | -   | ns |

| T247 | xRD ネゴート期間                  | 25  | -   | -   | ns |

| T248 | xRD ネゴートに対する xCS ネゴート時間     | 0   | -   | -   | ns |

| T249 | xRD アサートに対する CA 有効遅延時間      | -   | -   | 10  | ns |

| T24a | xRD ネゴートに対する CA ホールド時間      | 0   | -   | -   | ns |

| T24b | xCS ネゴートに対する xDACK アサート時間   | 10  | -   | -   | ns |

| T24c | -                           | -   | -   | -   | ns |

| T24d | xRD アサートに対する CD 出力遅延時間      | -   | -   | 8   | ns |

- 固定 WAIT モードの選択は、S1R72005 の CPUConfig レジスタにて行います。

- 本 LSI はパワーオンリセット後 外部 xWAIT を使用するモードで動作します。

- CPUConfig レジスタへアクセス時は xWAIT が出力されませんので xWAIT を持たない CPU から書きこみできます。

- 外部 WAIT 端子を使用しない場合、CPU は上記のタイミングでアクセス可能なように本デバイスにアクセス時にソフトウェイトを割り当ててください。

## 7. 電気的特性

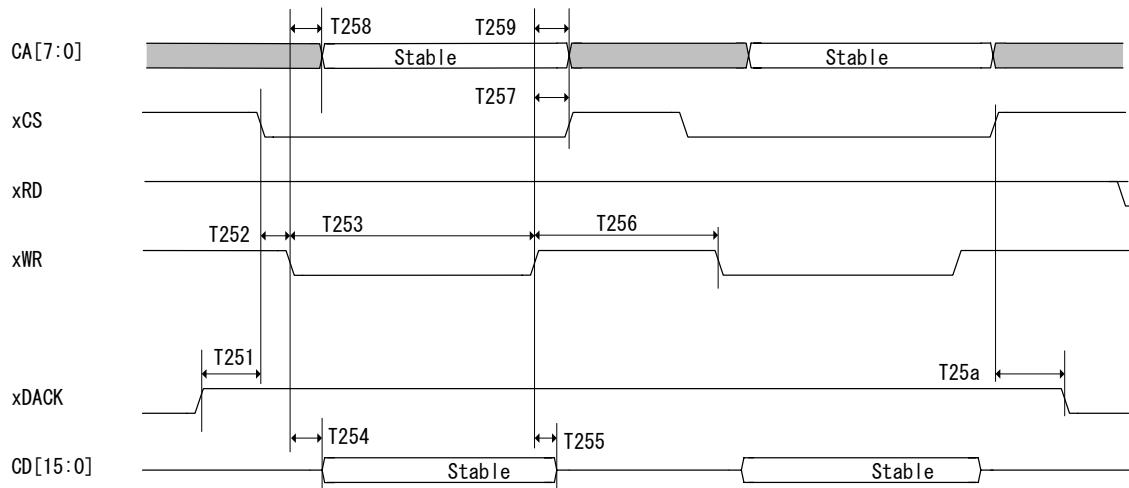

### 7.4.2.6 ライト タイミング (固定 WAIT モード)

| 記号   | 説明                        | min | typ | max | 単位 |

|------|---------------------------|-----|-----|-----|----|

| T251 | xDACK ネゴートに対する xCS アサート時間 | 10  | -   | -   | ns |

| T252 | xCS アサートに対する xWR アサート時間   | 0   | -   | -   | ns |

| T253 | xWR アサートパルス幅              | 110 | -   | -   | ns |

| T254 | xWR アサートに対する CD 有効遅延時間    | -   | -   | 20  | ns |

| T255 | xWR ネゴートに対する CD ホールド時間    | 0   | -   | -   | ns |

| T256 | xWR ネゴート期間                | 25  | -   | -   | ns |

| T257 | xWR ネゴートに対する xCS ネゴート時間   | 0   | -   | -   | ns |

| T258 | xWR アサートに対する CA 有効遅延時間    | 0   | -   | -   | ns |

| T259 | xWR ネゴートに対する CA ホールド時間    | 0   | -   | -   | ns |

| T25a | xCS ネゴートに対する xDACK アサート時間 | 10  | -   | -   | ns |

- ・固定 WAIT モードの選択は、S1R72005 の CPUConfig レジスタにて行います。

- ・本 LSI はパワーオンリセット後 外部 xWAIT を使用するモードで動作します。

- ・CPUConfig レジスタへアクセス時は xWAIT が出力されませんので xWAIT を持たない CPU から書きこみできます。

- ・外部 WAIT 端子を使用しない場合、CPU は上記のタイミングでアクセス可能なように本デバイスにアクセス時にソフトウェイトを割り当ててください。

## 7.4.3 DMA タイミング

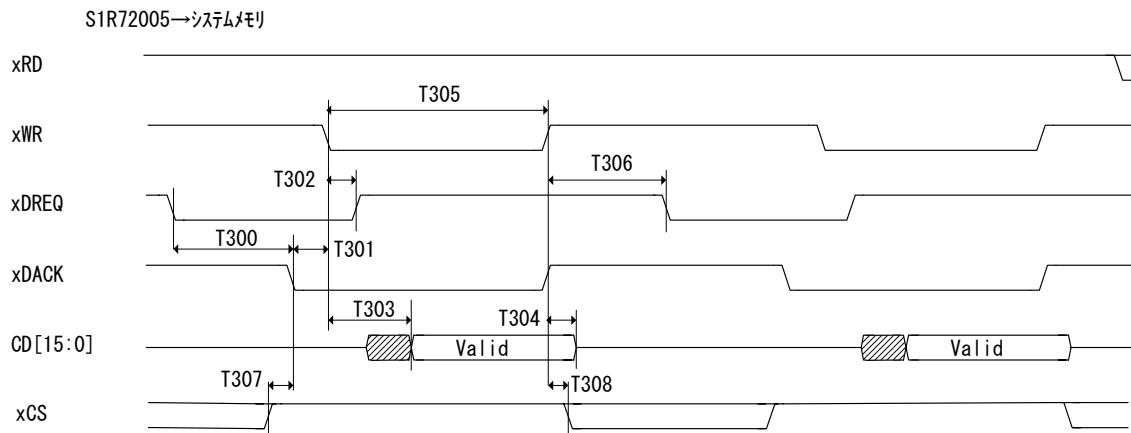

## 7.4.3.1 xRD・xWR ストローブモード(DMAOUT)

| 記号   | 説明                          | min | typ | max | 単位 |

|------|-----------------------------|-----|-----|-----|----|

| T300 | xDREQ アサートに対する xDACK アサート時間 | 0   | -   | -   | ns |

| T301 | xDACK アサートに対する xWR アサート時間   | 0   | -   | -   | ns |

| T302 | xWR アサートに対する xDREQ ネガート時間   | -   | -   | 10  | ns |

| T303 | xWR アサートに対するデータ出力遅延時間       | -   | -   | 8   | ns |

| T304 | xWR ネガートに対するデータホールド時間       | 2   | -   | -   | ns |

| T305 | xWR アサート幅                   | 42  | -   | -   | ns |

| T306 | xWR ネガートに対する xDREQ アサート時間   | 160 | -   | -   | ns |

| T307 | xCS ネガートに対する xDACK アサート時間   | 0   | -   | -   | ns |

| T308 | xDACK ネガートに対する xCS アサート時間   | 0   |     |     | ns |

## 7. 電気的特性

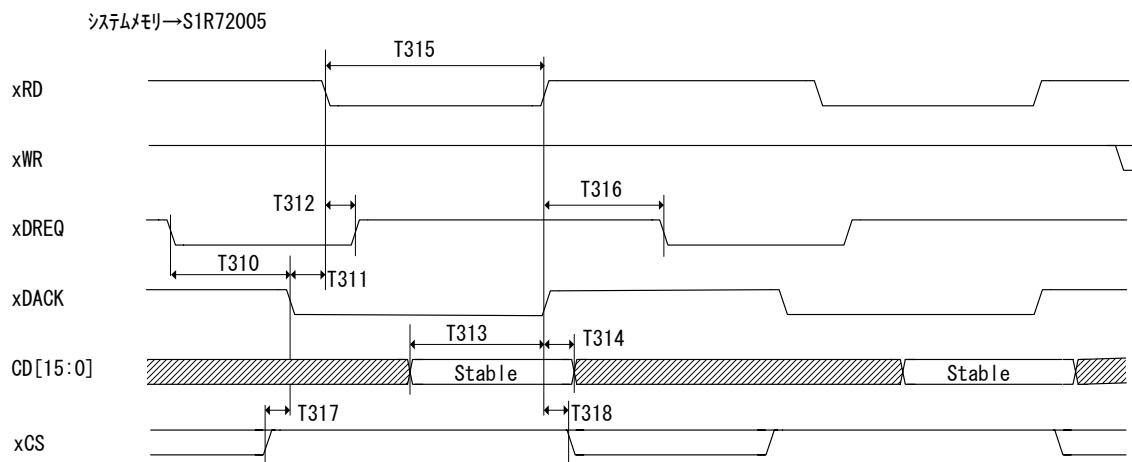

### 7.4.3.2 xRD・xWR ストローブモード(DMAIN)

| 記号   | 説明                          | min | typ | max | 単位 |

|------|-----------------------------|-----|-----|-----|----|

| T310 | xDREQ アサートに対する xDACK アサート時間 | 0   | -   | -   | ns |

| T311 | xDACK アサートに対する xRD アサート時間   | 0   | -   | -   | ns |

| T312 | xRD アサートに対する xDREQ ネガート時間   | -   | -   | 10  | ns |

| T313 | xRD ネガートに対するデータセットアップ時間     | 10  | -   | -   | ns |

| T314 | xRD ネガートに対するデータホールド時間       | 0   | -   | -   | ns |

| T315 | xRD アサートパルス幅                | 42  | -   | -   | ns |

| T316 | xRD ネガートに対する xDREQ アサート時間   | 160 | -   | -   | ns |

| T317 | xCS ネガートに対する xDACK アサート時間   | 0   | -   | -   | ns |

| T318 | xDACK ネガートに対する xCS アサート時間   | 0   | -   | -   | ns |

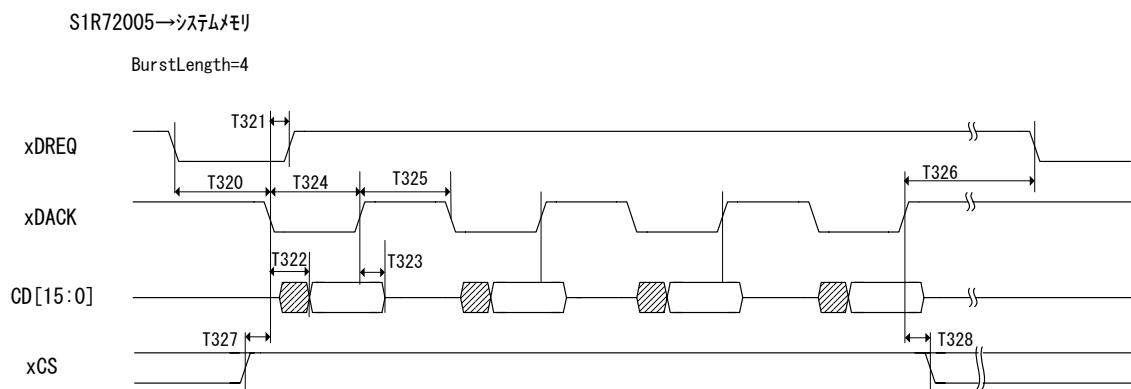

## 7.4.3.3 DACK ストローブモード(DMAOUT)

| 記号   | 説明                          | min | typ | max | 単位 |

|------|-----------------------------|-----|-----|-----|----|

| T320 | xDREQ アサートに対する xDACK アサート時間 | 0   | -   | -   | ns |

| T321 | xDACK アサートに対する xDREQ ネガート時間 | -   | -   | 10  | ns |

| T322 | xDACK アサートに対するデータ出力遅延時間     | -   | -   | 7   | ns |

| T323 | xDACK ネガートに対するデータホールド時間     | 2   | -   | -   | ns |

| T324 | xDACK アサートパルス幅              | 42  | -   | -   | ns |

| T325 | xDACK ネガートパルス幅              | 42  | -   | -   | ns |

| T326 | xDACK ネガートに対する xDREQ アサート時間 | 160 | -   | -   | ns |

| T327 | xCS ネガートに対する xDACK アサート時間   | 0   | -   | -   | ns |

| T328 | xDACK ネガートに対する xCS アサート時間   | 0   | -   | -   | ns |

## 7. 電気的特性

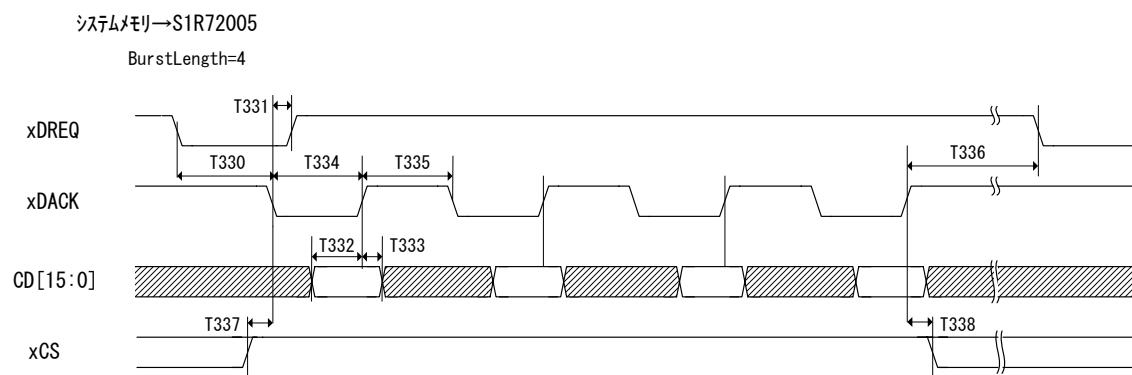

### 7.4.3.4 DACK ストローブモード(DMAIN)

| 記号   | 説明                          | min | typ | max | 単位 |

|------|-----------------------------|-----|-----|-----|----|

| T330 | xDREQ アサートに対する xDACK アサート時間 | 0   | -   | -   | ns |

| T331 | xDACK アサートに対する xDREQ ネガート時間 | -   | -   | 10  | ns |

| T332 | xDACK ネガートに対するデータセットアップ時間   | 10  | -   | -   | ns |

| T333 | xDACK ネガートに対するデータホールド時間     | 0   | -   | -   | ns |

| T334 | xDACK アサートパルス幅              | 42  | -   | -   | ns |

| T335 | xDACK ネガートパルス幅              | 42  | -   | -   | ns |

| T336 | xDACK ネガートに対する xDREQ アサート時間 | 160 | -   | -   | ns |

| T337 | xCS ネガートに対する xDACK アサート時間   | 0   | -   | -   | ns |

| T338 | xDACK ネガートに対する xCS アサート時間   | 0   | -   | -   | ns |

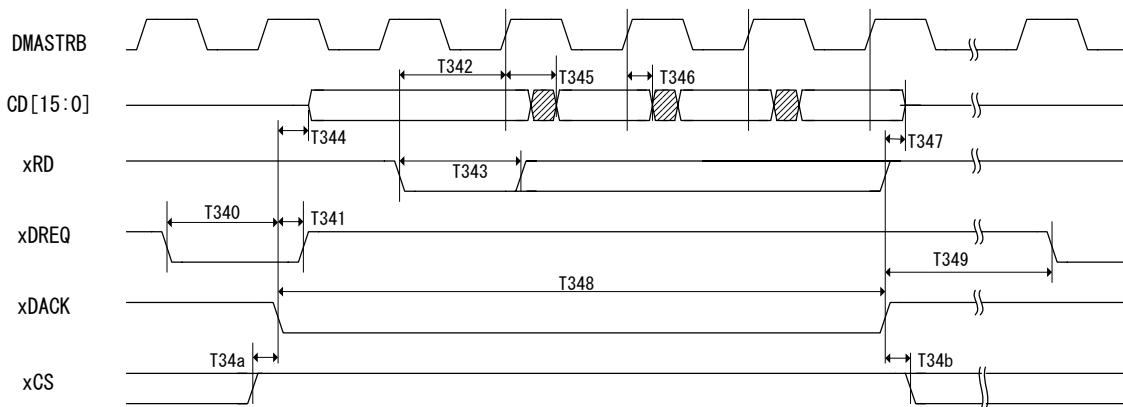

## 7.4.3.5 DMASTRB SDRAM モード(DMAOUT)

S1R72005→システムメモリ (SDRAM)

DOUTLatency =0, BurstLength=4

| 記号   | 説明                                 | min             | typ | max | 単位 |

|------|------------------------------------|-----------------|-----|-----|----|

| T340 | xDREQ アサートに対する xDACK アサート時間        | 0               | -   | -   | ns |

| T341 | xDACK アサートに対する xDREQ ネガート時間        | -               | -   | 10  | ns |

| T342 | xRD(~CAS)アサートに対する DMASTRB 有効エッジ 時間 | 3               | -   | -   | ns |

| T343 | xRD(~CAS)アサートパルス幅                  | 1T<br>(DMASTRB) | -   | -   | ns |

| T344 | xDACK アサートに対するデータ出力遅延時間            | -               | -   | 7   | ns |

| T345 | DMASTRB 有効エッジに対する データ出力遅延時間        | -               | -   | 9   | ns |

| T346 | DMASTRB 有効エッジに対する データホールド時間        | 4               | -   | -   | ns |

| T347 | xDACK ネガートに対するデータホールド時間            | 2               | -   | -   | ns |

| T348 | xDACK アサートパルス幅                     | 42              | -   | -   | ns |

| T349 | xDACK ネガートに対する xDREQ アサート時間        | 160             | -   | -   | ns |

| T34a | xCS ネガートに対する xDACK アサート時間          | 0               | -   | -   | ns |

| T34b | xDACK ネガートに対する xCS アサート時間          | 0               | -   | -   | ns |

## 7. 電気的特性

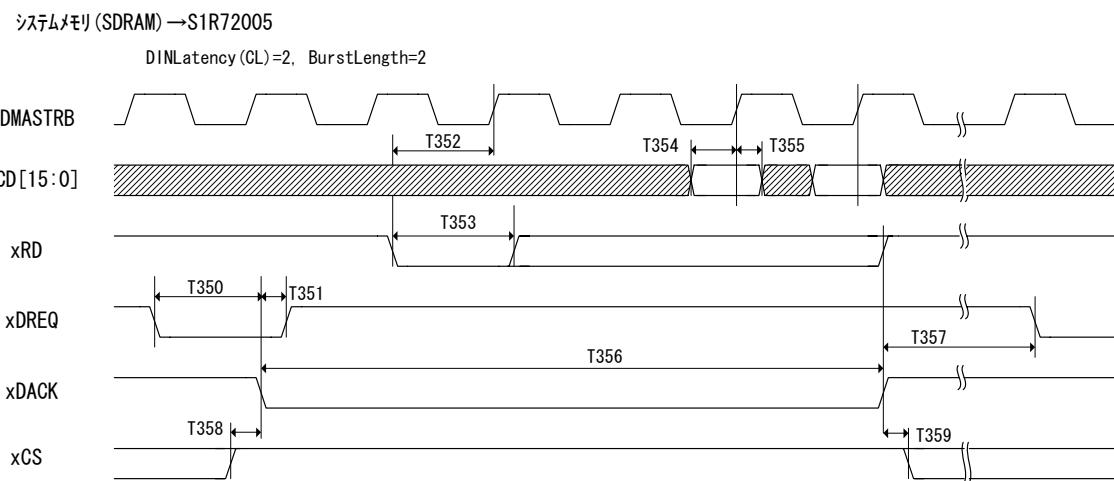

### 7.4.3.6 DMASTRB SDRAM モード(DMAIN)

| 記号   | 説明                                | min             | typ | max | 単位 |

|------|-----------------------------------|-----------------|-----|-----|----|

| T350 | xDREQ アサートに対する xDACK アサート時間       | 0               | -   | -   | ns |

| T351 | xDACK アサートに対する xDREQ ネガート時間       | -               | -   | 10  | ns |

| T352 | xRD(~CAS)アサートに対する DMASTRB 有効エッジ時間 | 3               | -   | -   | ns |

| T353 | xRD(~CAS)アサートパルス幅                 | 1T<br>(DMASTRB) | -   | -   | ns |

| T354 | DMASTRB 有効エッジに対する データセットアップ時間     | 10              | -   | -   | ns |

| T355 | DMASTRB 有効エッジに対する データホールド時間       | 0               | -   | -   | ns |

| T356 | xDACK アサートパルス幅                    | 42              | -   | -   | ns |

| T357 | xDACK ネガートに対する xDREQ アサート時間       | 160             | -   | -   | ns |

| T358 | xCS ネガートに対する xDACK アサート時間         | 0               | -   | -   | ns |

| T359 | xDACK ネガートに対する xCS アサート時間         | 0               | -   | -   | ns |

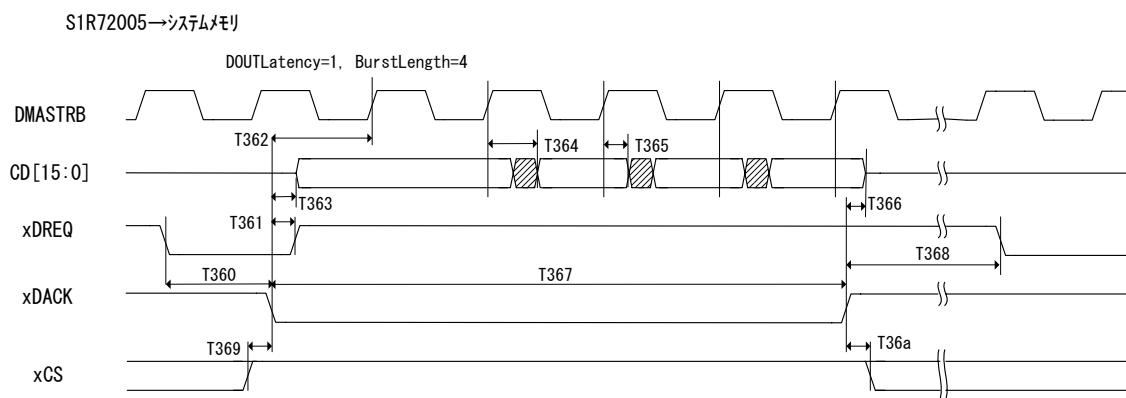

## 7.4.3.7 DMASTRB 汎用モード (DMAOUT)

| 記号   | 説明                             | min | typ | max | 単位 |

|------|--------------------------------|-----|-----|-----|----|

| T360 | xDREQ アサートに対する xDACK アサート時間    | 0   | -   | -   | ns |

| T361 | xDACK アサートに対する xDREQ ネガート時間    | -   | -   | 10  | ns |

| T362 | xDACK アサートに対する DMASTRB 有効エッジ時間 | 3   | -   | -   | ns |

| T363 | xDACK アサートに対する出力データ遅延時間        | -   | -   | 7   | ns |

| T364 | DMASTRB 有効エッジに対する出力データ遅延時間     | -   | -   | 9   | ns |

| T365 | DMASTRB 有効エッジに対する出力データホールド時間   | 4   | -   | -   | ns |

| T366 | xDACK ネガートに対するデータホールド時間        | 2   | -   | -   | ns |

| T367 | xDACK アサートパルス幅                 | 42  | -   | -   | ns |

| T368 | xDACK ネガートに対する xDREQ アサート時間    | 160 | -   | -   | ns |

| T369 | xCS ネガートに対する xDACK アサート時間      | 0   | -   | -   | ns |

| T36a | xDACK ネガートに対する xCS アサート時間      | 0   | -   | -   | ns |

## 7. 電気的特性

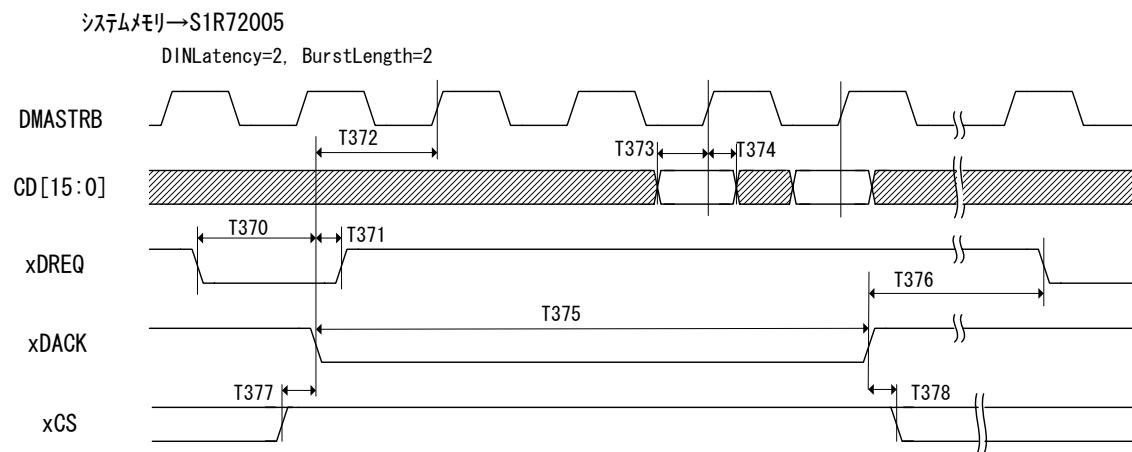

### 7.4.3.8 DMASTRB 汎用モード (DMAIN)

| 記号   | 説明                              | min | typ | max | 単位 |

|------|---------------------------------|-----|-----|-----|----|

| T370 | xDREQ アサートに対する xDACK アサート時間     | 0   | -   | -   | ns |

| T371 | xDACK アサートに対する xDREQ ネガート時間     | -   | -   | 10  | ns |

| T372 | xDACK アサートに対する DMASTRB 有効エッジ 時間 | 3   | -   | -   | ns |

| T373 | DMASTRB 有効エッジ に対する テータセットアップ 時間 | 10  | -   | -   | ns |

| T374 | DMASTRB 有効エッジ に対する テータホールド 時間   | 0   | -   | -   | ns |

| T375 | xDACK アサートパルス幅                  | 42  | -   | -   | ns |

| T376 | xDACK ネガートに対する xDREQ アサート時間     | 160 | -   | -   | ns |

| T377 | xCS ネガートに対する xDACK アサート時間       | 0   | -   | -   | ns |

| T378 | xDACK ネガートに対する xCS アサート時間       | 0   | -   | -   | ns |

### 7.4.4 USB I/F タイミング

USB2.0 規格に準拠しています。

## 8. 外形寸法図

### 8. 外形寸法図

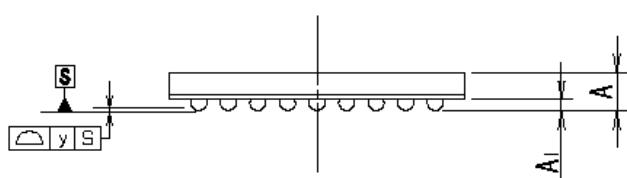

#### 8.1 CSP パッケージ

Top View

Bottom View

| Symbol         | Dimension in Millimeters |      |      |

|----------------|--------------------------|------|------|

|                | Min                      | Nom  | Max  |

| D              | 7.80                     | 8.0  | 8.2  |

| E              | 7.80                     | 8.0  | 8.2  |

| A              |                          |      | 1.20 |

| A <sub>1</sub> | 0.25                     | 0.30 | 0.35 |

| [e]            |                          | 0.80 |      |

| b              | 0.38                     | 0.43 | 0.48 |

| X              |                          |      | 0.08 |

| Y              |                          |      | 0.10 |

| Z <sub>D</sub> |                          | 0.80 |      |

| Z <sub>E</sub> |                          | 0.80 |      |

1 = 1mm

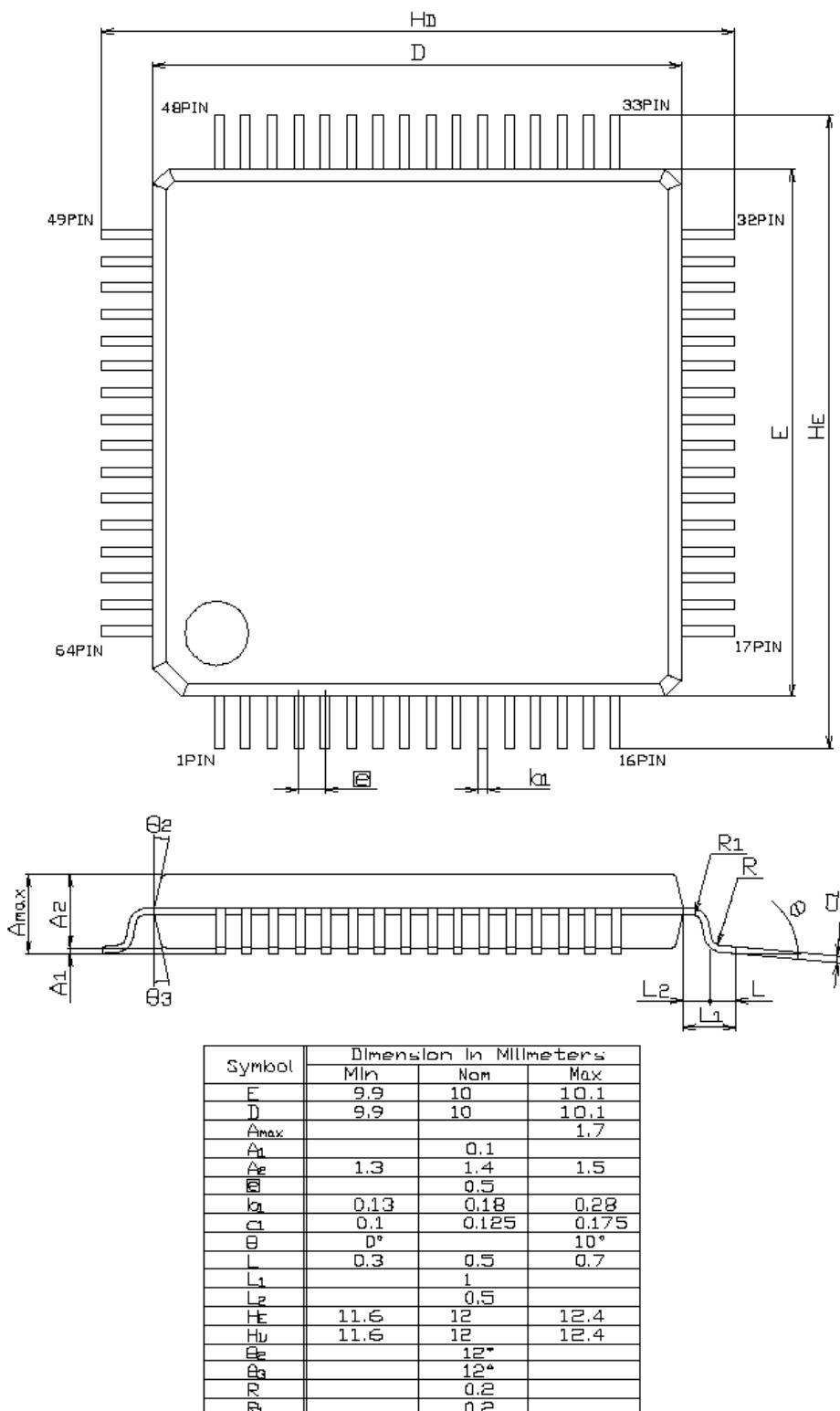

## 8.2 QFP パッケージ

## 9. 接続例

### 9. 接続例

外部周辺回路の接続例（参考例）を示します。

(注) 当接続例はあくまで参考例であり、お客様の製品での動作を保証するものではありません。

回路構成の詳細および部品の選定につきましては、お客様にてあらためて御検討ください。

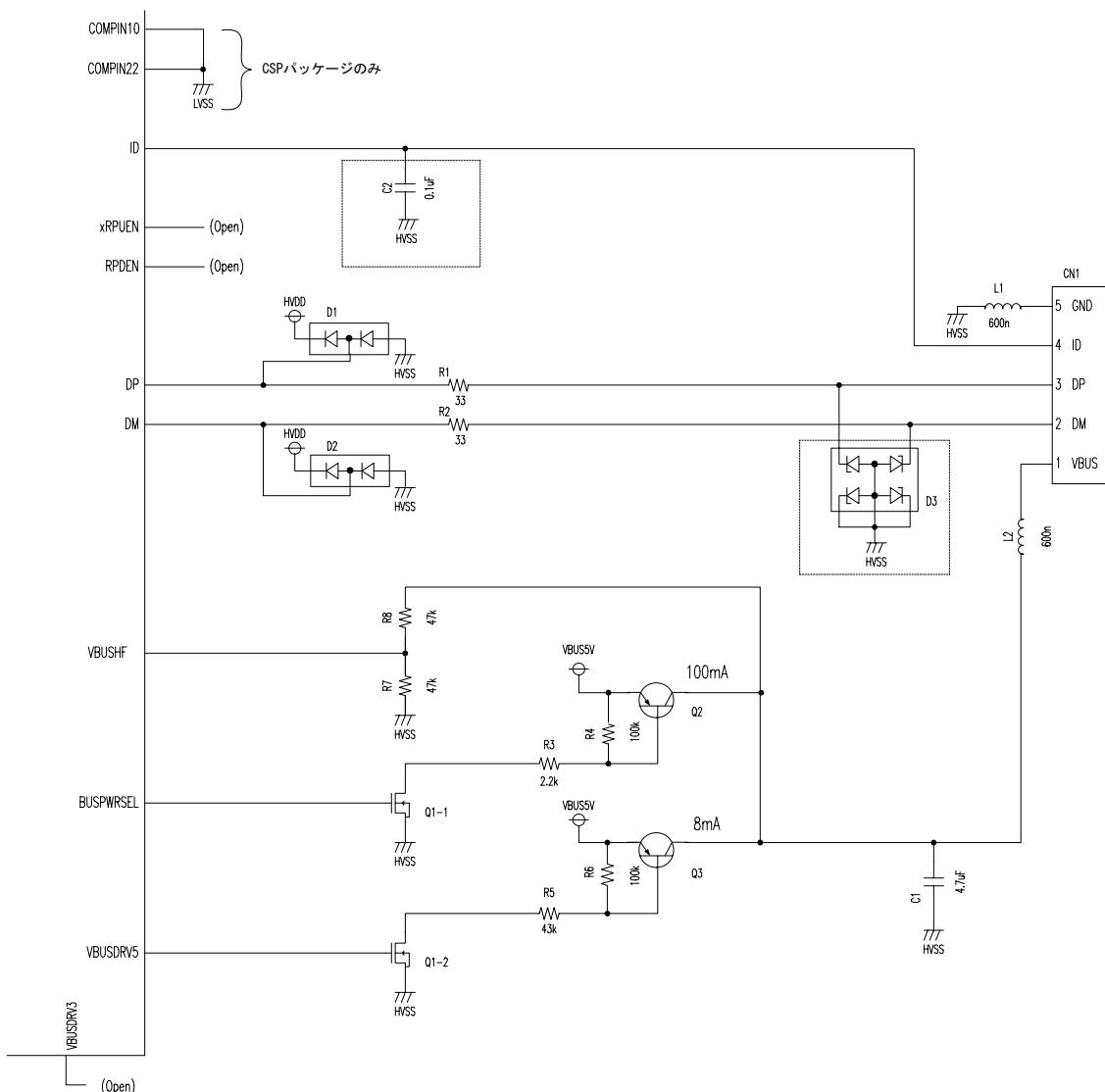

#### 9.1 OTG I/F 端子接続例

##### (接続上の注意)

- 静電気保護のため、必ずD1およびD2のダイオードによる保護回路を設けてください。その場合、ダイオードは特性および定格等を考慮のうえ選定してください。

- さらなる静電気保護のためには、D3のダイオードを使用することも考えられます。

- C1は1.0uF～6.5uFの範囲で選択可能です。

- ID端子の静電気保護のためにC2を使用することも考えられます。

- DPおよびDMラインは同長かつ短く配線してください。

- OTG I/F部配線の直近直下に他の配線をしないでください。

### 接続部品例

(注) 本部品表はあくまで参考例であり、お客様の製品での動作を保証するものではありません。部品の選定につきましては、お客様にてあらためて御検討ください。

| 項  | 記号     | 部品名           | 部品型番               | 仕様(定数)     | 動作温度(℃) | メーカー  | 部品数 |

|----|--------|---------------|--------------------|------------|---------|-------|-----|

| 1  | C1     | セラミックコンデンサ    | GRM31MF11C475ZA12B | 16V 4.7uF  | -25~85  | 村田製作所 | 1   |

| 2  | C2     | セラミックコンデンサ    | GRM40F104Z50PT     | 0.1uF      | -25~85  | 村田製作所 | 1   |

| 3  | L1, L2 | EMI Filter    | BLM21PG600SN1      | 600nH      | -55~125 | 村田製作所 | 2   |

| 4  | R1, R2 | 抵抗            | RK73H1JTD33F       | 33Ω        | -55~125 | KOA   | 2   |

| 5  | R3     | 抵抗            | RK73H1JTD2.2kD     | 2.2kΩ      | -55~125 | KOA   | 1   |

| 6  | R4, R6 | 抵抗            | RK73H1JTD100kD     | 100kΩ      | -55~125 | KOA   | 2   |

| 7  | R5     | 抵抗            | RK73H1JTD43kD      | 43kΩ       | -55~125 | KOA   | 1   |

| 8  | R7, R8 | 抵抗            | RK73H2BTM47kF      | 47kΩ       | -55~125 | KOA   | 2   |

| 9  | Q1     | FET           | TPCS8205           |            | -55~150 | 東芝    | 1   |

| 10 | Q2, Q3 | トランジスタ        | 2SA1121            | PNP        | -55~125 | 日立    | 2   |

| 11 | D1, D2 | ダイオード         | ISS396             |            | -40~100 | 東芝    | 2   |

| 12 | D3     | ダイオード         | NNCD5.6LG          |            | -40~100 | NEC   | 1   |

| 13 | CN1    | USBReceptacle | MNE20              | USB miniAB | -       | ACON  | 1   |

## 9. 接続例

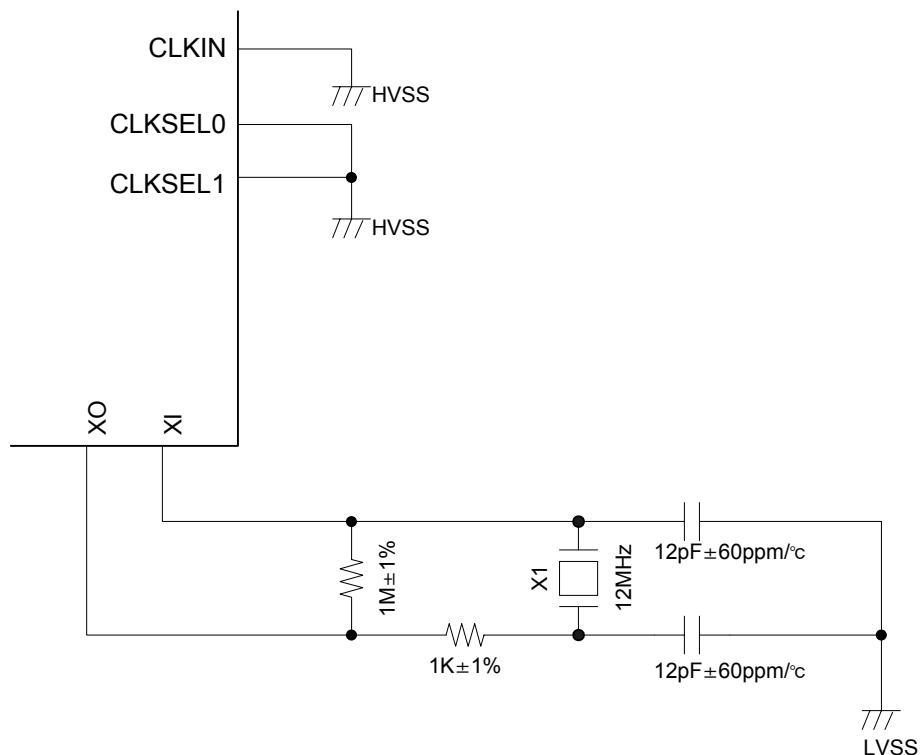

### 9.2 クロック端子接続例

<水晶振動子使用時>

X1\* : MA-406 12MHz 10pF 30ppm (EPSON)

(接続上の注意)

- クロック部配線の直近直下に他の配線をしないでください。

- XIおよびXOの回路および定数は、使用する水晶振動子X1の接続例を参考にしてください。

- XIおよびXOの回路は最短で配線してください。

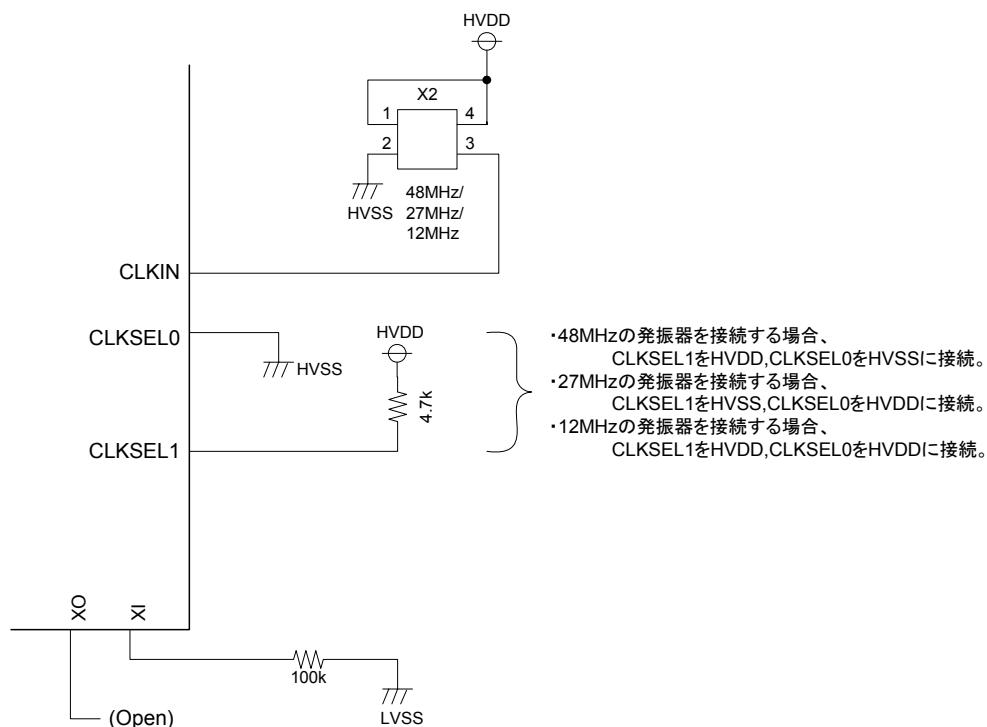

## &lt;水晶発振器（外部クロック入力）使用時&gt;

X2\* : 例 SG-615PCW 48MHz±50ppm (EPSON)

中心周波数±50ppm以下の水晶発振器を推奨いたします。

PLL デバイスはジッタが大きいため推奨できかねます。

## (接続上の注意)

- クロック部配線の直近直下に他の配線をしないでください。

- CLKINの回路は、使用する水晶発振器X2の接続例を参考にしてください。

- CLKINの回路は最短で配線してください。

- CLKINの入力電圧は必要動作条件のHVi入力電圧規定値を守ってください。

- XIの配線はできるだけ短くしてください。

- XOの配線はできるだけ短くしてオープンとしてください。

## 9. 接続例

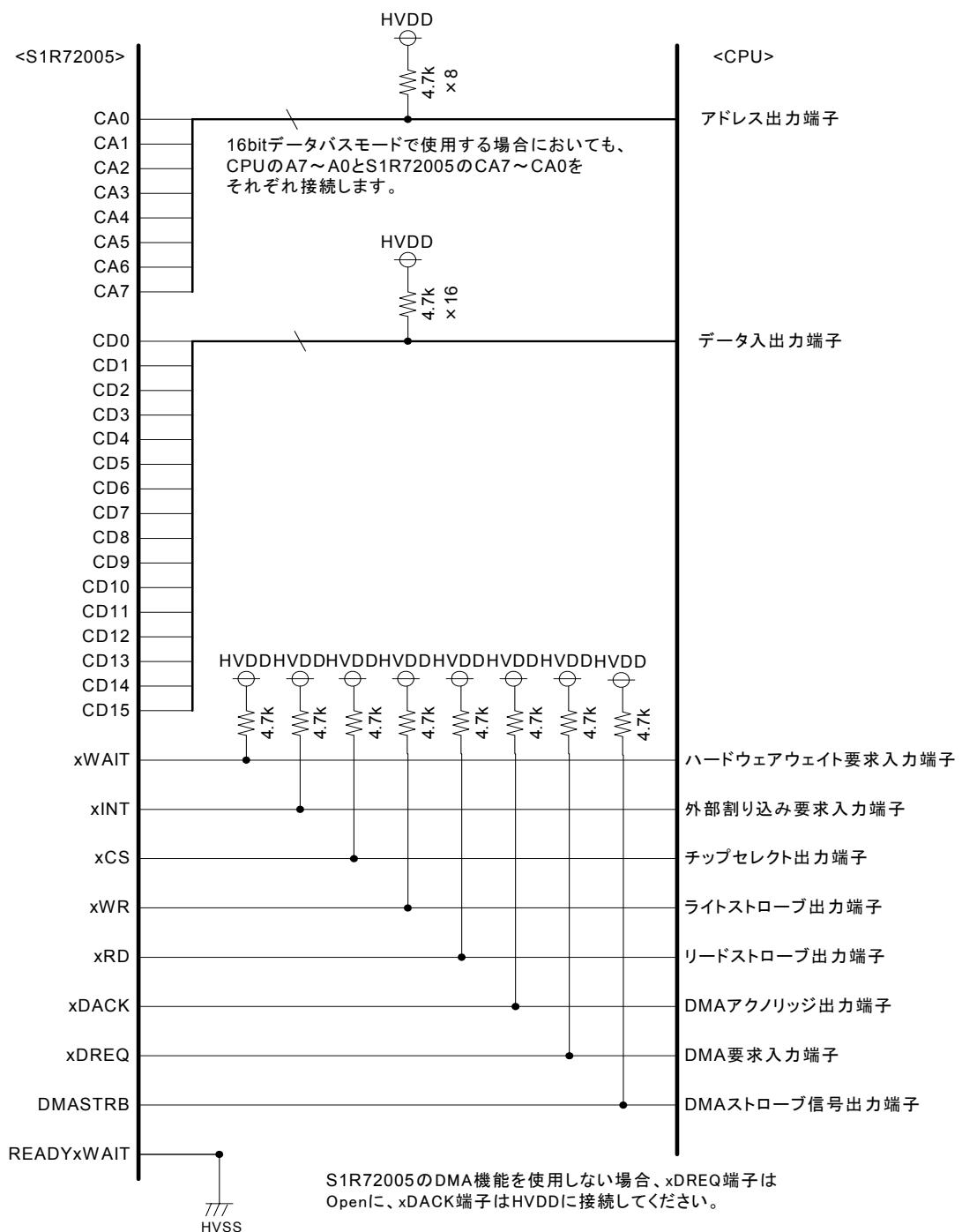

### 9.3 CPU I/F 端子接続例

#### (接続上の注意)

- READYxWAIT 端子は、お客様のシステムに合わせて必ず HVDD か HVSS に接続してください。

- PullUp 抵抗はお客様のシステムにおいて必要と判断された場合に、適切な値の抵抗をご使用ください。

- S1R72005 の DMASTRB 端子を未使用時は、本端子は HVSS に接続してください。

- データバスが 8bit の CPU と接続する場合、S1R72005 では下位 8bit を使用し、上位 8bit は HVSS に接続してください。

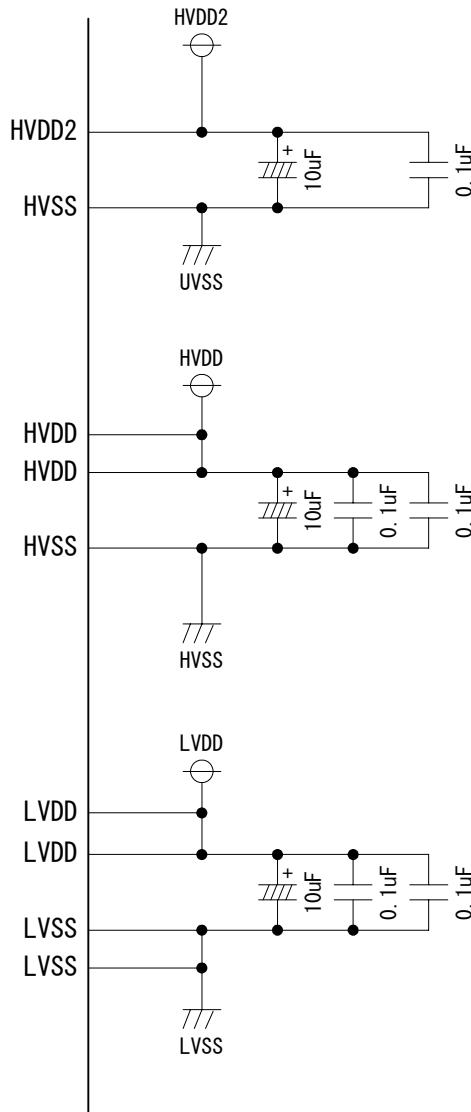

## 9.4 電源およびグランド端子接続例

(接続上の注意)

- HVSS と CPU の I/O 用グランドとは共通のグランドとしてください。

- USBI/O 部に配置された HVDD 2 (CSP:G3、QFP:20 ピン) および HVSS (CSP:H5、QFP:23 ピン) は、端子専用に（上図最上部参照）コンデンサを接続してください。

## 9. 接続例

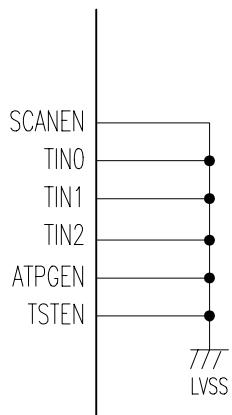

### 9.5 テスト端子接続例

(接続上の注意)

- すべてのテスト入力端子はかならず上図のようにVSSへ接続してください。

本仕様書において掲載した応用回路例は、あくまで参考であって特許侵害を誘起させる目的ではありません。万一、これらの応用回路例を適用して特許侵害が生じたとしても、当社は何ら責任を負うものではありません。

**セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

**<IC 東日本営業グループ>**

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

**<IC 西日本営業グループ>**

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

名古屋 〒460-0008 名古屋市中区栄 1-10-21 名古屋御園ビル 6F

TEL (052) 205-8421 (代表) FAX (052) 231-2538