**EPSON**

CMOS 8-BIT SINGLE CHIP MICROCOMPUTER

# S1C88650

テクニカルマニュアル

S1C88650 Technical Hardware

セイコーエプソン株式会社

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

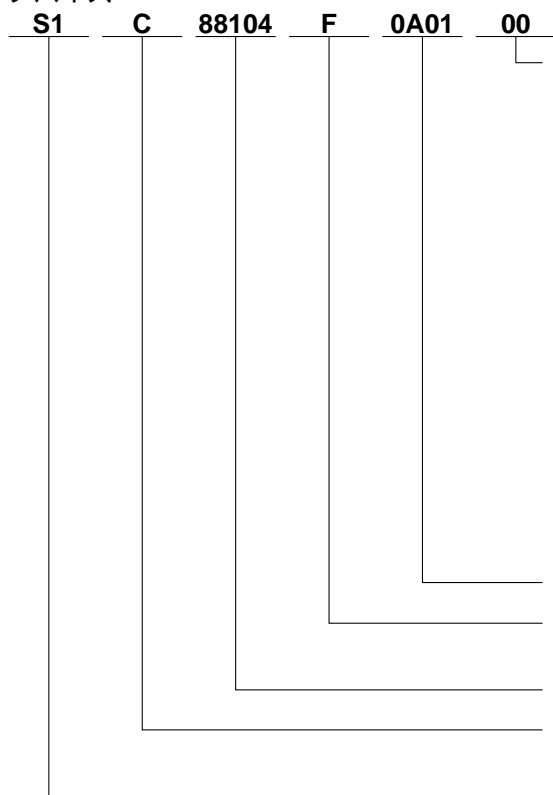

## 製品型番体系

デバイス

### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

### 仕様

[D: ベアチップ、F: QFP]

### 機種番号

### 機種名称

[C: マイコン、デジタル製品]

### 製品分類

[S1: 半導体]

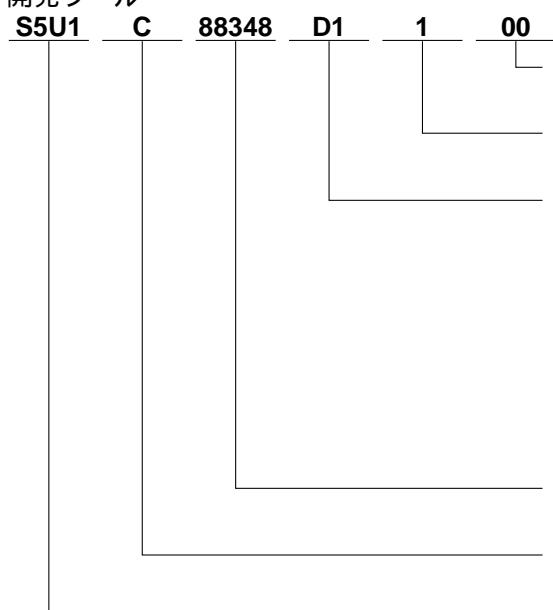

開発ツール

### 梱包仕様

[00: 標準梱包]

### バージョン

[1: Version 1]

### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ペリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

### 対応機種番号

[88348: S1C88348用]

### ツール分類

[C: マイコン用]

### 製品分類

[S5U1: 半導体用開発ツール]

## 一 目 次 一

|       |                                                       |    |

|-------|-------------------------------------------------------|----|

| 1     | 概要 .....                                              | 1  |

| 1.1   | 特長 .....                                              | 1  |

| 1.2   | ブロック図 .....                                           | 2  |

| 1.3   | 端子 .....                                              | 3  |

| 1.3.1 | 端子配置図 .....                                           | 3  |

| 1.3.2 | 端子説明 .....                                            | 4  |

| 1.4   | マスクオプション .....                                        | 5  |

| 2     | 電源 .....                                              | 7  |

| 2.1   | 動作電圧 .....                                            | 7  |

| 2.2   | 内部電源回路 .....                                          | 7  |

| 3     | CPUとバスの構成 .....                                       | 8  |

| 3.1   | CPU .....                                             | 8  |

| 3.2   | 内蔵メモリ .....                                           | 8  |

| 3.2.1 | プログラムROM .....                                        | 8  |

| 3.2.2 | RAM .....                                             | 8  |

| 3.2.3 | I/Oメモリ .....                                          | 8  |

| 3.2.4 | 表示メモリ .....                                           | 8  |

| 3.2.5 | 漢字フォント用ROM .....                                      | 8  |

| 3.3   | 例外処理ベクタ .....                                         | 9  |

| 3.4   | CC(カスタマイズコンディションフラグ) .....                            | 9  |

| 3.5   | チップモード .....                                          | 9  |

| 3.5.1 | MCUモードとMPUモード .....                                   | 9  |

| 3.5.2 | バスモード .....                                           | 10 |

| 3.5.3 | CPUモード .....                                          | 11 |

| 3.6   | 外部バス .....                                            | 11 |

| 3.6.1 | データバス .....                                           | 11 |

| 3.6.2 | アドレスバス .....                                          | 12 |

| 3.6.3 | リード( $\overline{RD}$ )/ライト( $\overline{WR}$ )信号 ..... | 12 |

| 3.6.4 | チップイネーブル( $\overline{CE}$ )信号 .....                   | 12 |

| 3.6.5 | ウェイト制御 .....                                          | 13 |

| 3.6.6 | バス権解放状態 .....                                         | 14 |

| 4     | イニシャルリセット .....                                       | 15 |

| 4.1   | イニシャルリセット要因 .....                                     | 15 |

| 4.1.1 | $\overline{RESET}$ 端子 .....                           | 15 |

| 4.1.2 | 入力ポート(K00~K03)の同時LOWレベル入力 .....                       | 16 |

| 4.1.3 | イニシャルリセットシーケンス .....                                  | 16 |

| 4.2   | イニシャルリセット時の初期設定 .....                                 | 17 |

| 5     | 周辺回路と動作 .....                                         | 18 |

| 5.1   | I/Oメモリマップ .....                                       | 18 |

| 5.2   | システムコントローラとバスの制御 .....                                | 34 |

| 5.2.1 | バスモードとCPUモードの設定 .....                                 | 34 |

| 5.2.2 | アドレスデコーダ( $\overline{CE}$ 出力)の設定 .....                | 34 |

| 5.2.3 | ウェイトステートの設定 .....                                     | 35 |

| 5.2.4 | バス権解放要求信号の設定 .....                                    | 35 |

|                                    |    |

|------------------------------------|----|

| 5.2.5 スタックページの設定 .....             | 35 |

| 5.2.6 システムコントローラの制御方法 .....        | 36 |

| 5.2.7 プログラミング上の注意事項 .....          | 38 |

| 5.3 ウオッヂドッグタイマ .....               | 39 |

| 5.3.1 ウオッヂドッグタイマの構成 .....          | 39 |

| 5.3.2 割り込み機能 .....                 | 39 |

| 5.3.3 ウオッヂドッグタイマの制御方法 .....        | 40 |

| 5.3.4 プログラミング上の注意事項 .....          | 40 |

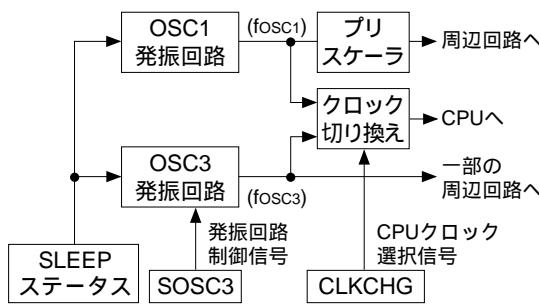

| 5.4 発振回路 .....                     | 41 |

| 5.4.1 発振回路の構成 .....                | 41 |

| 5.4.2 マスクオプション .....               | 41 |

| 5.4.3 OSC1発振回路 .....               | 41 |

| 5.4.4 OSC3発振回路 .....               | 42 |

| 5.4.5 CPUクロックの切り換え .....           | 42 |

| 5.4.6 発振回路の制御方法 .....              | 43 |

| 5.4.7 プログラミング上の注意事項 .....          | 43 |

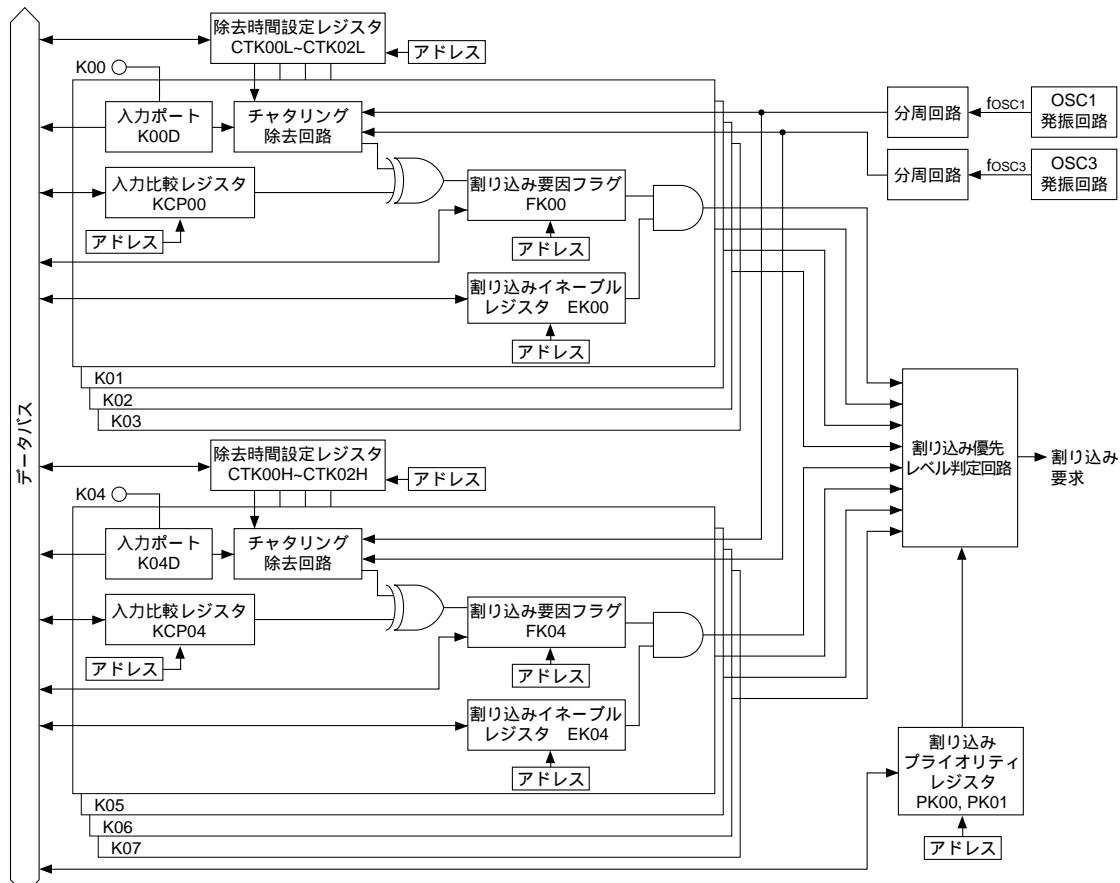

| 5.5 入力ポート (Kポート) .....             | 44 |

| 5.5.1 入力ポートの構成 .....               | 44 |

| 5.5.2 マスクオプション .....               | 44 |

| 5.5.3 プルアップ制御 .....                | 45 |

| 5.5.4 割り込み機能と入力比較レジスタ .....        | 45 |

| 5.5.5 入力ポートの制御方法 .....             | 47 |

| 5.5.6 プログラミング上の注意事項 .....          | 50 |

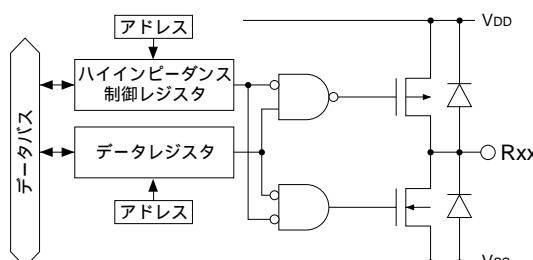

| 5.6 出力ポート (Rポート) .....             | 51 |

| 5.6.1 出力ポートの構成 .....               | 51 |

| 5.6.2 ハイインピーダンス制御 .....            | 51 |

| 5.6.3 DC出力 .....                   | 51 |

| 5.6.4 出力ポートの制御方法 .....             | 52 |

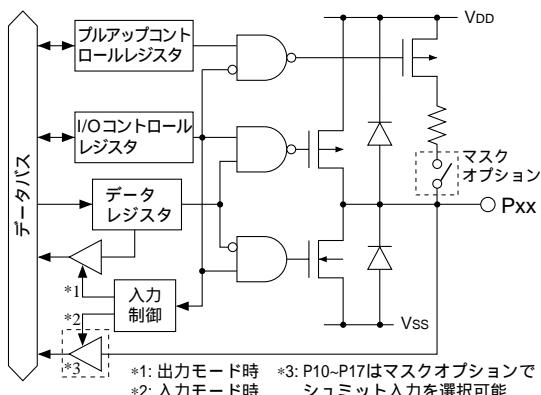

| 5.7 入出力兼用ポート (Pポート) .....          | 54 |

| 5.7.1 入出力兼用ポートの構成 .....            | 54 |

| 5.7.2 マスクオプション .....               | 54 |

| 5.7.3 I/Oコントロールレジスタと入力/出力モード ..... | 55 |

| 5.7.4 プルアップ制御 .....                | 55 |

| 5.7.5 特殊出力 .....                   | 55 |

| 5.7.6 入出力兼用ポートの制御方法 .....          | 57 |

| 5.7.7 プログラミング上の注意事項 .....          | 60 |

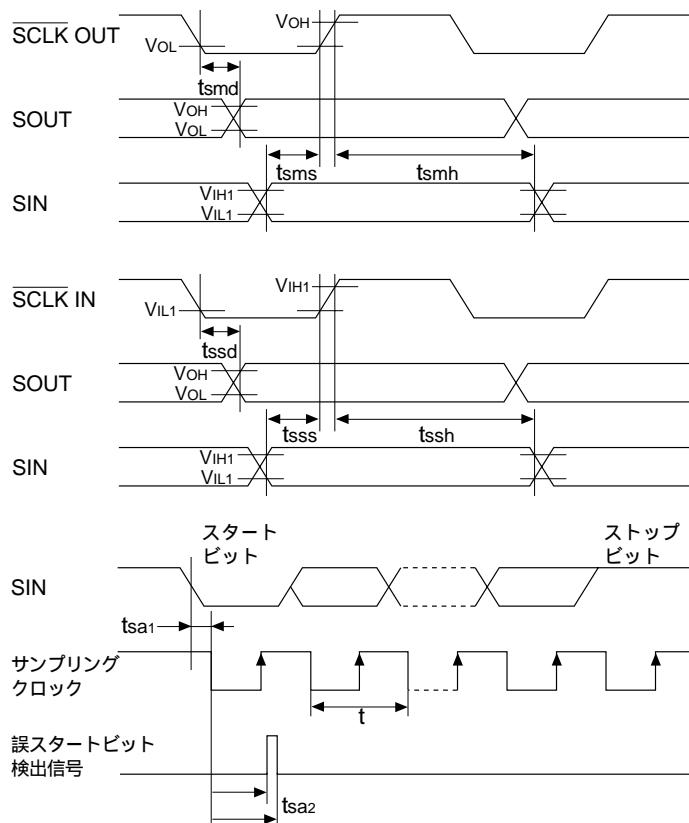

| 5.8 シリアルインタフェース .....              | 61 |

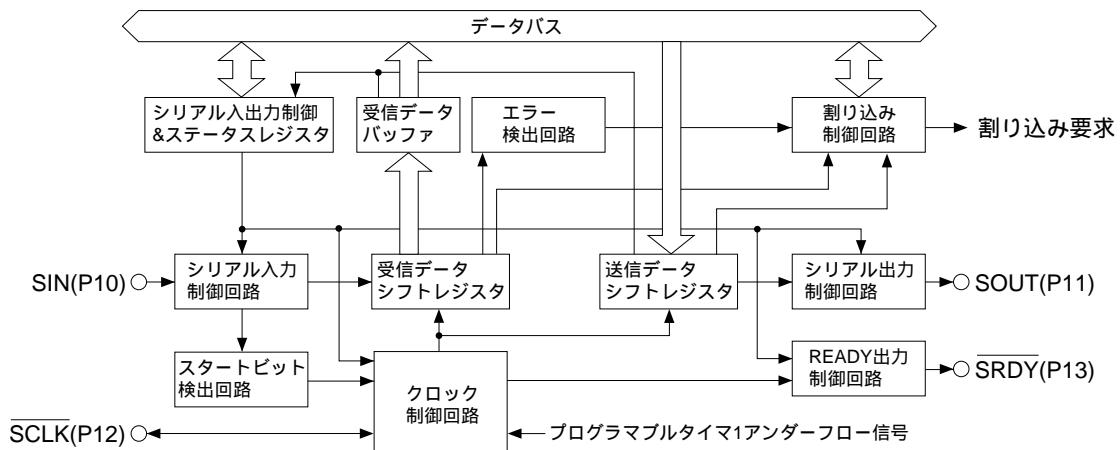

| 5.8.1 シリアルインタフェースの構成 .....         | 61 |

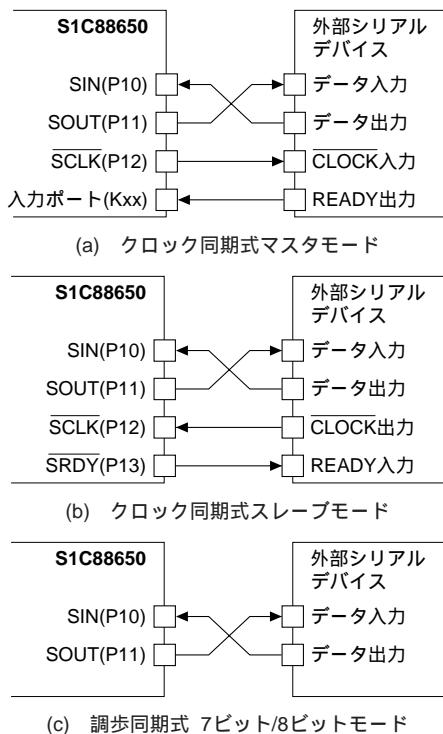

| 5.8.2 端子機能の切り換え .....              | 61 |

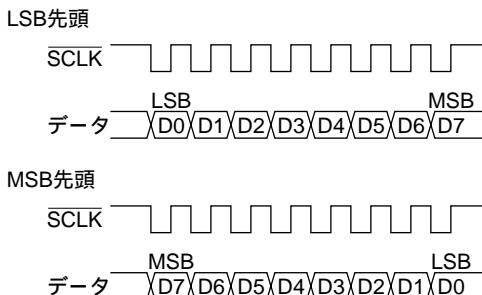

| 5.8.3 転送モード .....                  | 62 |

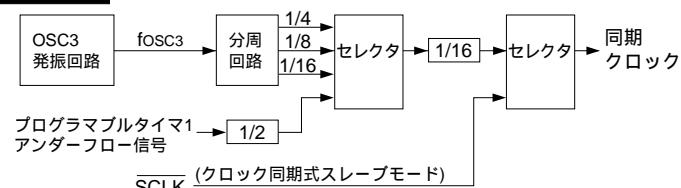

| 5.8.4 クロック源 .....                  | 63 |

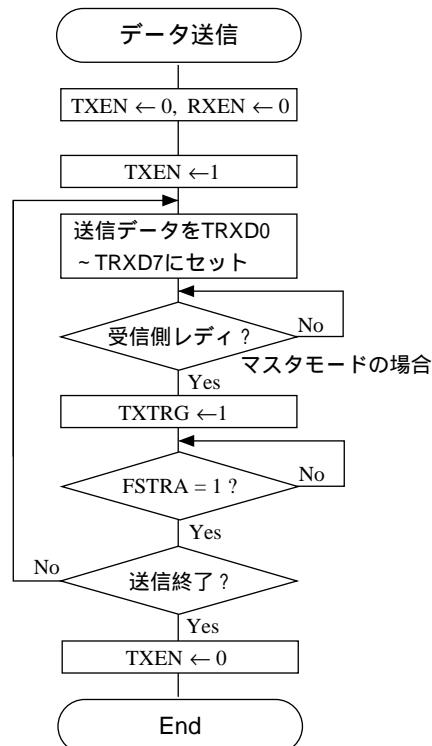

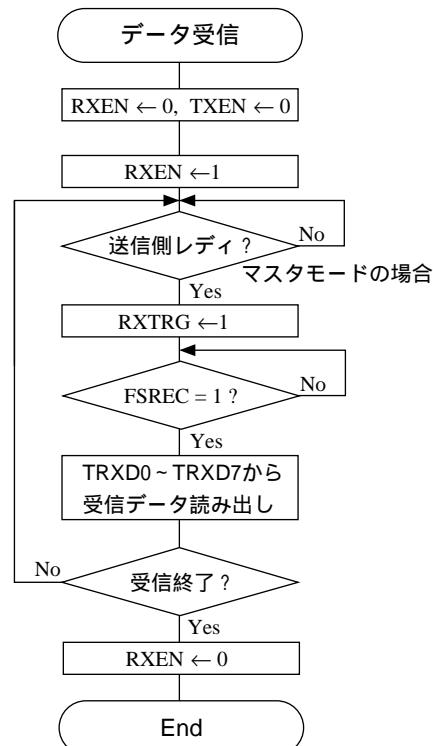

| 5.8.5 送受信の制御 .....                 | 64 |

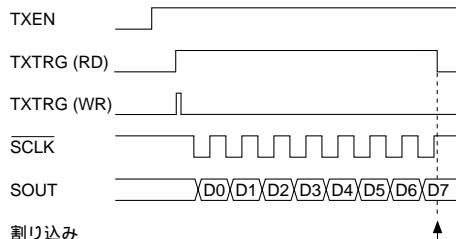

| 5.8.6 クロック同期式転送の動作 .....           | 65 |

| 5.8.7 調歩同期式転送の動作 .....             | 69 |

| 5.8.8 割り込み機能 .....                 | 73 |

| 5.8.9 シリアルインタフェースの制御方法 .....       | 75 |

| 5.8.10 プログラミング上の注意事項 .....         | 80 |

|                                        |     |

|----------------------------------------|-----|

| 5.9 計時タイマ .....                        | 81  |

| 5.9.1 計時タイマの構成 .....                   | 81  |

| 5.9.2 割り込み機能 .....                     | 81  |

| 5.9.3 計時タイマの制御方法 .....                 | 83  |

| 5.9.4 プログラミング上の注意事項 .....              | 85  |

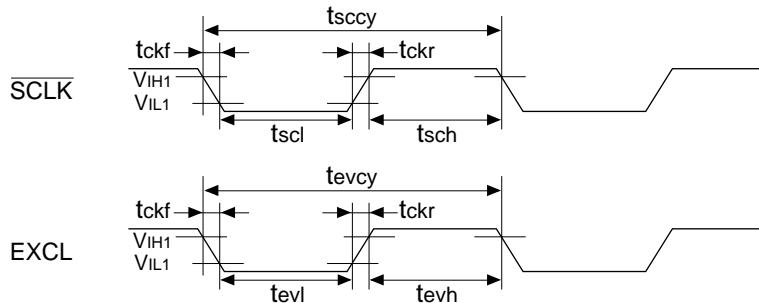

| 5.10 プログラマブルタイマ .....                  | 86  |

| 5.10.1 プログラマブルタイマの構成 .....             | 86  |

| 5.10.2 動作モード .....                     | 87  |

| 5.10.3 入力クロックの設定 .....                 | 89  |

| 5.10.4 タイマの動作と制御 .....                 | 89  |

| 5.10.5 割り込み機能 .....                    | 91  |

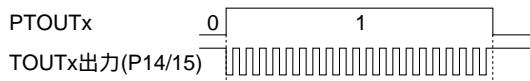

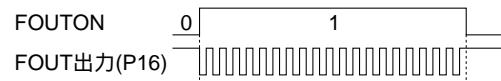

| 5.10.6 TOUT出力の設定 .....                 | 93  |

| 5.10.7 シリアルインターフェースの転送速度設定 .....       | 94  |

| 5.10.8 LCDドライバ用フレーム周波数の設定 .....        | 94  |

| 5.10.9 プログラマブルタイマの制御方法 .....           | 95  |

| 5.10.10 プログラミング上の注意事項 .....            | 107 |

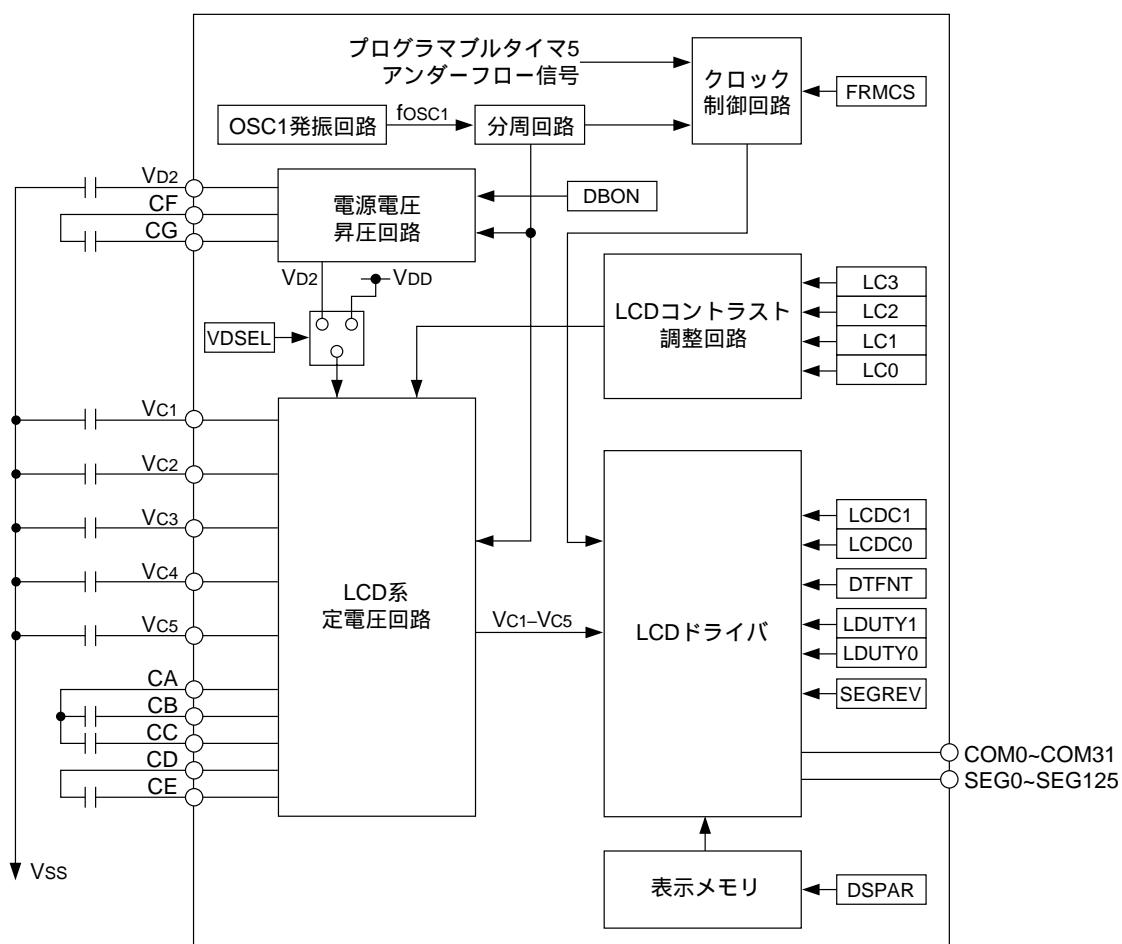

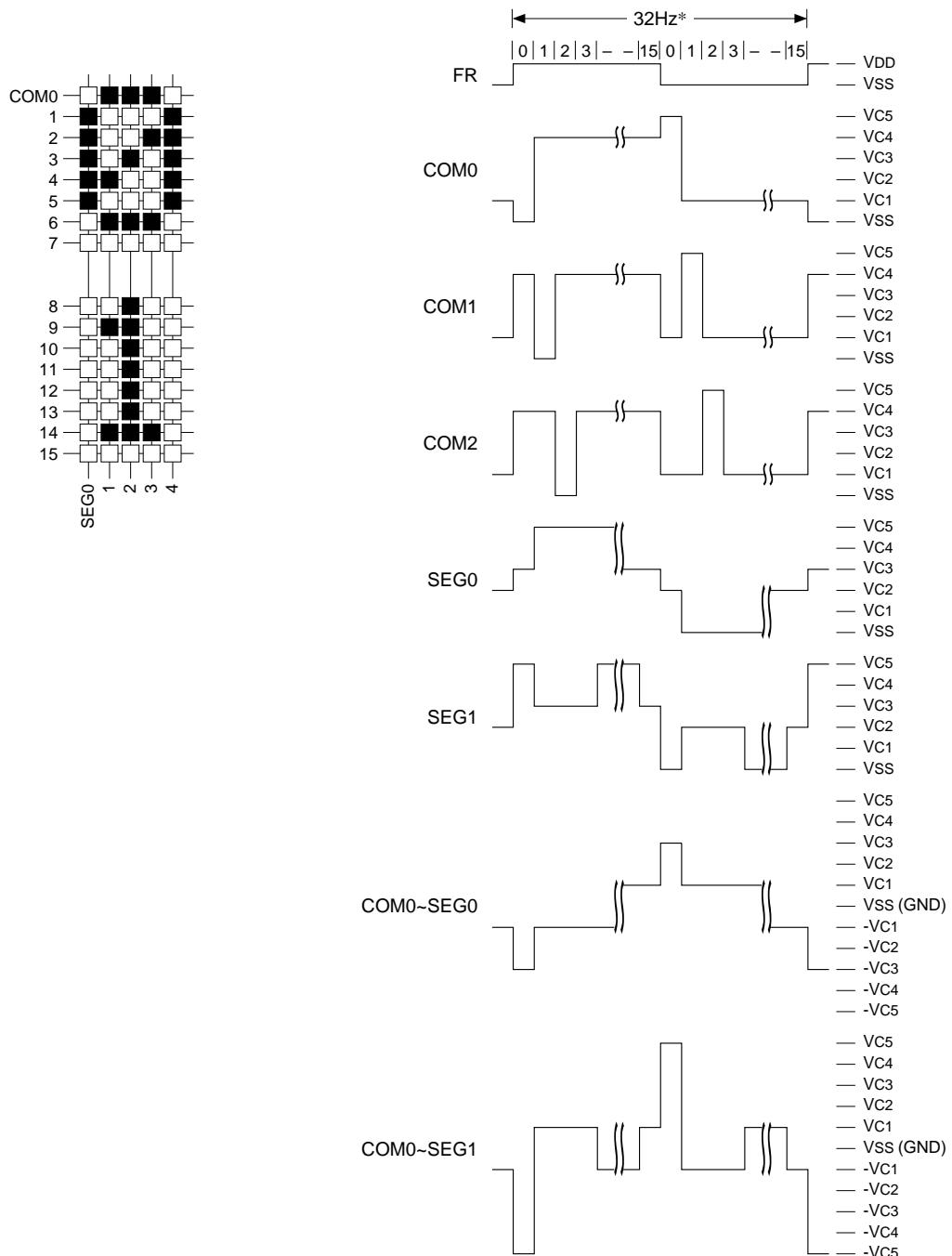

| 5.11 LCDドライバ .....                     | 108 |

| 5.11.1 LCDドライバの構成 .....                | 108 |

| 5.11.2 LCD電源 .....                     | 108 |

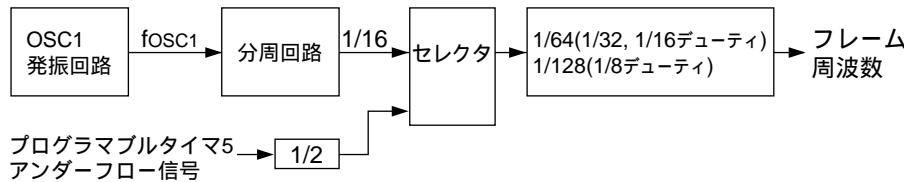

| 5.11.3 フレーム周波数 .....                   | 109 |

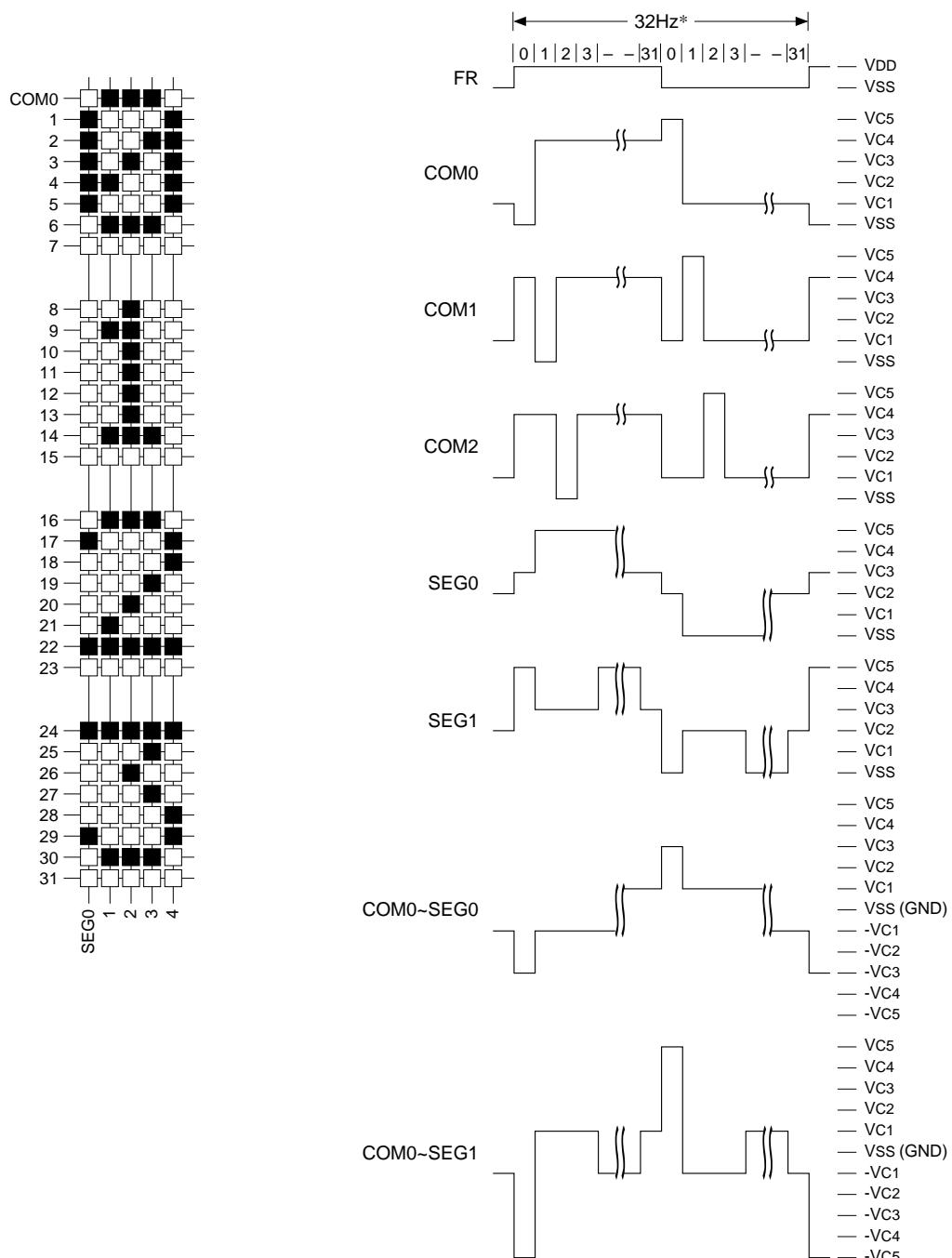

| 5.11.4 駆動デューティの切り換え .....              | 109 |

| 5.11.5 表示メモリ .....                     | 113 |

| 5.11.6 表示の制御 .....                     | 120 |

| 5.11.7 LCDドライバの制御方法 .....              | 121 |

| 5.11.8 プログラミング上の注意事項 .....             | 123 |

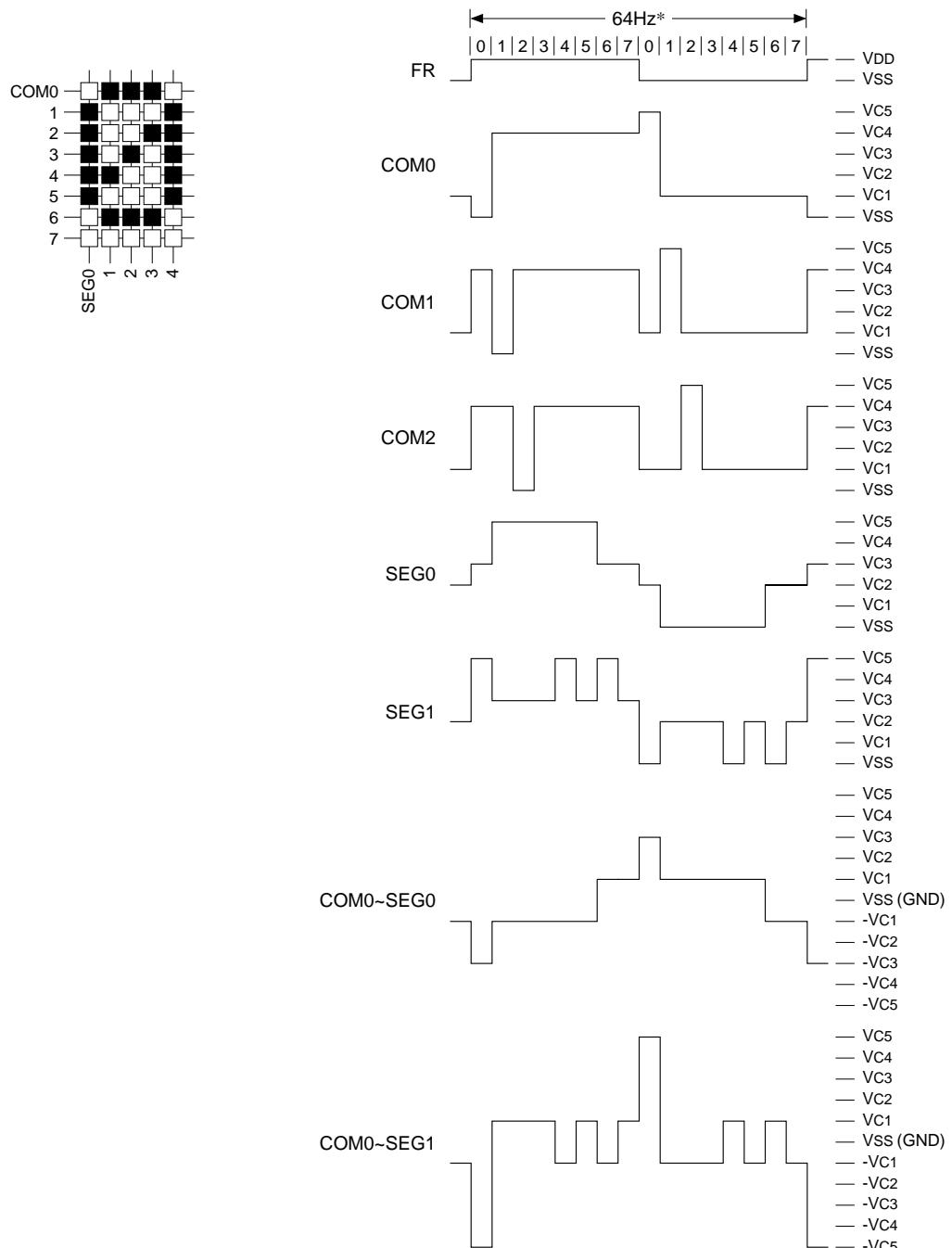

| 5.12 電源電圧検出(SVD)回路 .....               | 124 |

| 5.12.1 SVD回路の構成 .....                  | 124 |

| 5.12.2 SVD動作 .....                     | 124 |

| 5.12.3 SVD回路の制御方法 .....                | 125 |

| 5.12.4 プログラミング上の注意事項 .....             | 125 |

| 5.13 重負荷保護機能 .....                     | 126 |

| 5.13.1 重負荷保護モード .....                  | 126 |

| 5.13.2 重負荷保護機能の制御 .....                | 126 |

| 5.13.3 プログラミング上の注意事項 .....             | 126 |

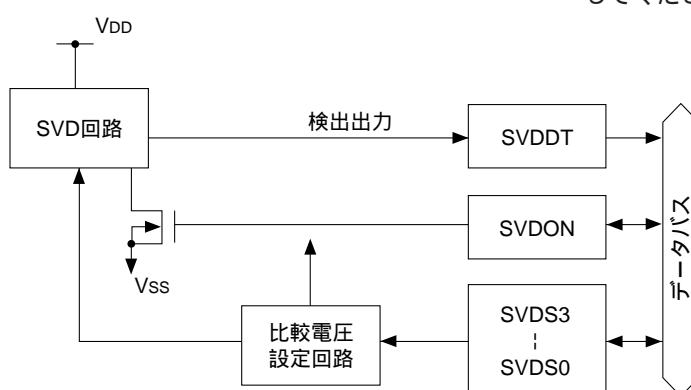

| 5.14 割り込みとスタンバイ状態 .....                | 127 |

| 5.14.1 割り込み発生条件 .....                  | 127 |

| 5.14.2 割り込み要因フラグ .....                 | 129 |

| 5.14.3 割り込みイネーブルレジスタ .....             | 130 |

| 5.14.4 割り込みプライオリティレジスタと割り込み優先レベル ..... | 131 |

| 5.14.5 例外処理ベクタ .....                   | 132 |

| 5.14.6 割り込みの制御 .....                   | 133 |

| 5.14.7 プログラミング上の注意事項 .....             | 135 |

| 6 注意事項 .....                           | 136 |

| 6.1 低消費電力化のための注意事項 .....               | 136 |

| 6.2 実装上の注意事項 .....                     | 137 |

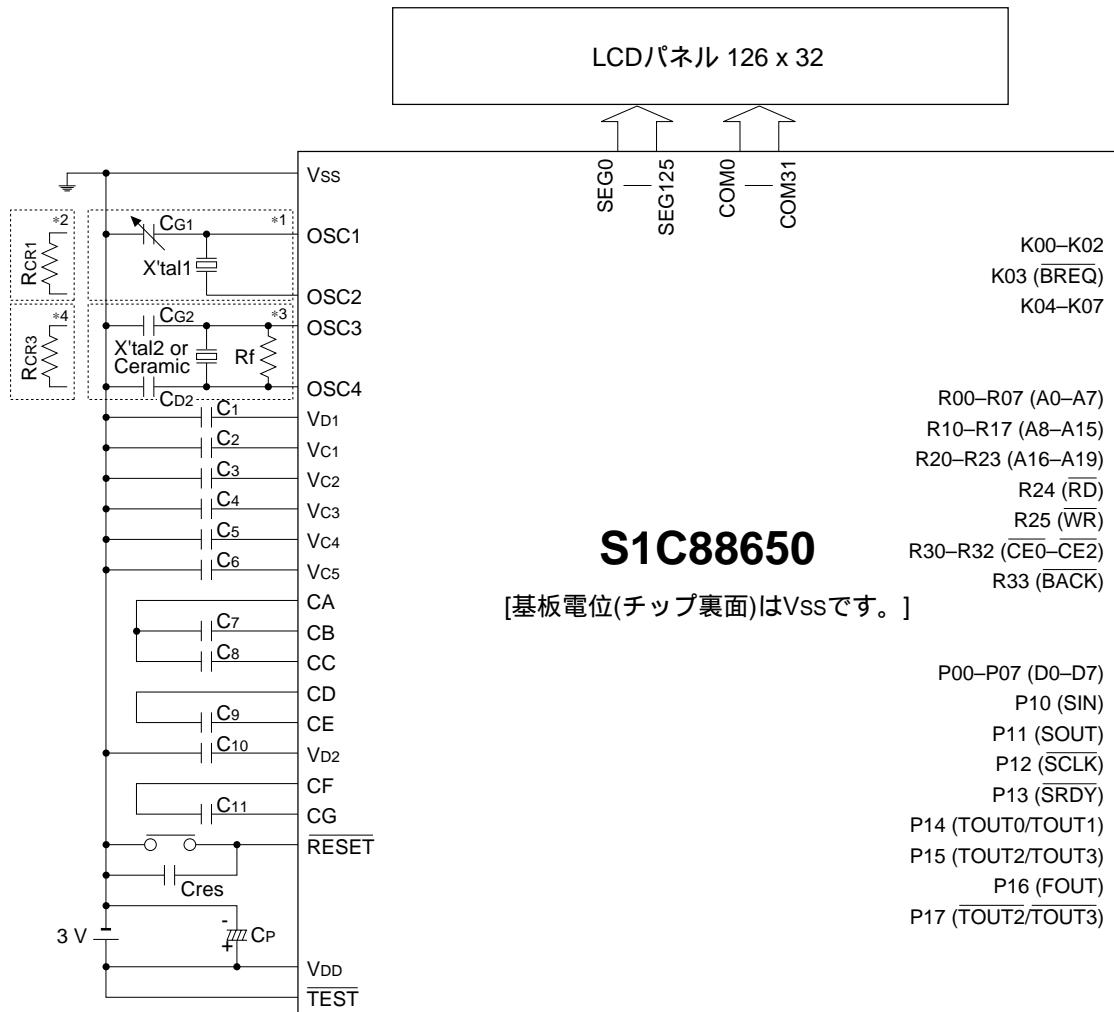

| 7 基本外部結線図 .....                        | 139 |

|            |                                                                                |     |

|------------|--------------------------------------------------------------------------------|-----|

| 8          | 電気的特性 .....                                                                    | 140 |

| 8.1        | 絶対最大定格 .....                                                                   | 140 |

| 8.2        | 推奨動作条件 .....                                                                   | 140 |

| 8.3        | DC特性 .....                                                                     | 141 |

| 8.4        | アナログ回路特性 .....                                                                 | 142 |

| 8.5        | 消費電流 .....                                                                     | 143 |

| 8.6        | AC特性 .....                                                                     | 144 |

| 8.7        | 発振特性 .....                                                                     | 149 |

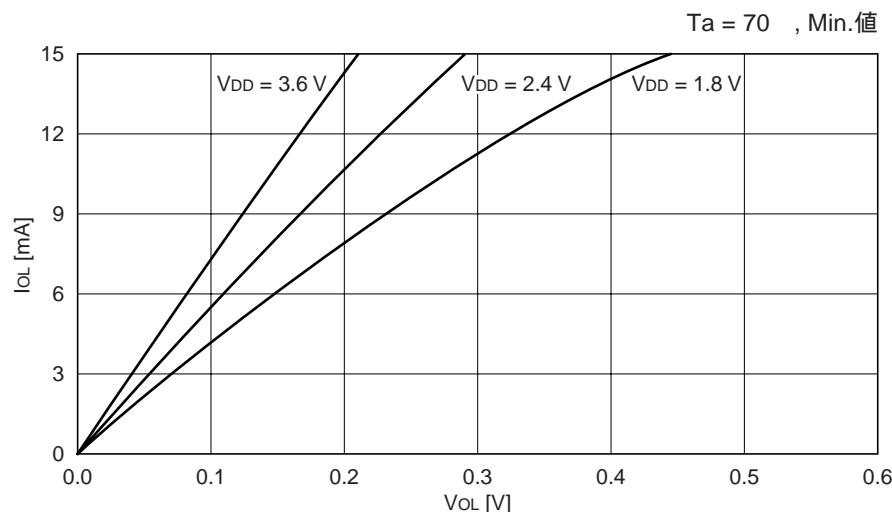

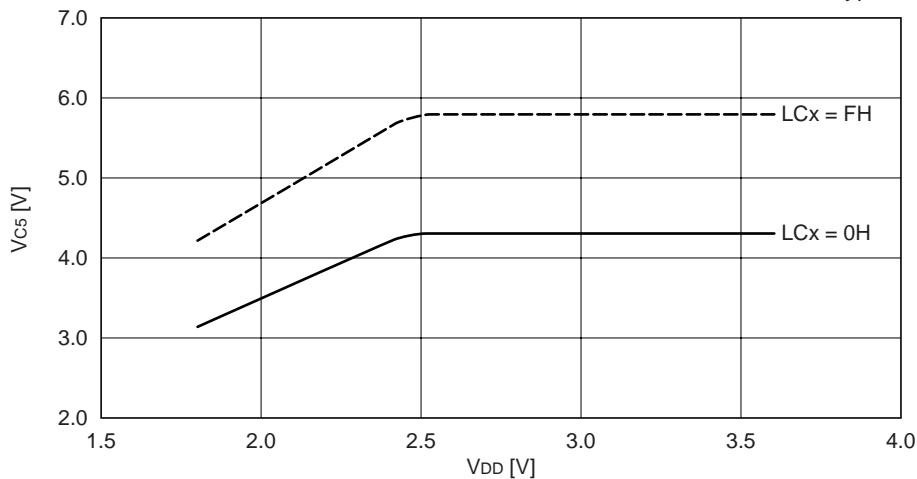

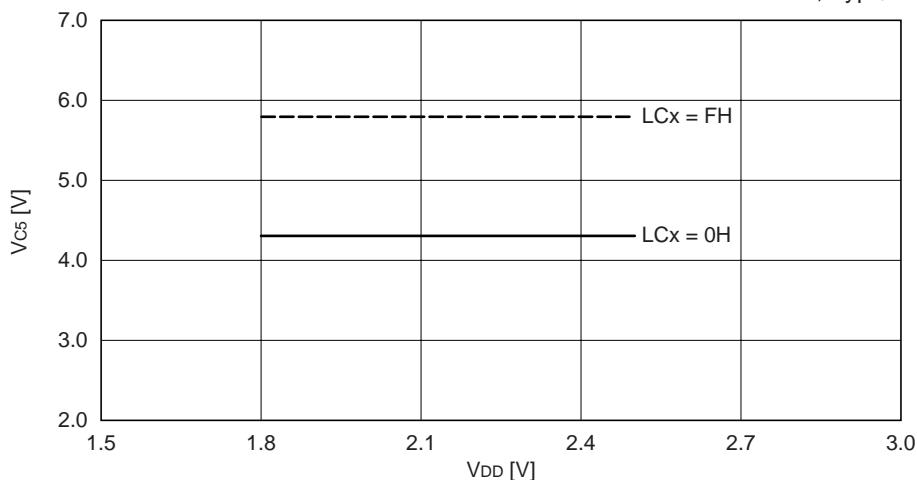

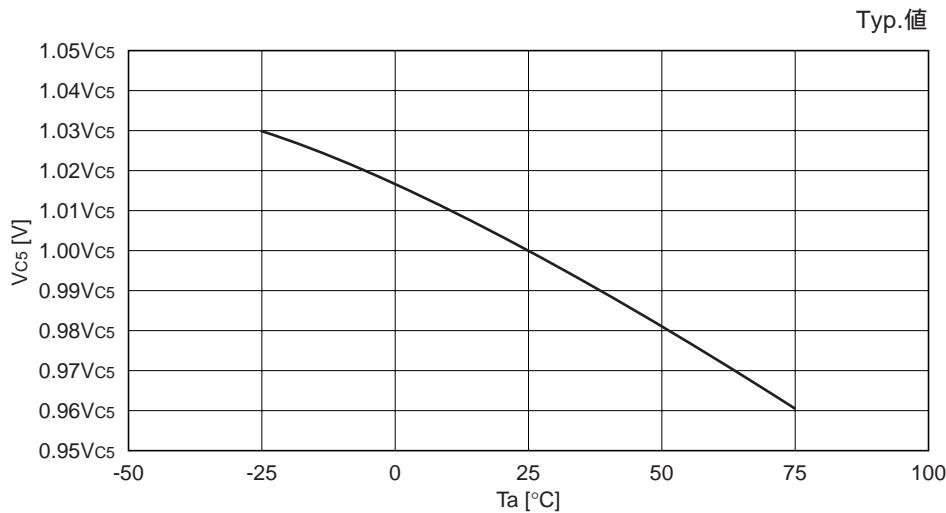

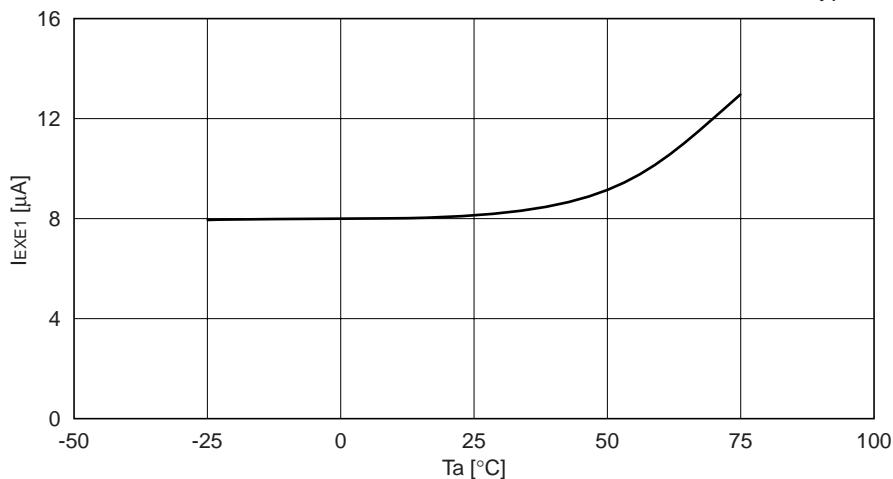

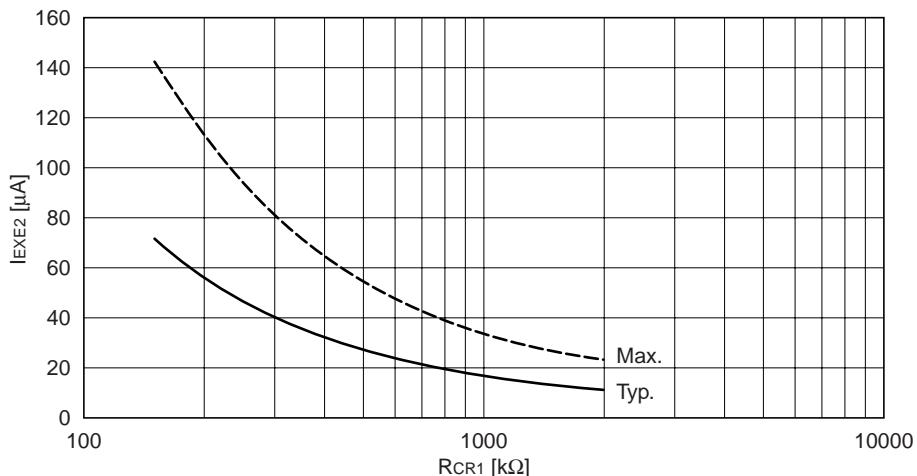

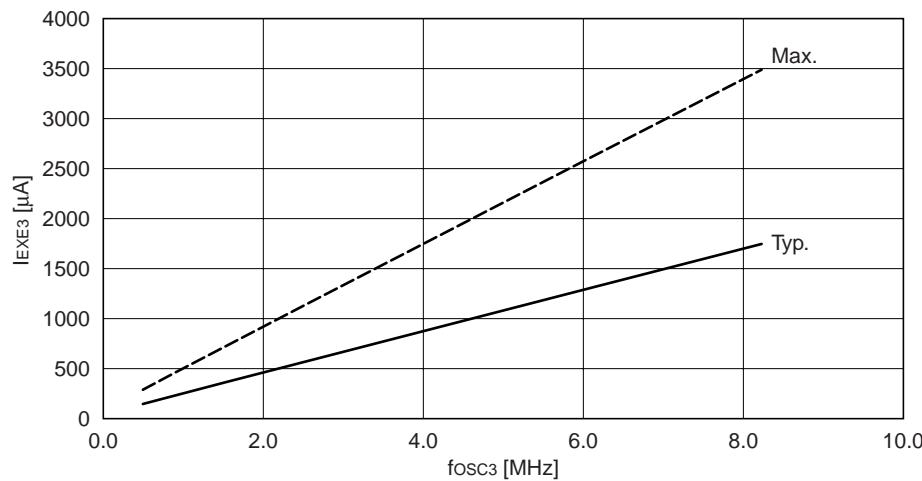

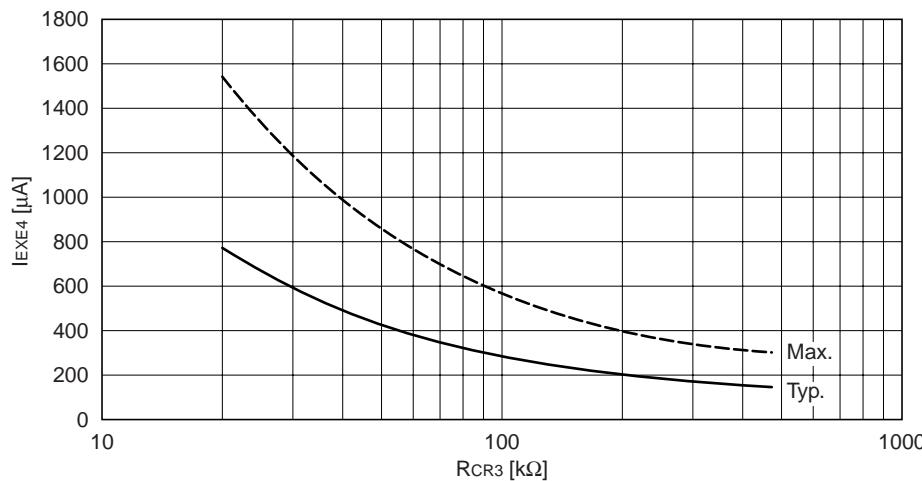

| 8.8        | 特性グラフ (参考値) .....                                                              | 150 |

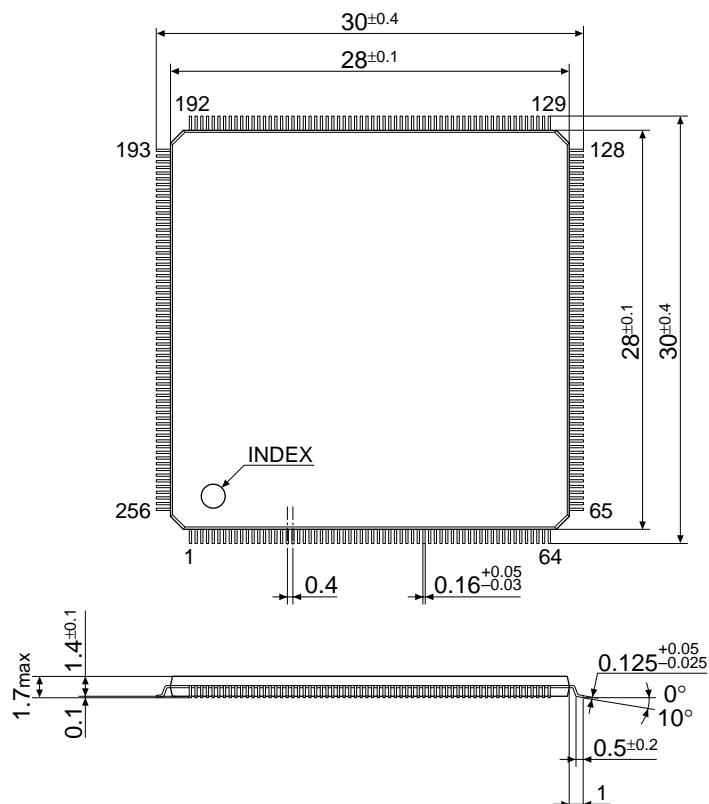

| 9          | パッケージ .....                                                                    | 159 |

| 9.1        | プラスチックパッケージ .....                                                              | 159 |

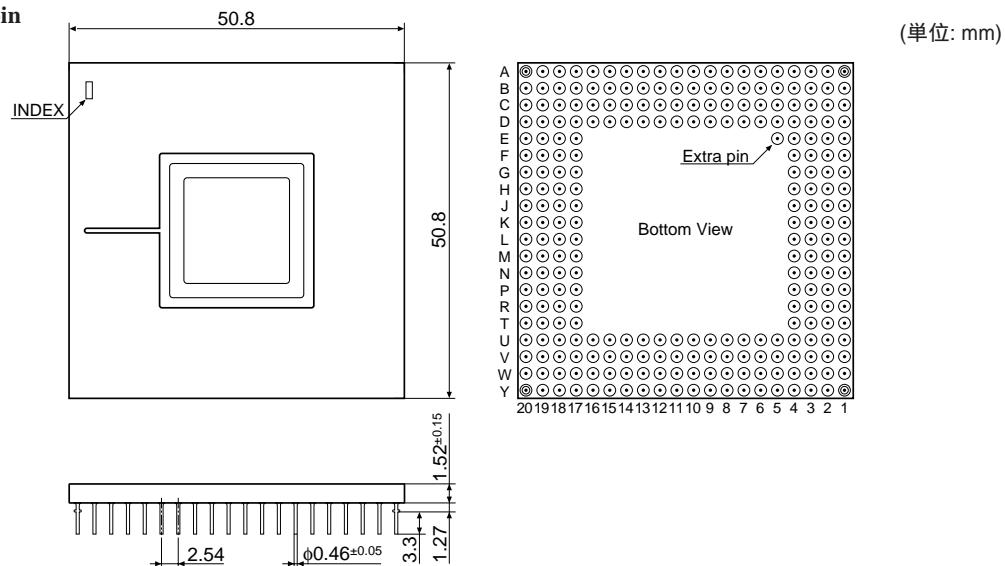

| 9.2        | テストサンプル用セラミックパッケージ .....                                                       | 160 |

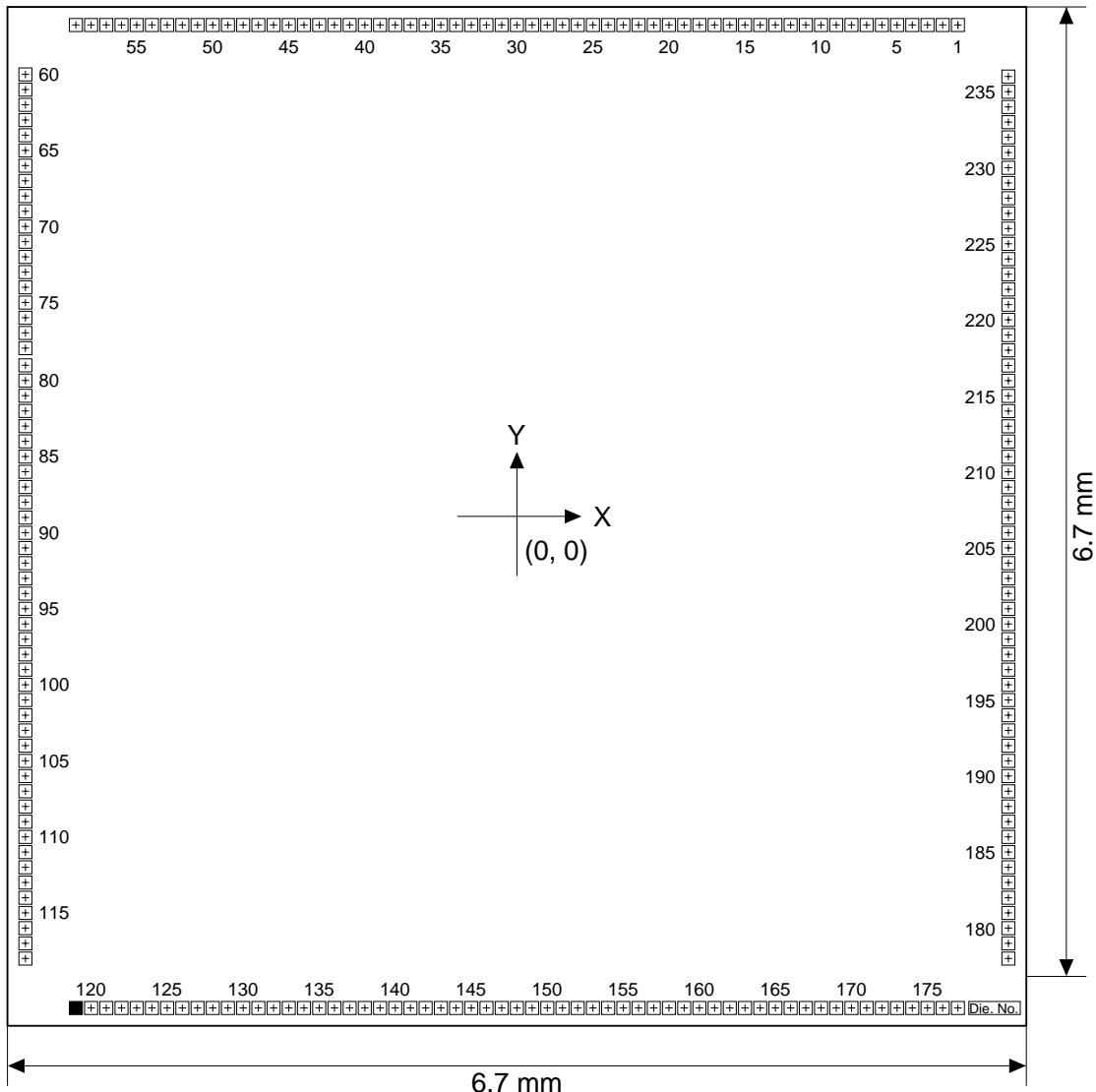

| 10         | パッド配置 .....                                                                    | 161 |

| 10.1       | パッド配置図 .....                                                                   | 161 |

| 10.2       | パッド座標 .....                                                                    | 162 |

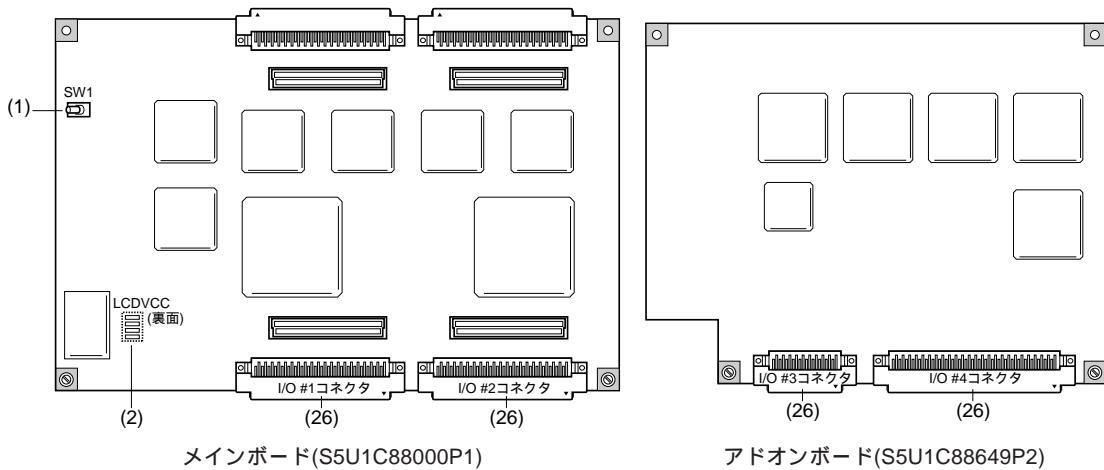

| Appendix A | S5U1C88000P1&S5U1C88649P2 Manual (Peripheral Circuit Board for S1C88650) ..... | 163 |

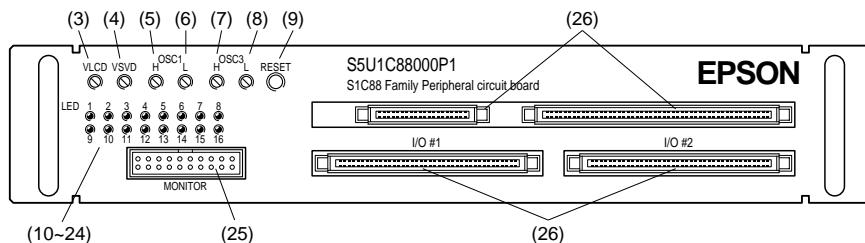

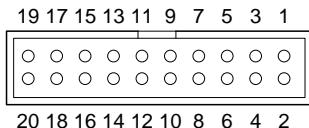

| A.1        | 各部の名称と機能 .....                                                                 | 163 |

| A.2        | 使用上の注意 .....                                                                   | 165 |

| A.2.1      | 操作上の注意事項 .....                                                                 | 165 |

| A.2.2      | 実際のICとの相違点 .....                                                               | 165 |

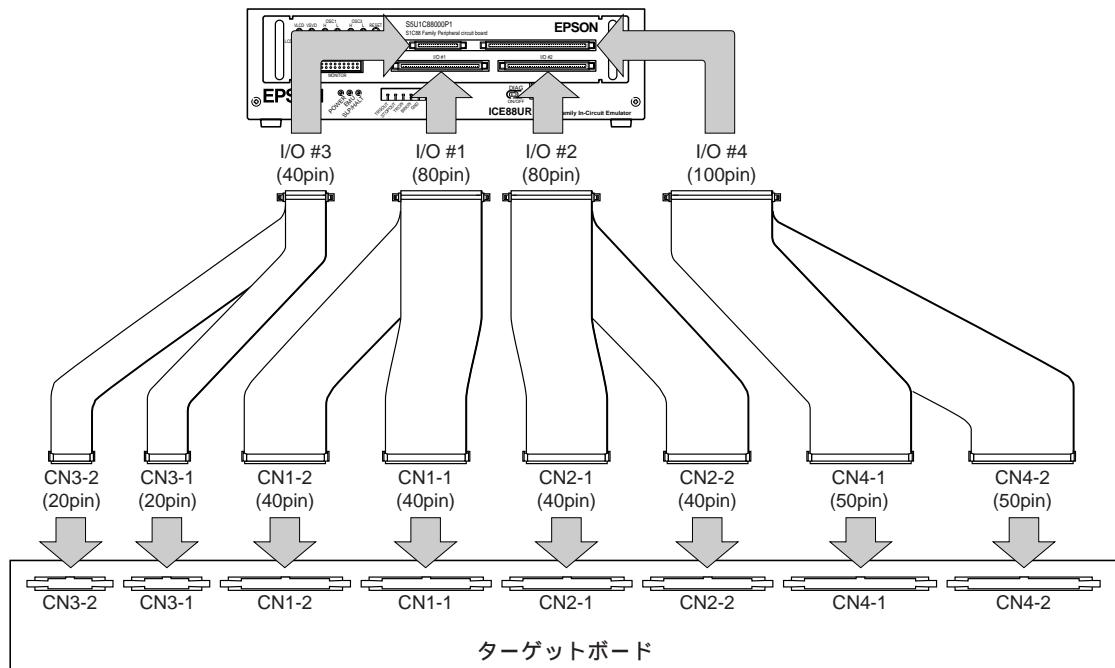

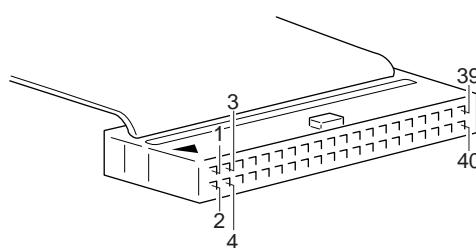

| A.3        | ターゲットシステムとの接続 .....                                                            | 168 |

| A.4        | 製品の仕様 .....                                                                    | 171 |

| Appendix B | 漢字フォントの使用について .....                                                            | 172 |

# 1 概要

S1C88650は、液晶表示付きの携帯機器向けにドットマトリックスLCDコントローラ/ドライバおよび漢字フォント用ROMを内蔵した8ビットマイクロコンピュータです。1.8Vで8.2MHzと高速で、スタンバイ時は2.5μAと低消費電流です。

LCDコントローラ/ドライバは、LCD駆動電源回路を内蔵しており、低消費電力で126×32のLCDパネルを駆動することができます。

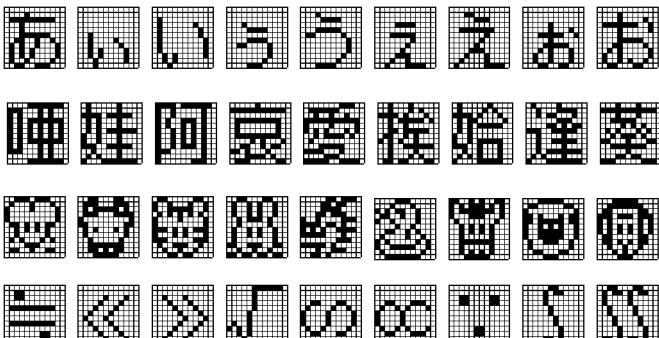

11×12のJIS第1水準、JIS第2水準、非漢字の漢字フォントおよびユーザ外字を内蔵可能で、外付けの漢字フォント用ROMを使わずに容易に漢字を表示することができます("Appendix B 漢字フォントの使用について"参照)。

本8ビットCPUは、最大16MBのアドレス空間をアクセスすることができるため、大容量のデータ処理なども容易にプログラミングすることができます。従来、専用のLCDドライバを使用する必要のあるたさまざまな表示モジュール、CD/MDプレイヤやソリッドオーディオ等の携帯オーディオ機器の他、PDA、データバンク等、多彩な応用が可能です。

## 1.1 特長

表1.1.1にS1C88650の特長を示します。

表1.1.1 特長

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| コアCPU         | CMOS 8ビットコアCPU S1C88 (MODEL3)                                                                                                                                                                                                                                                                                                                                                                                                            |

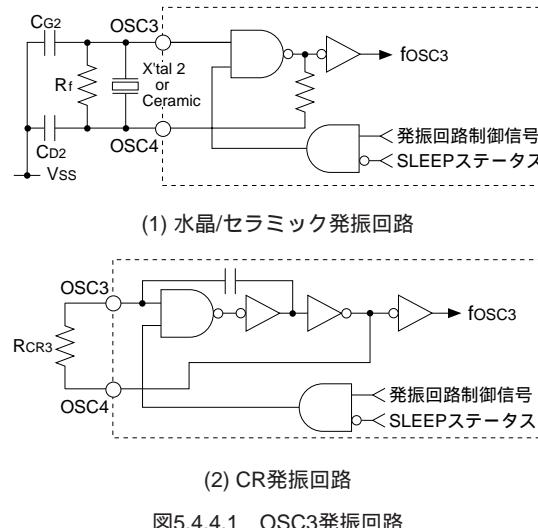

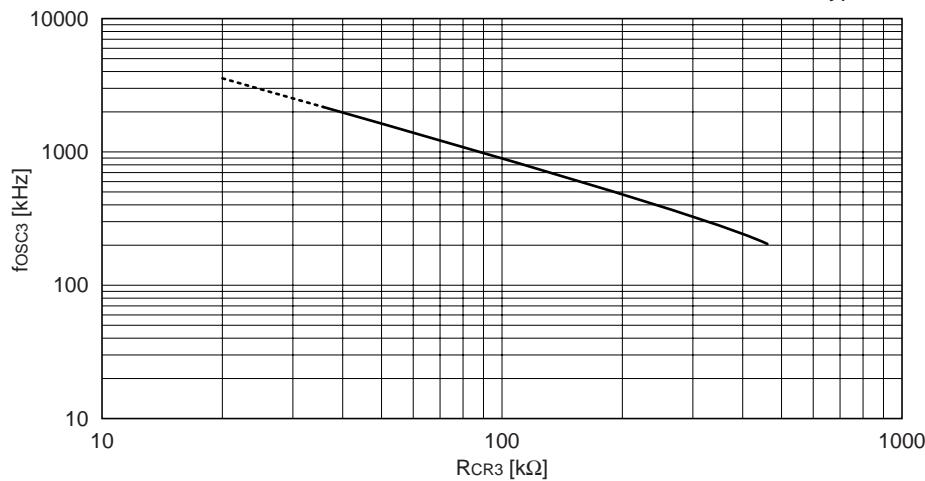

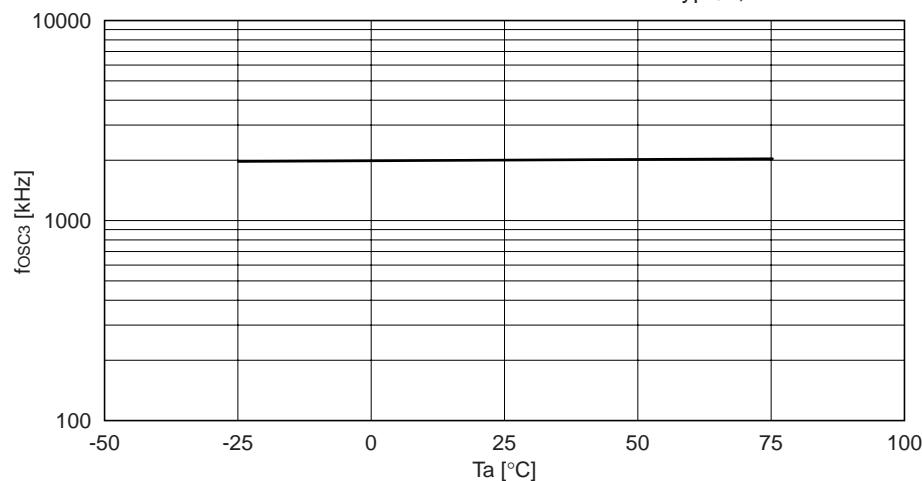

| メイン(OSC3)発振回路 | 水晶発振回路/セラミック発振回路 8.2MHz (Max.)、またはCR発振回路 2.2MHz (Max.)                                                                                                                                                                                                                                                                                                                                                                                   |

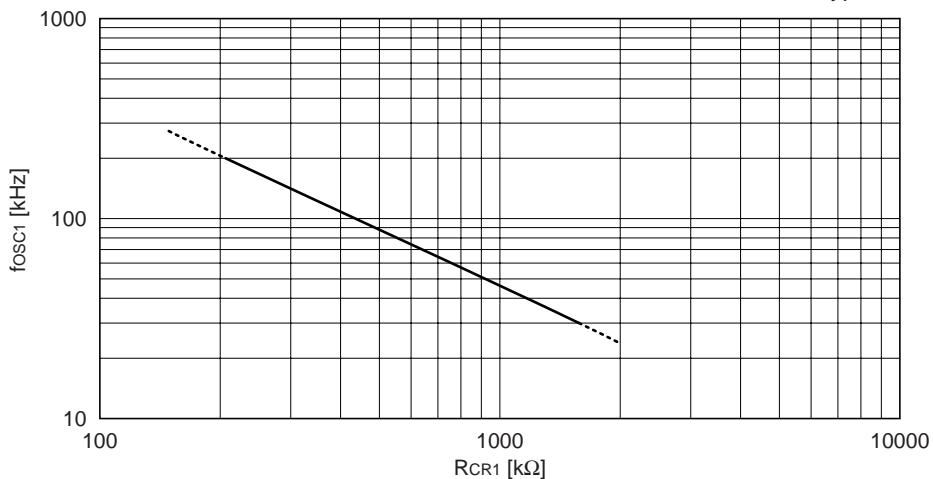

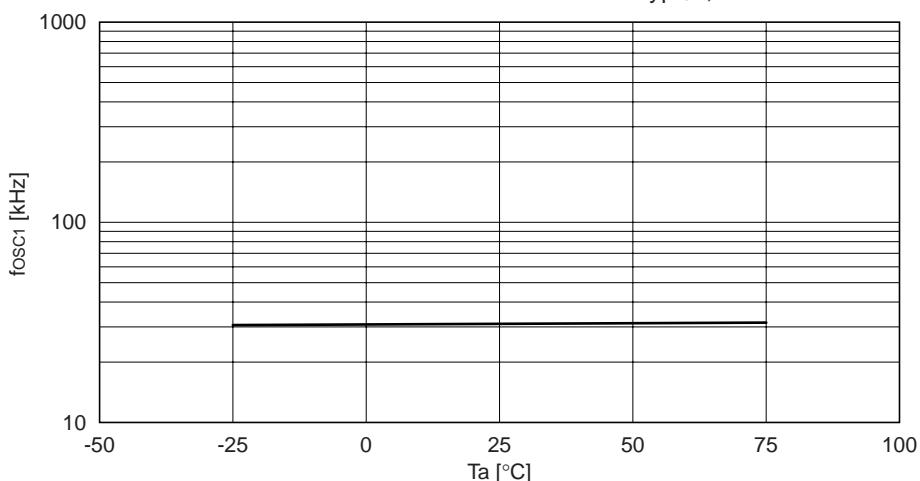

| サブ(OSC1)発振回路  | 水晶発振回路 32.768kHz (Typ.)、またはCR発振回路 200kHz (Max.)                                                                                                                                                                                                                                                                                                                                                                                          |

| 命令セット         | 608種類 (乘除算命令使用可能)                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 最小命令実行時間      | 0.244μsec/8.2MHz (2クロック)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 内蔵ROM容量       | 48Kバイト/プログラムROM<br>896Kバイト/漢字フォント用ROM (フォント未格納時、プログラムおよびデータ格納用として使用可能)                                                                                                                                                                                                                                                                                                                                                                   |

| 内蔵RAM容量       | 8Kバイト/RAM 768バイト/表示メモリ                                                                                                                                                                                                                                                                                                                                                                                                                   |

| バスライン         | アドレスバス: 20ビット (バスとして使用しない場合は汎用出力ポートとして使用可能)<br>データバス: 8ビット (バスとして使用しない場合は汎用入出力ポートとして使用可能)<br>CE信号: 3ビット<br>WR信号: 1ビット<br>RD信号: 1ビット (バスとして使用しない場合は汎用出力ポートとして使用可能)                                                                                                                                                                                                                                                                        |

| 入力ポート         | 8ビット (4ビットをPWMタイマの源振クロック、1ビットをバスリクエスト信号入力として使用可能)                                                                                                                                                                                                                                                                                                                                                                                        |

| 出力ポート         | 0ビット～3ビット (外部バスを使用する場合) (1ビットをバスアクノリッジ信号出力に設定可能)<br>26ビット (外部バスを使用しない場合)                                                                                                                                                                                                                                                                                                                                                                 |

| 入出力兼用ポート      | 8ビット (外部バスを使用する場合) (シリアルI/F、FOUT、TOUT出力と端子を兼用)<br>16ビット (外部バスを使用しない場合)                                                                                                                                                                                                                                                                                                                                                                   |

| シリアルインターフェース  | 1ch (クロック同期式/調歩同期式の選択が可能)                                                                                                                                                                                                                                                                                                                                                                                                                |

| タイマ           | プログラマブルタイマ: 16ビット(8ビット×2) 4ch (PWM機能付き)<br>計時タイマ: 1ch                                                                                                                                                                                                                                                                                                                                                                                    |

| LCDドライバ       | ドットマトリクス方式 (16×16/5×8または12×12ドットフォント)<br>126セグメント×32、16または8コモン (1/5バイアス)<br>LCD電源回路内蔵 (5電位昇圧タイプ)                                                                                                                                                                                                                                                                                                                                         |

| ウォッチドッグタイマ    | 内蔵 (1～8秒周期)                                                                                                                                                                                                                                                                                                                                                                                                                              |

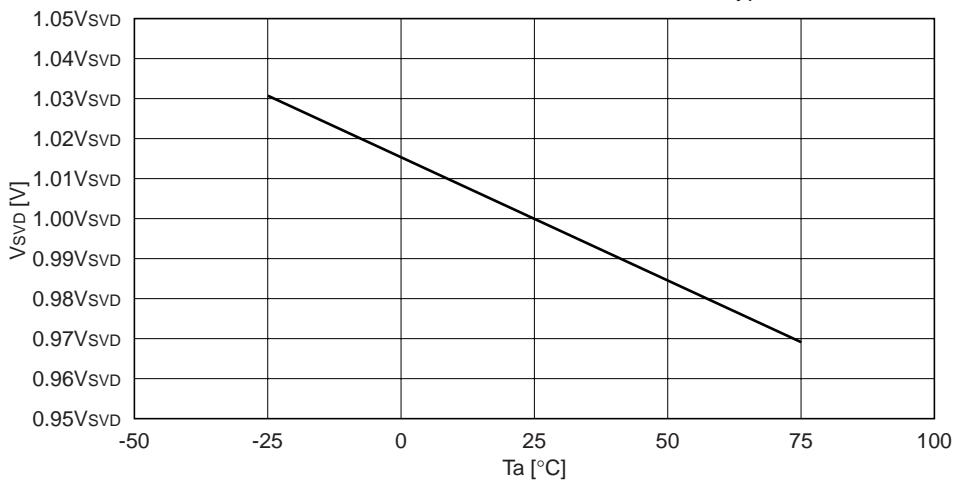

| 電源電圧検出回路(SVD) | 13値プログラマブル (1.8～2.7V)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 割り込み          | 外部割り込み: 入力割り込み 1系統 (8種類)<br>内部割り込み: タイマ割り込み 2系統 (16種類)<br>シリアルインターフェース割り込み 1系統 (3種類)                                                                                                                                                                                                                                                                                                                                                     |

| 電源電圧          | 1.8V～3.6V                                                                                                                                                                                                                                                                                                                                                                                                                                |

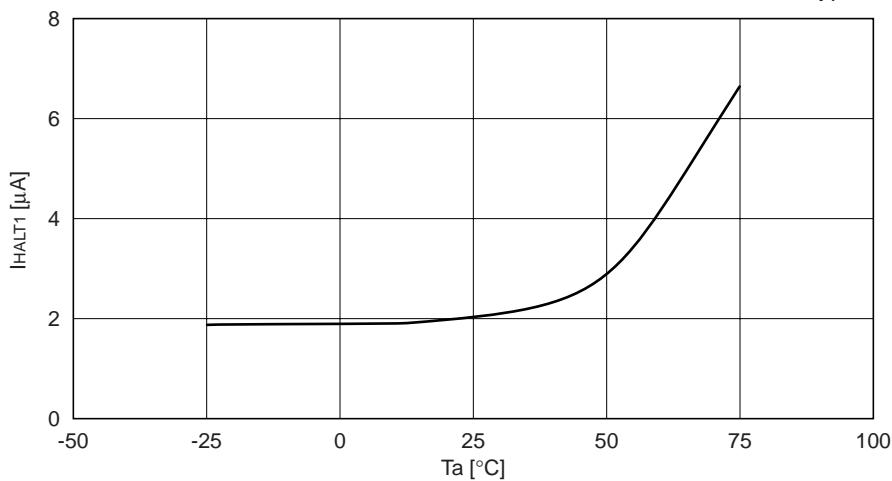

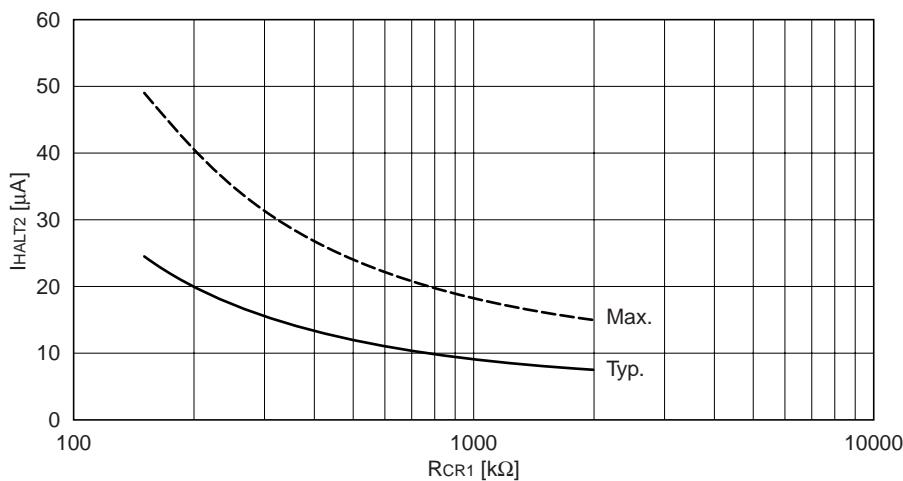

| 消費電流          | SLEEP時: 1μA (Typ.)<br>HALT時: 2.5μA (Typ.) 32kHz 水晶発振、LCD OFF<br>10μA (Typ.) 32kHz CR発振、LCD OFF<br>7.6μA (Typ.) 32kHz 水晶発振、LCD ON*、VDD=2.5～3.6V<br>実行時: 9μA (Typ.) 32kHz 水晶発振、LCD OFF<br>15μA (Typ.) 32kHz CR発振、LCD OFF<br>1700μA (Typ.) 8MHz セラミック発振、LCD OFF<br>600μA (Typ.) 2MHz CR発振、LCD OFF<br>14μA (Typ.) 32kHz 水晶発振、LCD ON*、VDD=2.5～3.6V<br>19μA (Typ.) 32kHz 水晶発振、LCD ON*、VDD=1.8～2.5V、電源電圧昇圧回路ON<br>14μA (Typ.) 32kHz 水晶発振、SVD ON |

| 出荷形態          | QFP22-256pinプラスチックパッケージまたはチップ                                                                                                                                                                                                                                                                                                                                                                                                            |

\* LCD ON時の消費電流は、LCDCx = 全点灯、LCx = FH、パネル負荷なしの場合です。消費電流は表示パターン、パネル負荷によって増加します。

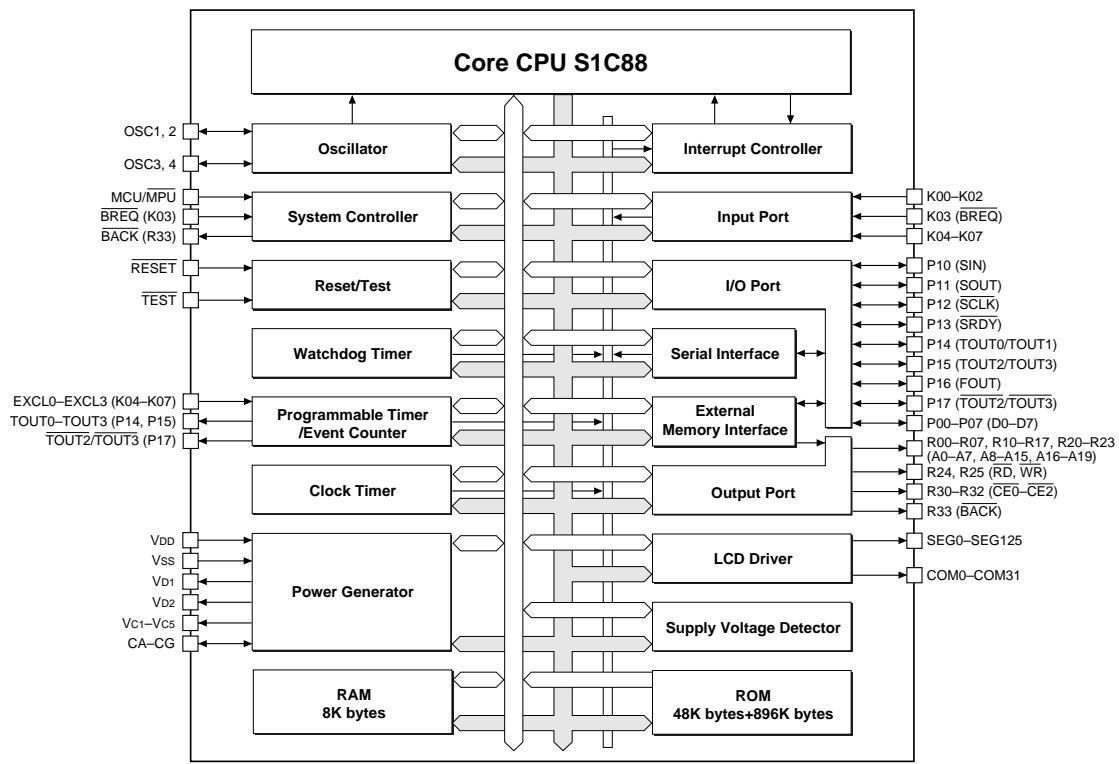

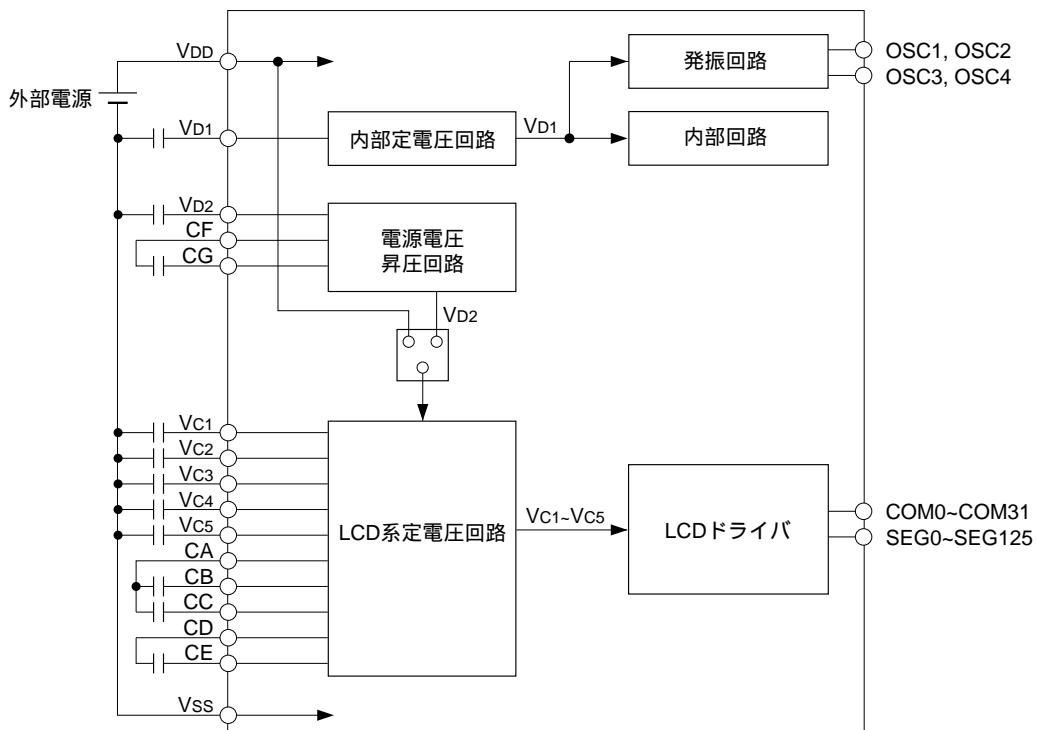

## 1.2 ブロック図

図1.2.1 S1C88650ブロック図

## 1.3 端子

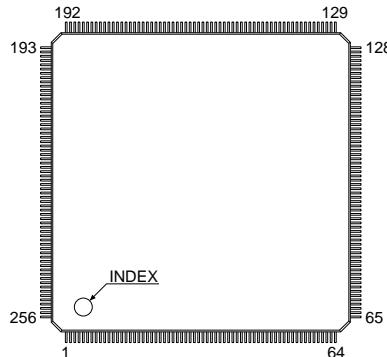

### 1.3.1 端子配置図

QFP22-256pin

| 端子No. | 端子名   | 端子No. | 端子名             | 端子No. | 端子名             | 端子No. | 端子名             | 端子No. | 端子名             |

|-------|-------|-------|-----------------|-------|-----------------|-------|-----------------|-------|-----------------|

| 1     | N.C.  | 53    | SEG88           | 105   | COM23           | 157   | P07/D7          | 209   | COM11           |

| 2     | N.C.  | 54    | SEG89           | 106   | COM22           | 158   | P06/D6          | 210   | COM12           |

| 3     | TEST  | 55    | SEG90           | 107   | COM21           | 159   | P05/D5          | 211   | COM13           |

| 4     | SEG39 | 56    | SEG91           | 108   | COM20           | 160   | P04/D4          | 212   | COM14           |

| 5     | SEG40 | 57    | SEG92           | 109   | COM19           | 161   | P03/D3          | 213   | COM15           |

| 6     | SEG41 | 58    | SEG93           | 110   | COM18           | 162   | P02/D2          | 214   | SEG0            |

| 7     | SEG42 | 59    | SEG94           | 111   | COM17           | 163   | P01/D1          | 215   | SEG1            |

| 8     | SEG43 | 60    | SEG95           | 112   | COM16           | 164   | P00/D0          | 216   | SEG2            |

| 9     | SEG44 | 61    | SEG96           | 113   | V <sub>D2</sub> | 165   | R00/A0          | 217   | SEG3            |

| 10    | SEG45 | 62    | N.C.            | 114   | CG              | 166   | R01/A1          | 218   | SEG4            |

| 11    | SEG46 | 63    | N.C.            | 115   | CF              | 167   | R02/A2          | 219   | SEG5            |

| 12    | SEG47 | 64    | N.C.            | 116   | CE              | 168   | R03/A3          | 220   | SEG6            |

| 13    | SEG48 | 65    | N.C.            | 117   | CD              | 169   | R04/A4          | 221   | SEG7            |

| 14    | SEG49 | 66    | N.C.            | 118   | CC              | 170   | R05/A5          | 222   | SEG8            |

| 15    | SEG50 | 67    | V <sub>ss</sub> | 119   | CB              | 171   | R06/A6          | 223   | SEG9            |

| 16    | SEG51 | 68    | SEG97           | 120   | CA              | 172   | R07/A7          | 224   | SEG10           |

| 17    | SEG52 | 69    | SEG98           | 121   | V <sub>C5</sub> | 173   | R10/A8          | 225   | SEG11           |

| 18    | SEG53 | 70    | SEG99           | 122   | V <sub>C4</sub> | 174   | R11/A9          | 226   | SEG12           |

| 19    | SEG54 | 71    | SEG100          | 123   | V <sub>C3</sub> | 175   | R12/A10         | 227   | SEG13           |

| 20    | SEG55 | 72    | SEG101          | 124   | V <sub>C2</sub> | 176   | R13/A11         | 228   | SEG14           |

| 21    | SEG56 | 73    | SEG102          | 125   | V <sub>C1</sub> | 177   | R14/A12         | 229   | SEG15           |

| 22    | SEG57 | 74    | SEG103          | 126   | N.C.            | 178   | R15/A13         | 230   | SEG16           |

| 23    | SEG58 | 75    | SEG104          | 127   | N.C.            | 179   | R16/A14         | 231   | SEG17           |

| 24    | SEG59 | 76    | SEG105          | 128   | N.C.            | 180   | R17/A15         | 232   | SEG18           |

| 25    | SEG60 | 77    | SEG106          | 129   | N.C.            | 181   | R20/A16         | 233   | SEG19           |

| 26    | SEG61 | 78    | SEG107          | 130   | N.C.            | 182   | R21/A17         | 234   | SEG20           |

| 27    | SEG62 | 79    | SEG108          | 131   | V <sub>DD</sub> | 183   | R22/A18         | 235   | SEG21           |

| 28    | SEG63 | 80    | SEG109          | 132   | OSC3            | 184   | R23/A19         | 236   | SEG22           |

| 29    | SEG64 | 81    | SEG110          | 133   | OSC4            | 185   | R24/RD          | 237   | SEG23           |

| 30    | SEG65 | 82    | SEG111          | 134   | V <sub>ss</sub> | 186   | R25/WR          | 238   | SEG24           |

| 31    | SEG66 | 83    | SEG112          | 135   | V <sub>D1</sub> | 187   | R30/CEO         | 239   | SEG25           |

| 32    | SEG67 | 84    | SEG113          | 136   | OSC1            | 188   | R31/CE1         | 240   | SEG26           |

| 33    | SEG68 | 85    | SEG114          | 137   | OSC2            | 189   | V <sub>DD</sub> | 241   | SEG27           |

| 34    | SEG69 | 86    | SEG115          | 138   | TEST            | 190   | N.C.            | 242   | SEG28           |

| 35    | SEG70 | 87    | SEG116          | 139   | RESET           | 191   | N.C.            | 243   | SEG29           |

| 36    | SEG71 | 88    | SEG117          | 140   | MCU/MPU         | 192   | N.C.            | 244   | SEG30           |

| 37    | SEG72 | 89    | SEG118          | 141   | K07/EXCL3       | 193   | N.C.            | 245   | SEG31           |

| 38    | SEG73 | 90    | SEG119          | 142   | K06/EXCL2       | 194   | N.C.            | 246   | SEG32           |

| 39    | SEG74 | 91    | SEG120          | 143   | K05/EXCL1       | 195   | V <sub>ss</sub> | 247   | SEG33           |

| 40    | SEG75 | 92    | SEG121          | 144   | K04/EXCL0       | 196   | R32/CE2         | 248   | SEG34           |

| 41    | SEG76 | 93    | SEG122          | 145   | K03/BREQ        | 197   | R33/BACK        | 249   | SEG35           |

| 42    | SEG77 | 94    | SEG123          | 146   | K02             | 198   | COM0            | 250   | SEG36           |

| 43    | SEG78 | 95    | SEG124          | 147   | K01             | 199   | COM1            | 251   | SEG37           |

| 44    | SEG79 | 96    | SEG125          | 148   | K00             | 200   | COM2            | 252   | SEG38           |

| 45    | SEG80 | 97    | COM31           | 149   | P17/TOUT2/TOUT3 | 201   | COM3            | 253   | V <sub>ss</sub> |

| 46    | SEG81 | 98    | COM30           | 150   | P16/FOUT        | 202   | COM4            | 254   | N.C.            |

| 47    | SEG82 | 99    | COM29           | 151   | P15/TOUT2/TOUT3 | 203   | COM5            | 255   | N.C.            |

| 48    | SEG83 | 100   | COM28           | 152   | P14/TOUT0/TOUT1 | 204   | COM6            | 256   | N.C.            |

| 49    | SEG84 | 101   | COM27           | 153   | P13/SRDY        | 205   | COM7            | —     | —               |

| 50    | SEG85 | 102   | COM26           | 154   | P12/SCLK        | 206   | COM8            | —     | —               |

| 51    | SEG86 | 103   | COM25           | 155   | P11/SOUT        | 207   | COM9            | —     | —               |

| 52    | SEG87 | 104   | COM24           | 156   | P10/SIN         | 208   | COM10           | —     | —               |

図1.3.1.1 S1C88650端子配置図

### 1.3.2 端子説明

表1.3.2.1 S1C88650端子説明

| 端子名             | 端子No.                | In/Out | 機能                                                       |

|-----------------|----------------------|--------|----------------------------------------------------------|

| VDD             | 131, 189             | -      | 電源(+)端子                                                  |

| VSS             | 67, 134, 195, 253    | -      | 電源(GND)端子                                                |

| VD1             | 135                  | -      | 内部ロジックおよび発振系定電圧回路出力端子                                    |

| VD2             | 113                  | -      | LCD回路用電源昇圧出力端子                                           |

| VC1~VC5         | 125~121              | -      | LCD系駆動電圧出力端子                                             |

| CA-CG           | 120~114              | -      | LCD昇圧コンデンサ接続端子/電源電圧昇圧コンデンサ接続端子                           |

| OSC1            | 136                  | I      | OSC1発振入力端子(水晶/CR発振をマスクオプションで選択)                          |

| OSC2            | 137                  | O      | OSC1発振出力端子                                               |

| OSC3            | 132                  | I      | OSC3発振入力端子(水晶/セラミック/CR発振をマスクオプションで選択)                    |

| OSC4            | 133                  | O      | OSC3発振出力端子                                               |

| MCU/MPU         | 140                  | I      | MCUモード MPUモード設定端子                                        |

| K00~K02         | 148~146              | I      | 入力ポート(K00 ~ K02)端子                                       |

| K03/BREQ        | 145                  | I      | 入力ポート(K03)端子またはバスリクエスト信号(BREQ)入力端子                       |

| K04/EXCL0       | 144                  | I      | 入力ポート(K04)端子またはプログラマブルタイマ外部クロック(EXCL0)入力端子               |

| K05/EXCL1       | 143                  | I      | 入力ポート(K05)端子またはプログラマブルタイマ外部クロック(EXCL1)入力端子               |

| K06/EXCL2       | 142                  | I      | 入力ポート(K06)端子またはプログラマブルタイマ外部クロック(EXCL2)入力端子               |

| K07/EXCL3       | 141                  | I      | 入力ポート(K07)端子またはプログラマブルタイマ外部クロック(EXCL3)入力端子               |

| R00~R07/A0~A7   | 165~172              | O      | 出力ポート(R00 ~ R07)端子またはアドレスバス(A0 ~ A7)                     |

| R10~R17/A8~A15  | 173~180              | O      | 出力ポート(R10 ~ R17)端子またはアドレスバス(A8 ~ A15)                    |

| R20~R23/A16~A19 | 181~184              | O      | 出力ポート(R20 ~ R23)端子またはアドレスバス(A16 ~ A19)                   |

| R24/RD          | 185                  | O      | 出力ポート(R24)端子またはリード信号(RD)出力端子                             |

| R25/WR          | 186                  | O      | 出力ポート(R25)端子またはライト信号(WR)出力端子                             |

| R30~R32/CE0~CE2 | 187, 188, 196        | O      | 出力ポート(R30 ~ R32)端子またはチップインターフェース信号(CE0 ~ CE2)出力端子        |

| R33(BACK)       | 197                  | O      | 出力ポート(R33)端子またはバスアケノリッジ信号(BACK)出力端子                      |

| P00~P07/D0~D7   | 164~157              | I/O    | 入出力兼用ポート(P00 ~ P07)端子またはデータバス(D0 ~ D7)                   |

| P10/SIN         | 156                  | I/O    | 入出力兼用ポート(P10)端子またはシリアルI/Fデータ入力(SIN)端子                    |

| P11/SOUT        | 155                  | I/O    | 入出力兼用ポート(P11)端子またはシリアルI/Fデータ出力(SOUT)端子                   |

| P12/SCLK        | 154                  | I/O    | 入出力兼用ポート(P12)端子またはシリアルI/Fクロック(SCLK)入出力端子                 |

| P13/SRDY        | 153                  | I/O    | 入出力兼用ポート(P13)端子またはシリアルI/Fレディ信号(SRDY)出力端子                 |

| P14/TOUT0/TOUT1 | 152                  | I/O    | 入出力兼用ポート(P14)端子またはプログラマブルタイマアンダーフロー信号(TOUT0/TOUT1)出力端子   |

| P15/TOUT2/TOUT3 | 151                  | I/O    | 入出力兼用ポート(P15)端子またはプログラマブルタイマアンダーフロー信号(TOUT2/TOUT3)出力端子   |

| P16/FOUT        | 150                  | I/O    | 入出力兼用ポート(P16)端子またはクロック(FOUT)出力端子                         |

| P17/TOUT2/TOUT3 | 149                  | I/O    | 入出力兼用ポート(P17)端子またはプログラマブルタイマアンダーフロー反転信号(TOUT2/TOUT3)出力端子 |

| COM0~COM31      | 198~213, 112~97      | O      | LCDコモン出力端子                                               |

| SEG0~SEG125     | 214~252, 4~61, 68~96 | O      | LCDセグメント出力端子                                             |

| RESET           | 139                  | I      | イニシャルリセット入力端子                                            |

| TEST            | 138                  | I      | テスト用入力端子                                                 |

| TEST            | 3                    | -      | テスト端子(通常動作時はオープン)                                        |

## 1.4 マスクオプション

S1C88650には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。本マニュアルの回路説明を参照してシステムに合った内容を選択し、**■**に印をつけてください。

なお、使用しない機能についても解説にしたがって必ず記入してください。

このオプションリストを参照して、マスクオプション選択をファンクションオプションジェネレータwinfogの画面上で行います。winfogによって作成したデータをもとに最終的なICのマスクパターンが生成されます。winfogについては"S5U1C88000C Manual II"を参照してください。

### RERIPHERAL CIRCUIT BOARDオプションリスト

ICE (S5U1C88000H5)に組み込むPeripheral Circuit Board (S5U1C88000P1&S5U1C88649P2)に対して設定できるオプションです。ICのマスクオプションには影響ありません。

#### A OSC1発振回路

##### OSC1 SYSTEM CLOCK

- 1. 内部クロック

- 2. ユーザクロック

ユーザクロックを選択した場合、OSC1端子から任意のクロックを入力してください。また、内部クロックを選択した場合、ICのマスクオプションリストによって選択された発振回路オプションにより、使用できる周波数が異なります。

#### B OSC3発振回路

##### OSC3 SYSTEM CLOCK

- 1. 内部クロック

- 2. ユーザクロック

ユーザクロックを選択した場合、OSC3端子から任意のクロックを入力してください。また、内部クロックを選択した場合、ICのマスクオプションリストによって選択された発振回路オプションにより、使用できる周波数が異なります。

### S1C88650マスクオプションリスト

ICのマスクパターンを生成するためのオプションリストです。ICEに組み込むPeripheral Circuit Boardにおいては一部選択できない項目があります。

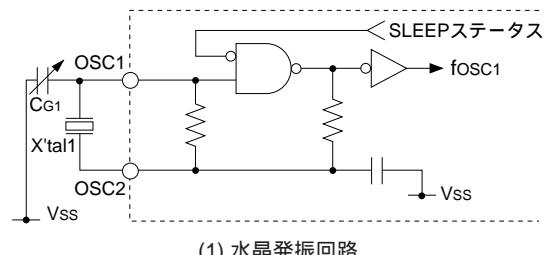

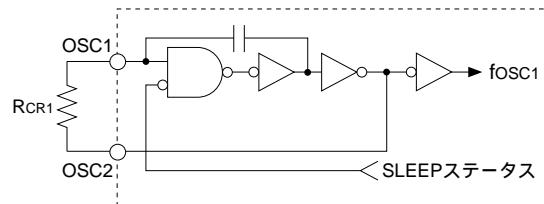

#### 1 OSC1発振回路

##### OSC1 SYSTEM CLOCK

- 1. 水晶発振回路

- 2. CR発振回路

OSC1発振回路の種類を、水晶発振、CR発振から選択できます。詳細については、"5.4.3 OSC1発振回路"を参照してください。

#### 2 OSC3発振回路

##### OSC3 SYSTEM CLOCK

- 1. 水晶発振回路

- 2. セラミック発振回路

- 3. CR発振回路

OSC3発振回路の種類を、水晶発振、セラミック発振、CR発振から選択できます。詳細については、"5.4.4 OSC3発振回路"を参照してください。

#### 3 キー同時押しリセット

##### MULTIPLE KEY ENTRY RESET

- ・組み合わせ ..

- 1. 使用しない

- 2. 使用する K00, K01

- 3. 使用する K00, K01, K02

- 4. 使用する K00, K01, K02, K03

複数キーの同時押しによってICをリセットする機能を使用するかしないかをマスクオプションで選択できます。使用する場合は、キーを接続する入力ポート(K00 ~ K03)の組み合わせを選択します。詳細については"4.1.2 入力ポート(K00 ~ K03)の同時LOWレベル入力"を参照してください。

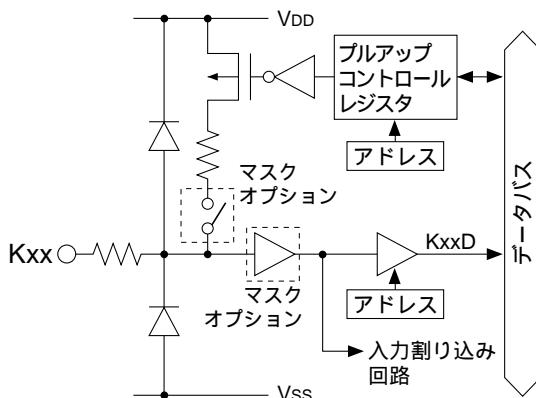

#### 4 入力ポートプルアップ抵抗

##### INPUT PORT PULL UP RESISTOR

- |              |         |         |

|--------------|---------|---------|

| ・K00 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K01 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K02 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K03 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K04 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K05 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K06 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・K07 .....   | 1. 抵抗あり | 2. 抵抗なし |

| ・MCU/MPU ... | 1. 抵抗あり | 2. 抵抗なし |

| ・RESET ..... | 1. 抵抗あり | 2. 抵抗なし |

入力(K)ポートにプルアップ抵抗を付加するかしないか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"5.5 入力ポート(Kポート)"を参照してください。

また、MCU/MPU端子およびRESET端子にもプルアップ抵抗を付加するかしないか選択できます。

## 5 入出力兼用ポートプルアップ抵抗

## I/O PORT PULL UP RESISTOR

- |             |         |         |

|-------------|---------|---------|

| • P00 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P01 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P02 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P03 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P04 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P05 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P06 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P07 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P10 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P11 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P12 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P13 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P14 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P15 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P16 ..... | 1. 抵抗あり | 2. 抵抗なし |

| • P17 ..... | 1. 抵抗あり | 2. 抵抗なし |

入出力兼用(P)ポートが入力モード時に働くプルアップ抵抗を付加するかしないか選択できます。この選択は入出力兼用ポートの各ビットごとに行えます。詳細については"5.7 入出力兼用ポート(Pポート)"を参照してください。

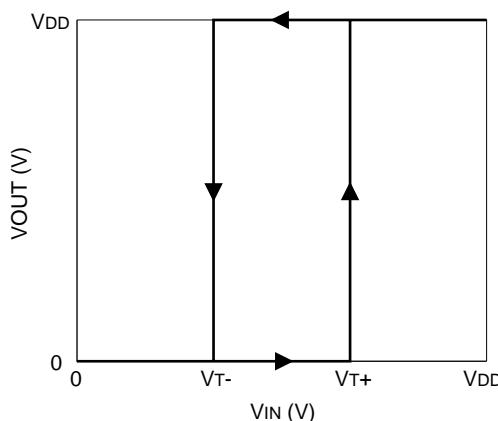

## 6 入力ポート入力インターフェースレベル

## INPUT PORT INPUT I/F LEVEL

- |             |            |              |

|-------------|------------|--------------|

| • K00 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K01 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K02 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K03 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K04 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K05 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K06 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • K07 ..... | 1. CMOSレベル | 2. CMOSシユミット |

入力(K)ポートの入力インターフェースレベルをCMOSレベルにするか、CMOSシユミットレベルにするか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"5.5 入力ポート(Kポート)"を参照してください。ICEでは、このオプションの選択にかかわらずCMOSレベル固定になります。

## 7 入出力兼用ポート入力インターフェースレベル

## I/O PORT INPUT I/F LEVEL

- |             |            |              |

|-------------|------------|--------------|

| • P10 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P11 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P12 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P13 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P14 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P15 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P16 ..... | 1. CMOSレベル | 2. CMOSシユミット |

| • P17 ..... | 1. CMOSレベル | 2. CMOSシユミット |

入出力兼用(P)ポートの入力インターフェースレベルをCMOSレベルにするか、CMOSシユミットレベルにするか選択できます。この選択は入出力兼用ポートの各ビットごとに行えます。詳細については"5.7 入出力兼用ポート(Pポート)"を参照してください。ICEでは、このオプションの選択にかかわらずCMOSレベル固定になります。

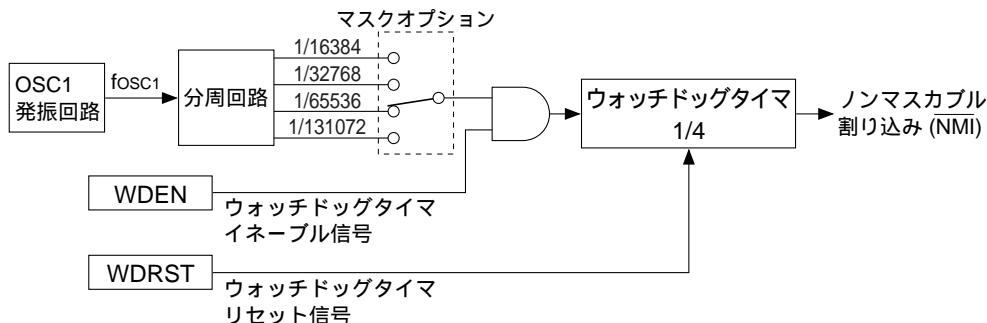

## 8 ウォッチドッグタイマNMI発生周期

## WATCHDOG TIMER NMI GENERATION CYCLE

1. 32768/fosc1

(fosc1=32kHz時 0.75 ~ 1秒周期)

2. 65536/fosc1

(fosc1=32kHz時 1.5 ~ 2秒周期)

3. 131072/fosc1

(fosc1=32kHz時 3 ~ 4秒周期)

4. 262144/fosc1

(fosc1=32kHz時 6 ~ 8秒周期)

ウォッチドッグタイマのNMI発生周期を選択することができます。詳細については"5.3.1 ウォッチドッグタイマの構成"を参照してください。

## 2 電源

ここでは、S1C88650の動作電圧、および内部電源回路の構成について説明します。

### 2.1 動作電圧

S1C88650の動作電源電圧は次のとおりです。

1.8V ~ 3.6V

### 2.2 内部電源回路

S1C88650は図2.2.1に示す電源回路を内蔵しております。前記の範囲内の電圧をVDD(+)、Vss(GND)間に供給することによって内部回路に必要なすべての電圧をIC内部で発生します。

電源回路は大きく3つに分けられます。

表2.2.1 電源回路

| 回路系       | 電源回路      | 出力電圧                               |

|-----------|-----------|------------------------------------|

| 発振回路、内部回路 | 内部定電圧回路   | V <sub>D1</sub>                    |

| LCD系定電圧回路 | 電源電圧昇圧回路  | V <sub>D2</sub> またはV <sub>D1</sub> |

| LCDドライバ   | LCD系定電圧回路 | V <sub>C1</sub> ~V <sub>C5</sub>   |

内部定電圧回路は、内部ロジック回路と発振回路の動作電圧<V<sub>D1</sub>>を発生します。

V<sub>D1</sub>の電圧値は1.8V(Typ.)に固定されています。

電源電圧昇圧回路は、LCD系定電圧回路の動作電圧<V<sub>D2</sub>>を発生します。

電源電圧<V<sub>DD</sub>>に応じて、LCD系定電圧回路の電源として、<V<sub>DD</sub>>を供給するか<V<sub>D2</sub>>を供給するかを選択します。

表2.2.2 LCD系定電圧回路の電源

| 電源電圧 V <sub>DD</sub> | LCD系定電圧回路電源     |

|----------------------|-----------------|

| 1.8 ~ 2.5V           | V <sub>D2</sub> |

| 2.5 ~ 3.6V           | V <sub>DD</sub> |

V<sub>D2</sub>の電圧値はV<sub>DD</sub>のおおよそ2倍の値になります。詳細については"8 電気的特性"を参照してください。

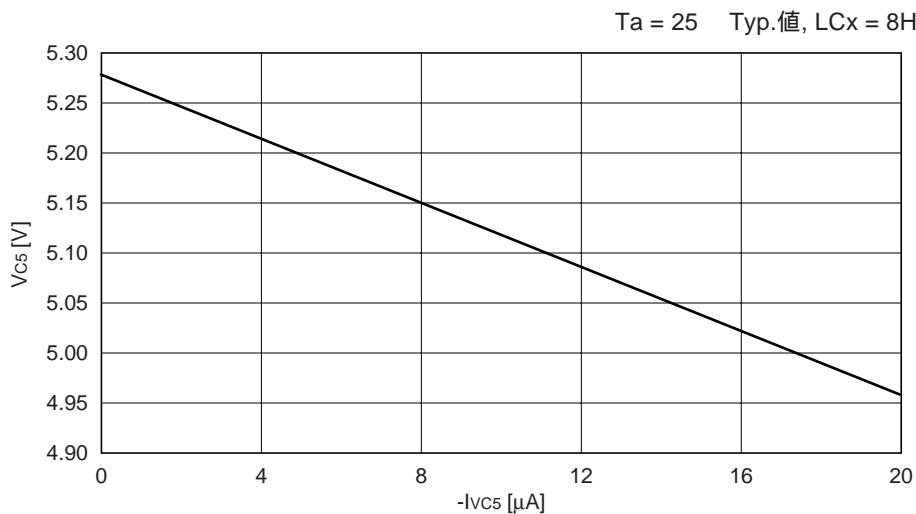

LCD系定電圧回路はLCDの1/5バイアス用駆動電圧<V<sub>C1</sub>>、<V<sub>C2</sub>>、<V<sub>C3</sub>>、<V<sub>C4</sub>>、<V<sub>C5</sub>>を発生します。各電圧値については"8 電気的特性"を参照してください。

S1C88650では、内蔵されたLCDドライバにこのLCD駆動電圧が供給され、コモン/セグメント端子に接続されたLCDパネルを駆動します。

- 注!

- V<sub>D1</sub>、V<sub>D2</sub>、V<sub>C1</sub>、V<sub>C2</sub>、V<sub>C3</sub>、V<sub>C4</sub>、V<sub>C5</sub>端子の出力を外部回路の駆動には絶対に使用しないでください。

- V<sub>DD</sub> = 2.5V以下のときにLCD系定電圧回路の電源としてV<sub>DD</sub>を使用すると、V<sub>C1</sub>~V<sub>C5</sub>の電圧は正しい電圧とはなりません。

図2.2.1 電源回路の構成

# 3 CPUとバスの構成

ここでは、CPUと動作モード、およびバスの構成について説明します。

## 3.1 CPU

S1C88650はCPUとして8ビットコアCPU S1C88を使用しており、レジスタ構成、命令等は他のS1C88を使用したファミリプロセッサとほぼ同様です。S1C88については"S1C88コアCPUマニュアル"を参照してください。

使用しているS1C88のCPUモデルはMODEL3で、S1C88650の場合、アドレス空間は最大1Mバイト×3となっています。

## 3.2 内蔵メモリ

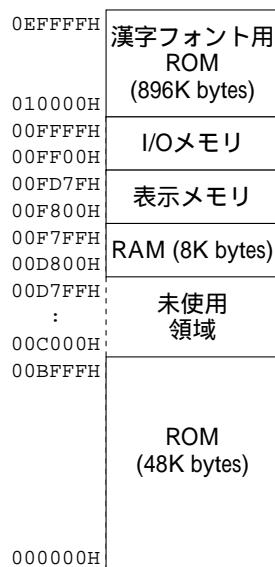

S1C88650は図3.2.1に示すROMおよびRAMを内蔵しており、小規模なアプリケーションには1チップで対応することができます。この内蔵メモリは外部メモリと合わせて使用可能です。また、内蔵ROMをバスから切り離して、所定の空間を外部に解放することもできます。

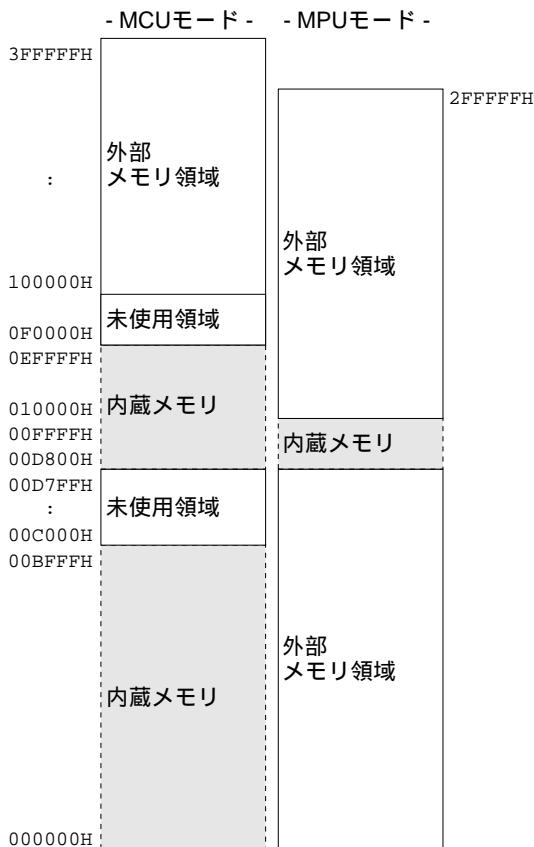

図3.2.1 内蔵メモリマップ

### 3.2.1 プログラムROM

内蔵プログラムROMの容量は48Kバイトで、000000H～00BFFFHに配置されています。

このROM領域はMCU/MPU端子の設定によって、外部メモリに解放することができます("3.5 チップモード"参照)。

### 3.2.2 RAM

内蔵RAMの容量は8Kバイトで、00D800H～00F7FFFHに配置されています。

なお、内蔵RAM領域に外部メモリを拡張した場合でも、この領域は外部メモリには解放されません。この領域のアクセスは常に内蔵RAMに対して行われます。

### 3.2.3 I/Oメモリ

S1C88650では、内蔵する周辺回路とのインターフェースにメモリマップドI/O方式を採用しています。各周辺回路の制御ビットやデータレジスタはメモリ空間上に配置され、通常のメモリアクセスによって制御およびデータのやりとりが行えます。I/Oメモリが配置されている領域は00FF00H～00FFFFHです。I/Oメモリの詳細については"5.1 I/Oメモリマップ"を参照してください。

なお、I/Oメモリ領域に外部メモリを拡張した場合でも、この領域は外部メモリには解放されません。この領域のアクセスは常にI/Oメモリに対して行われます。

### 3.2.4 表示メモリ

S1C88650はLCDドライバの表示データを保持する表示メモリを内蔵しています。表示メモリが配置されている領域は00Fx00H～00Fx7FH(x=8～DH)です。表示メモリの詳細については"5.11 LCD ドライバ"を参照してください。

表示メモリの領域もI/Oメモリと同様に外部メモリには解放されません。

### 3.2.5 漢字フォント用ROM

S1C88650は、JIS第1水準、JIS第2水準、非漢字のフォントおよびMusic shift JISフォントのデータを格納するための漢字フォント用ROMを内蔵しています。

ROMの容量は896Kバイトで、010000H～0EFFFFHに配置されています。

このROMは、漢字フォントを使用しない場合や、フォントデータの未使用領域をプログラムおよびデータ格納用として使用することができます(フォントデータの取り扱いに関しては、"S5U1C88xxxRx Manual"を参照)。

このROM領域はMCU/MPU端子の設定によって、外部メモリに解放することができます("3.5 チップモード"参照)。

### 3.3 例外処理ベクタ

S1C88650ではプログラム領域の000000H～00004BHが例外処理ベクタとして割り当てられています。また、00004EH～0000FFHまでは任意の偶数番地から始まる2バイトにソフトウェア割り込みのベクタを割り付けることができます。

表3.3.1にベクタアドレスと例外処理要因の対応を示します。

表3.3.1 ベクタアドレスと例外処理要因の対応

| ベクタアドレス | 例外処理要因           | 優先順位 |

|---------|------------------|------|

| 000000H | リセット             | 高い   |

| 000002H | ゼロ除算             |      |

| 000004H | ウォッチドッグタイマ(NMI)  |      |

| 000006H | K07入力割り込み        |      |

| 000008H | K06入力割り込み        |      |

| 00000AH | K05入力割り込み        |      |

| 00000CH | K04入力割り込み        |      |

| 00000EH | K03入力割り込み        |      |

| 000010H | K02入力割り込み        |      |

| 000012H | K01入力割り込み        |      |

| 000014H | K00入力割り込み        |      |

| 000016H | Pタイマ0アンダーフロー割り込み |      |

| 000018H | Pタイマ0コンペアマッチ割り込み |      |

| 00001AH | Pタイマ1アンダーフロー割り込み |      |

| 00001CH | Pタイマ1コンペアマッチ割り込み |      |

| 00001EH | Pタイマ2アンダーフロー割り込み |      |

| 000020H | Pタイマ2コンペアマッチ割り込み |      |

| 000022H | Pタイマ3アンダーフロー割り込み |      |

| 000024H | Pタイマ3コンペアマッチ割り込み |      |

| 000026H | システム予約(使用不可)     |      |

| 000028H | シリアルI/Fエラー割り込み   |      |

| 00002AH | シリアルI/F受信完了割り込み  |      |

| 00002CH | シリアルI/F送信完了割り込み  |      |

| 00002EH | システム予約(使用不可)     |      |

| 000030H | システム予約(使用不可)     |      |

| 000032H | システム予約(使用不可)     |      |

| 000034H | 計時タイマ32Hz割り込み    |      |

| 000036H | 計時タイマ8Hz割り込み     |      |

| 000038H | 計時タイマ2Hz割り込み     |      |

| 00003AH | 計時タイマ1Hz割り込み     |      |

| 00003CH | Pタイマ4アンダーフロー割り込み |      |

| 00003EH | Pタイマ4コンペアマッチ割り込み |      |

| 000040H | Pタイマ5アンダーフロー割り込み |      |

| 000042H | Pタイマ5コンペアマッチ割り込み |      |

| 000044H | Pタイマ6アンダーフロー割り込み |      |

| 000046H | Pタイマ6コンペアマッチ割り込み |      |

| 000048H | Pタイマ7アンダーフロー割り込み |      |

| 00004AH | Pタイマ7コンペアマッチ割り込み |      |

| 00004CH | システム予約(使用不可)     |      |

| 00004EH | ソフトウェア割り込み       | なし   |

| 0000FEH |                  |      |

各ベクタアドレスとその次のアドレスに、例外処理ルーチンの先頭アドレスを下位、上位の順に格納しておきます。例外処理要因が発生すると、設定されたアドレスから始まる例外処理ルーチンを実行します。

同時に複数の例外処理が発生した場合は優先順位の高いものから先に実行されます。

なお、表3.3.1に示された割り込みの優先順位は、割り込み優先レベルがすべて同じ場合のものです。各割り込みの優先レベルは系列ごとにソフトウェアで設定することができます。(“5.14 割り込みとスタンバイ状態”参照)

注! リセット以外の例外処理ではSC(システムコンディションフラグ)およびPC(プログラムカウンタ)をスタックに退避させ、各例外処理ルーチンに分岐します。したがって、例外処理ルーチンからメインルーチンに戻す際にはRETE命令を使用してください。

例外処理要因発生時のCPUの動作については“S1C88コアCPUマニュアル”を参照してください。

### 3.4 CC(カスタマイズコンディションフラグ)

S1C88650ではコアCPU内のカスタマイズコンディションフラグ(CC)を使用していません。したがって、条件付き分岐命令(JRS、CARS)の分岐条件として使用することはできません。

## 3.5 チップモード

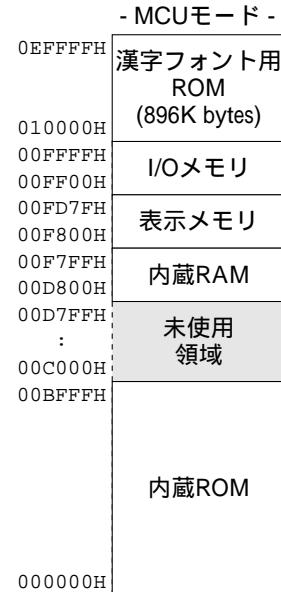

### 3.5.1 MCUモードとMPUモード

S1C88650はMCU/MPU端子によってチップの動作モードを次の2種類に設定できます。

MCUモード … MCU/MPU端子をHIGHに設定 内蔵ROMを使用する場合に設定します。内蔵メモリ以外の領域については外部メモリの拡張も行えます。メモリマップについては“3.5.2 バスモード”を参照してください。

MCUモードではイニシャルリセット時に内蔵メモリのみのシステムとして起動するようになっています。内蔵プログラムROMはプログラムメモリのコモンエリア(論理空間の0000H～7FFFH)部として常時固定となり、例外処理ベクタは内蔵プログラムROM内に配置されます。また、リセット例外処理によって開始されるアプリケーションの初期化ルーチンについても、内蔵プログラムROMに書き込んでおく必要があります。外部に拡張したメモリに対応させるバス等の設定はソフトウェアによって行えますので、内蔵プログラムROMに書き込む初期化ルーチンの中でこの処理を行います。このバスモードの設定後、外部メモリのアクセスが行えるようになります。

このモードでは内蔵メモリの領域をアクセスする際、外部メモリに対してチップイネーブル(CE)信号およびリード(RD)/ライト(WR)信号が出力されず、データバス(D0～D7)はハイインピーダンス(またはプルアップ状態)となります。したがって、外部メモリと内蔵メモリでアドレスが重複した場合、外部メモリのその領域は無効となります。

**MPUモード** ... MCU/MPU端子をLOWに設定 内蔵ROM領域を外部に解放します。内蔵ROMは使用できなくなり、この領域のアクセス時には外部メモリに対してチップイネーブル(CE)信号およびリード(RD)/ライト(WR)信号が出力され、データバス(D0～D7)がアクティブとなります。他の内蔵メモリの領域をアクセスする際には、これらの信号は外部に出力されません。

MPUモードでは外部のメモリによってシステムが起動します。

このモードで使用する場合、例外処理ベクタと初期化ルーチンを、必ずコモンエリア(000000H～007FFFFH)内に配置する必要があります。

MCU/MPU端子の内蔵プルアップ抵抗は、マスクオプションで使用するかしないかを選択することができます。

| 入力ポート   | プルアップ抵抗   |

|---------|-----------|

| MCU/MPU | 抵抗あり 抵抗なし |

- 注!

- MCU/MPU端子の設定は、RESET端子の立ち上がりエッジでラッチされますので、設定を変更する場合はRESET端子を再度LOWレベルとする必要があります。

- 内蔵メモリアクセス時にデータバスをハイインピーダンスにするかプルアップするかは、プルアップコントロールレジスタおよびマスクオプションによって選択することができます。詳細は"5.7 入出力兼用ポート(Pポート)"を参照してください。

### 3.5.2 バスモード

バスモードは外部に拡張したメモリの構成にバスの仕様を合わせるための設定で、以下の2種類がソフトウェアによって選択できます。

#### シングルチップモード

図3.5.2.1 シングルチップモードのメモリマップ

シングルチップモードは外部メモリの拡張を行わずにS1C88650をシングルチップマイクロコンピュータとして使用する場合に設定するモードです。

このモードでは内蔵ROMを使用するため、前項で示したMCUモードでのみ動作します。MPUモードではシングルチップモードを設定することはできません。

外部に対するバスラインが必要なくなるため、バス用に設定されている端子は汎用の出力ポートあるいは入出力兼用ポートとして使用できます。

#### 拡張モード

拡張モードはS1C88650の外部に1Mバイト×3以下のメモリを拡張して使用する場合に設定します。このモードはMCU/MPUモードにかかわらず設定できます。

MCUモードでは内蔵ROMが有効となり、100000Hから3FFFFFFHまでの領域に外部メモリ等を割り当てるることができます。

MPUモードでは内蔵ROM領域が解放されますので、000000Hから2FFFFFFHまでの領域に外部メモリ等を割り当てるすることができます。

ただし、00C000Hから00BFFFFHまでの領域は内蔵RAM等に割り当てられており、外部デバイスをアクセスすることはできません。

図3.5.2.2 拡張モードのメモリマップ

各モードの設定方法については"5.2 システムコントローラとバスの制御"で説明します。

### 3.5.3 CPUモード

CPUの動作については、プログラミング領域に応じて、以下の2種類がソフトウェアによって選択できます。

#### ミニマムモード

プログラム領域は、任意の1バンクエリアの64Kバイト以内に設定されます。ただし、CBレジスタは任意の1バンクを設定しておく必要があります。サブルーチンコール時にCBレジスタをスタックしないため、スタック領域が節約できます。プログラム容量が小～中規模、データ容量が大規模なシステムに適しています。

#### マキシマムモード

プログラム領域は、64Kバイトを越える領域で使用することができます。ただし、64Kバイトを越える領域をアクセスするためにはCBレジスタを設定しなくてはなりません。サブルーチンコール時にCBレジスタをスタックします。プログラム容量、データ容量ともに大規模なシステムに適しています。

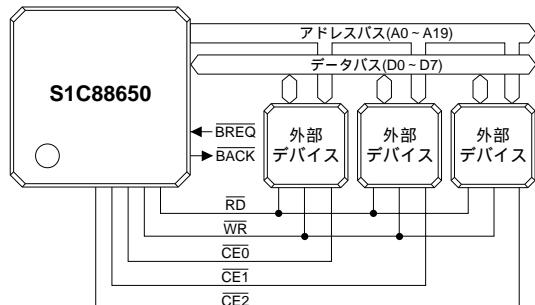

## 3.6 外部バス

S1C88650は最大1Mバイト×3のアドレスингが可能なバス端子を持ち、前項に示した各バスモードの範囲にしたがって、外部にメモリ等のデバイスを拡張することができます。

図3.6.1 外部バスライン

以下に外部バス端子の概要を説明します。制御方法については"5.2 システムコントローラとバスの制御"を参照してください。

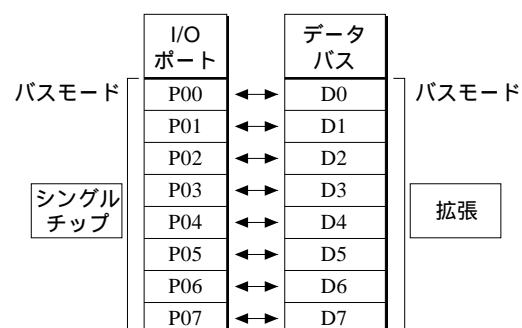

### 3.6.1 データバス

S1C88650は8ビットの外部データバス(D0～D7)を持っています。データバスD0～D7は、端子および入出力回路が入出力兼用ポートP00～P07と共に用されており、バスモードの設定によって機能が切り換わります。

シングルチップモードでは8ビットの端子がすべて入出力兼用ポートP00～P07として設定され、拡張モードではデータバス(D0～D7)に設定されます。データバスに設定された場合、各入出力兼用ポートのデータレジスタとI/Oコントロールレジスタは入出力回路から切り離され、リード/ライト可能な汎用データレジスタとして使用できます。

このデータバスにおいては、入力モード時にプルアップ抵抗をONするかしないかを、プルアップコントロールレジスタおよびマスクオプションによって選択することができます。詳細は"5.7 入出力兼用ポート(Pポート)"を参照してください。

図3.6.1.1 データバスと入出力兼用ポートの対応

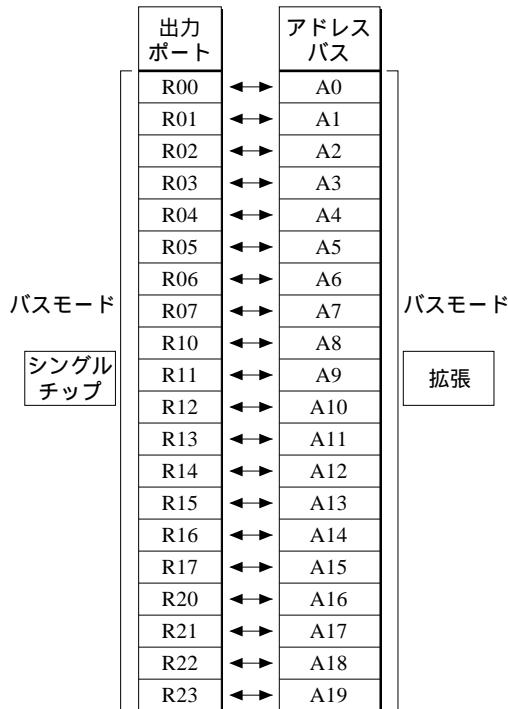

### 3.6.2 アドレスバス

S1C88650は20ビットの外部アドレスバス(A0 ~ A19)を持っています。アドレスバスA0 ~ A19は、端子および出力回路が出力ポートR00 ~ R07(A0 ~ A7)、R10 ~ R17(A8 ~ A15)、R20 ~ R23(A16 ~ A19)と共にされており、バスモードの設定によって機能が切り換わります。

シングルチップモードでは20ビットの端子がすべて出力ポートR00 ~ R07、R10 ~ R17、R20 ~ R23として設定されます。

拡張モードでは20ビットの端子がすべてアドレスバス(A0 ~ A19)として設定されます。

アドレスバスに設定された場合、各出力ポートのデータレジスタとハイインピーダンス制御レジスタは出力回路から切り離され、リード/ライト可能な汎用データレジスタとして使用できます。

### 3.6.3 リード( $\overline{RD}$ )/ライト( $\overline{WR}$ )信号

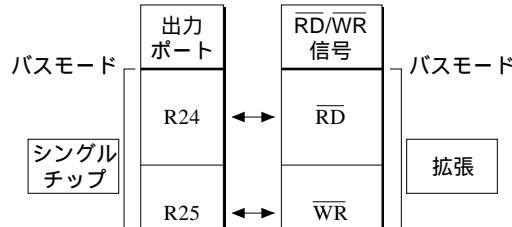

外部デバイスに対するリード( $\overline{RD}$ )/ライト( $\overline{WR}$ )信号の出力端子および出力回路はそれぞれ出力ポートR24、R25と共にされており、バスモードの設定によって機能の切り換えが行われます。

シングルチップモードではどちらの端子も出力ポート端子として設定され、拡張モードではリード( $\overline{RD}$ )/ライト( $\overline{WR}$ )信号出力端子に設定されます。

リード( $\overline{RD}$ )/ライト( $\overline{WR}$ )信号出力端子に設定された場合、出力ポートR24、R25のデータレジスタとハイインピーダンス制御レジスタは出力回路から切り離され、リード/ライト可能な汎用データレジスタとして使用できます。

信号の出力タイミングについては"3.6.5 ウェイト制御"を参照してください。

### 3.6.4 チップイネーブル( $\overline{CE}$ )信号

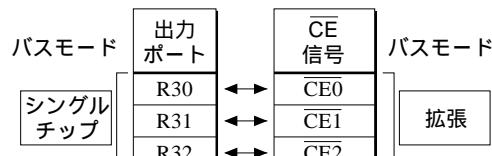

S1C88650はチップイネーブル( $\overline{CE}$ )信号を最大3本出力することのできるアドレスデコーダを内蔵しています。これにより、外部にアドレスデコーダを設けることなしに、チップイネーブル( $\overline{CE}$ )またはチップセレクト( $\overline{CS}$ )端子を持つ3個のデバイスを直接、接続することができます。

3本のチップイネーブル( $\overline{CE0}$  ~  $\overline{CE2}$ )信号の出力端子および出力回路は出力ポートR30 ~ R32と共にされており、シングルチップモード以外のモードの場合に、チップイネーブル( $\overline{CE}$ )と出力ポートのどちらに設定するかをソフトウェアで3ビット個々に選択することができます。

チップイネーブル( $\overline{CE}$ )出力に設定した場合、その出力ポートのデータレジスタとハイインピーダンス制御レジスタは出力回路から切り離され、リード/ライト可能な汎用データレジスタとして使用できます。

シングルチップモードの場合は出力ポートR30 ~ R32として固定されます。

図3.6.4.1 CE信号と出力ポートの対応

表3.6.4.1に、拡張モードにおいて割り当てられるチップイネーブル( $\overline{CE}$ )信号のアドレス範囲を示します。

表3.6.4.1  $\overline{CE0}$  ~  $\overline{CE2}$  のアドレス設定

| $\overline{CE}$ 信号 | アドレス範囲(拡張モード)   |                                  |

|--------------------|-----------------|----------------------------------|

|                    | MCUモード          | MPUモード                           |

| $\overline{CE0}$   | 300000H~3FFFFFH | 000000H~00D7FFH, 010000H~0FFFFFH |

| $\overline{CE1}$   | 100000H~1FFFFFH | 100000H~1FFFFFH                  |

| $\overline{CE2}$   | 200000H~2FFFFFH | 200000H~2FFFFFH                  |

内蔵メモリ領域のアクセス時には $\overline{CE}$ 信号が出力されません。その部分のアドレス範囲が変則的な設定になりますので注意してください。

メモリ空間への外部デバイスの配置は必ずしも下位アドレスから連続させる必要はなく、任意のチップイネーブル信号を用いてその領域に割り当てることができます。

注!  $\overline{CE}$ 信号はICがスタンバイモード(HALTモードまたはSLEEPモード)になるとインアクティブとなります。

信号の出力タイミングについては"3.6.5 ウェイト制御"を参照してください。

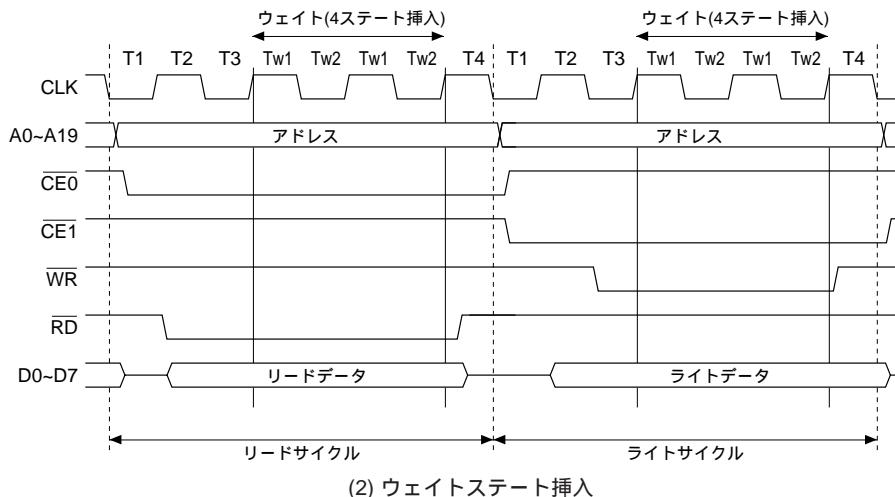

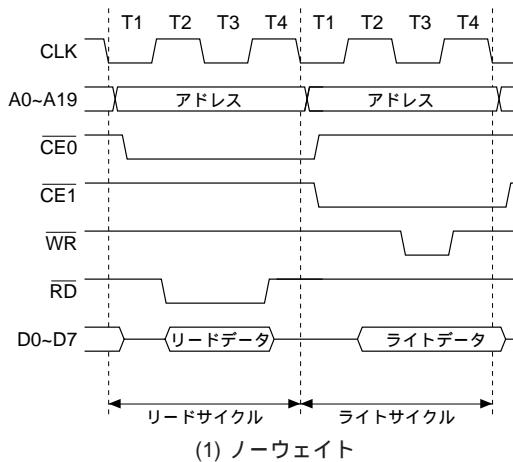

### 3.6.5 ウェイト制御

S1C88650は、高速動作時における外付け低速デバイスのアクセスを保証するため、アクセストイム伸長用のウェイト機能を内蔵しています。(ウェイト機能の詳細は"S1C88コアCPUマニュアル"を参照してください。)

挿入するウェイトステート数はソフトウェアによって表3.6.5.1に示す8種類の中から選択できます。

表3.6.5.1 選択可能なウェイトステート数

| 選択No.   | 1 | 2 | 3 | 4 | 5 | 6  | 7  | 8  |

|---------|---|---|---|---|---|----|----|----|

| 挿入ステート数 | 0 | 2 | 4 | 6 | 8 | 10 | 12 | 14 |

\* 1ステート長はクロックの1/2サイクルです。

ソフトウェアで設定したウェイトステートはバスサイクルのT3 ~ T4ステート間に挿入されます。ただし、内部レジスタと内蔵メモリのアクセス時、およびOSC1発振回路("5.4 発振回路"参照)での動作時には、ウェイトは挿入されません。

したがって、シングルチップモードではウェイトステートの設定は意味を持ちません。

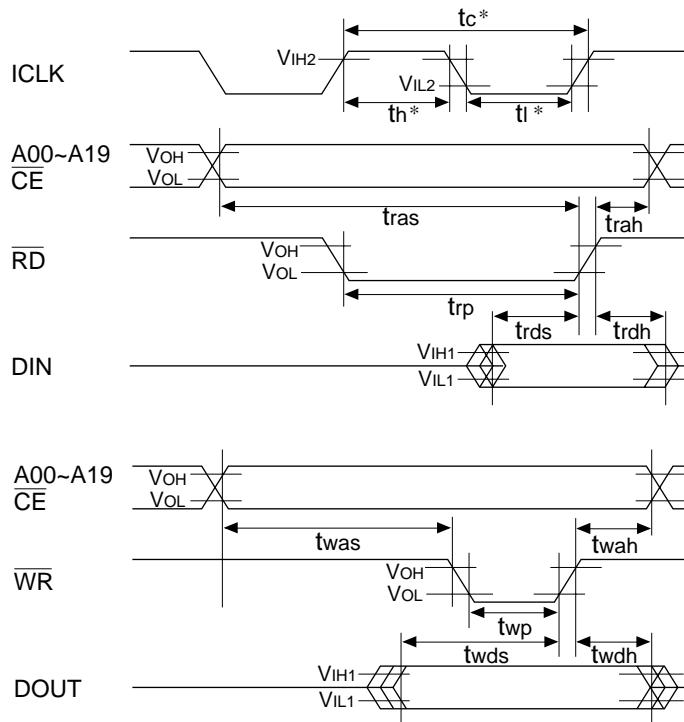

図3.6.5.1にメモリリード/ライトのタイミングチャートを示します。

図3.6.5.1 メモリリード/ライトサイクル

### 3.6.6 バス権解放状態

S1C88650は、外部デバイスからの要求によるバス権解放機能を持っており、外部デバイス間でのDMA(Direct Memory Access)転送が行えます。本機能は内蔵メモリへのアクセスはできません。

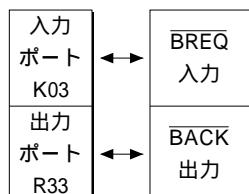

この機能に使用する端子は、バス権解放要求信号(BREQ)入力端子とバス権解放応答信号(BACK)出力端子の2本が用意されています。

BREQ入力端子はK03入力ポート端子と、BACK出力端子はR33出力ポート端子と共に用意されています。ソフトウェアによってBREQ/BACK端子に設定して使用します。シングルチップモードの場合、またはバス権解放の必要ないシステムにおいては、それらを入力/出力ポートに設定してください。

図3.6.6.1 BREQ/BACK端子

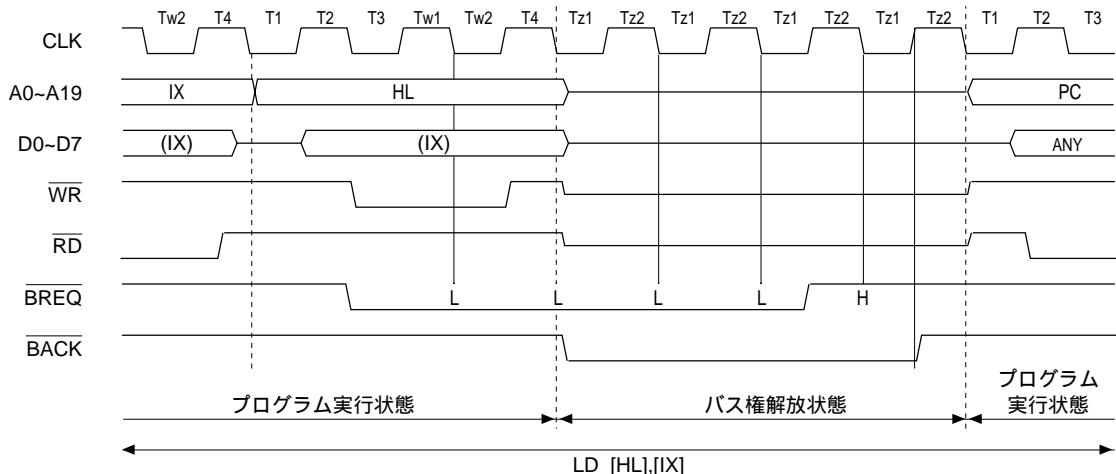

外部デバイスからのバス権解放要求(BREQ=LOW)を受け付けると、S1C88650はアドレスバス、データバス、RD/WR信号、およびCE信号の各ラインをハイインピーダンス状態に設定し、BACK端子にLOWレベルを出力してバス権を解放します。外部デバイスはBACK端子にLOWレベルが出力された時点から外部バスを使用することができ、DMA終了後にBREQ端子をHIGHレベルに戻すことでバス権を放棄します。

図3.6.6.2にバス権解放のシーケンスを示します。

バス権解放状態中、外部デバイスからは内蔵メモリをアクセスすることはできません。内蔵メモリの領域と重複した領域を持つ外部メモリがある場合、外部デバイスが出力するCE信号にしたがって外部メモリがアクセスされます。

注! バス権解放状態以外のときは外部デバイスがバスマスターとならないようシステム上で注意してください。

BREQ端子をLOWレベルにした後BACK端子がLOWレベルになるまで、BREQ端子のLOWレベルを保持してください。

BACK端子がLOWレベルになる以前にBREQ端子をHIGHレベルに戻すと、バス権解放状態への移行が不確定となります。

図3.6.6.2 バス権解放のシーケンス

# 4 イニシャルリセット

S1C88650は回路を初期化するためにイニシャルリセットを必要とします。

ここでは、イニシャルリセットの要因と内部レジスタ等の初期設定について説明します。

## 4.1 イニシャルリセット要因

S1C88650のイニシャルリセット要因としては以下の2種類があります。

- (1)  $\overline{\text{RESET}}$ 端子による外部イニシャルリセット

- (2) 入力ポート(K00～K03端子)の同時LOWレベル

入力による外部イニシャルリセット(マスクオプションで設定)

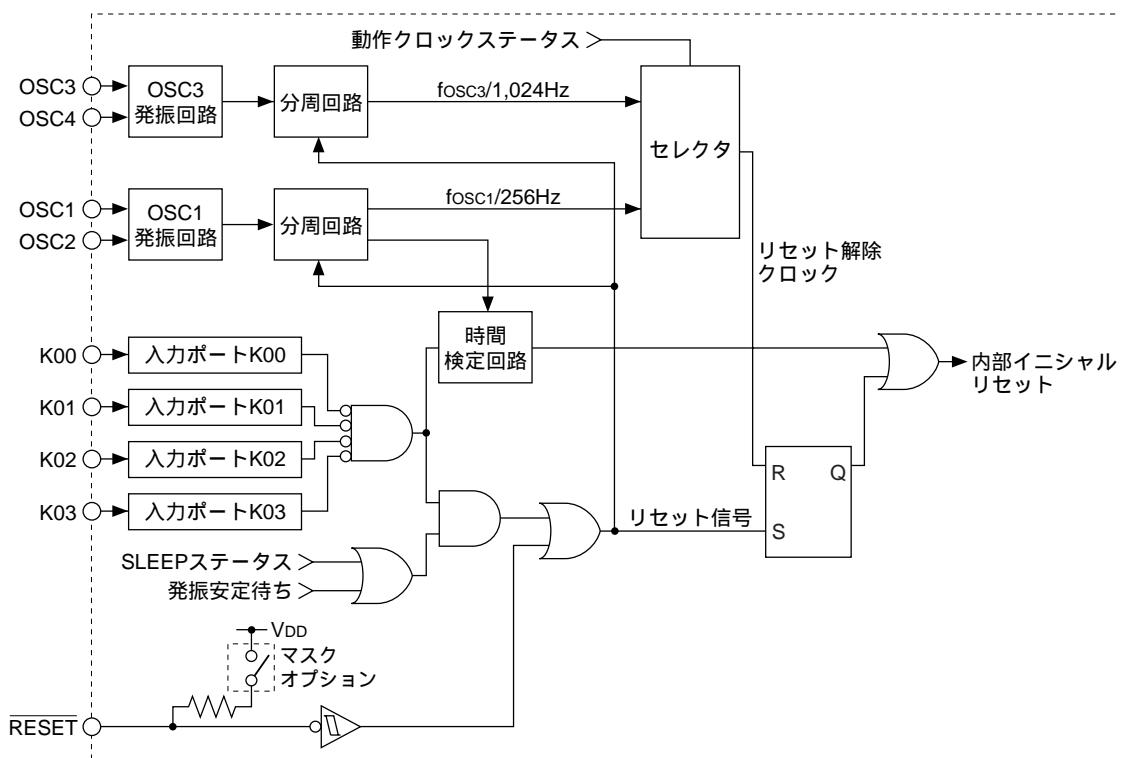

図4.1.1にイニシャルリセット回路の構成を示します。イニシャルリセット要因によってCPUおよび周辺回路が初期化され、要因が解除されるとCPUはリセット例外処理を開始します。("S1C88コアCPU マニュアル"参照)

これによって、バンク0先頭(000000H～000001H)のリセット例外処理ベクタが読み出され、その読み出されたアドレスから始まるプログラム(初期化ルーチン)の実行を開始します。

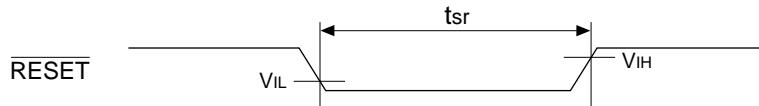

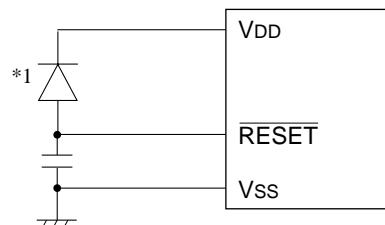

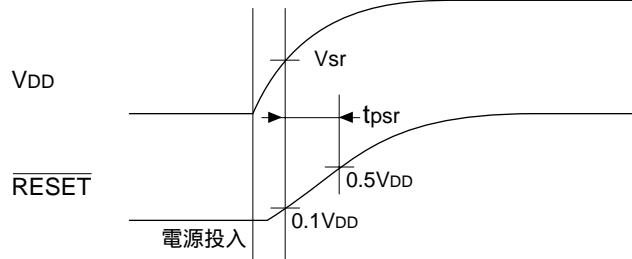

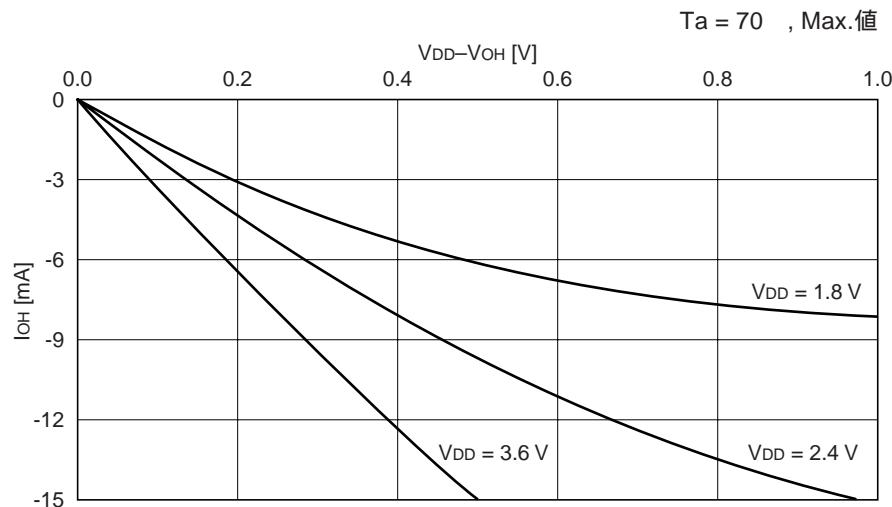

### 4.1.1 $\overline{\text{RESET}}$ 端子

外部から $\overline{\text{RESET}}$ 端子にLOWレベルを入力することでイニシャルリセットが行えます。

S1C88650を確実に初期化するため、電源電圧立ち上がり後規定の時間 $\overline{\text{RESET}}$ 端子をLOWレベルに保持してください。("8.6 AC特性"参照)

また、電源投入時の初回のイニシャルリセットは必ず $\overline{\text{RESET}}$ 端子を使用してください。 $\overline{\text{RESET}}$ 端子の内蔵プルアップ抵抗はマスクオプションで使用するかしないかを選択することができます。

|              |                                      |      |

|--------------|--------------------------------------|------|

| 入力ポートプルアップ抵抗 | $\overline{\text{RESET}}$ ..... 抵抗あり | 抵抗なし |

|--------------|--------------------------------------|------|

図4.1.1 イニシャルリセット回路の構成

### 4.1.2 入力ポート(K00～K03)の同時LOWレベル入力

マスクオプションで選択された入力ポート(K00～K03)に、外部から同時にLOWレベルを入力することでイニシャルリセットが行えます。本イニシャルリセット手段は時間検定回路を内蔵しているため、65536/fosc1秒(発振周波数fosc1=32.768kHzの場合2秒)以上、指定入力ポート端子をLOWレベルに保つ必要があります。

ただし、SLEEP(スタンバイ)状態時、および電源投入時の発振安定待ち期間中は時間検定回路がバイパスされるため、指定入力ポートへのLOWレベル同時入力直後にイニシャルリセットがかかります。マスクオプションで選択できる入力ポート(K00～K03)の組合せは次のとおりです。

#### キー同時押しリセット

使用しない

K00 & K01

K00 & K01 & K02

K00 & K01 & K02 & K03

たとえば、マスクオプションで"K00 & K01 & K02 & K03"を選択した場合、K00～K03の4ポートの入力が同時にLOWレベルになったときにイニシャルリセットがかかります。

この機能を使用する場合、通常動作時に指定入力ポートが同時にLOWレベルにならないように注意してください。

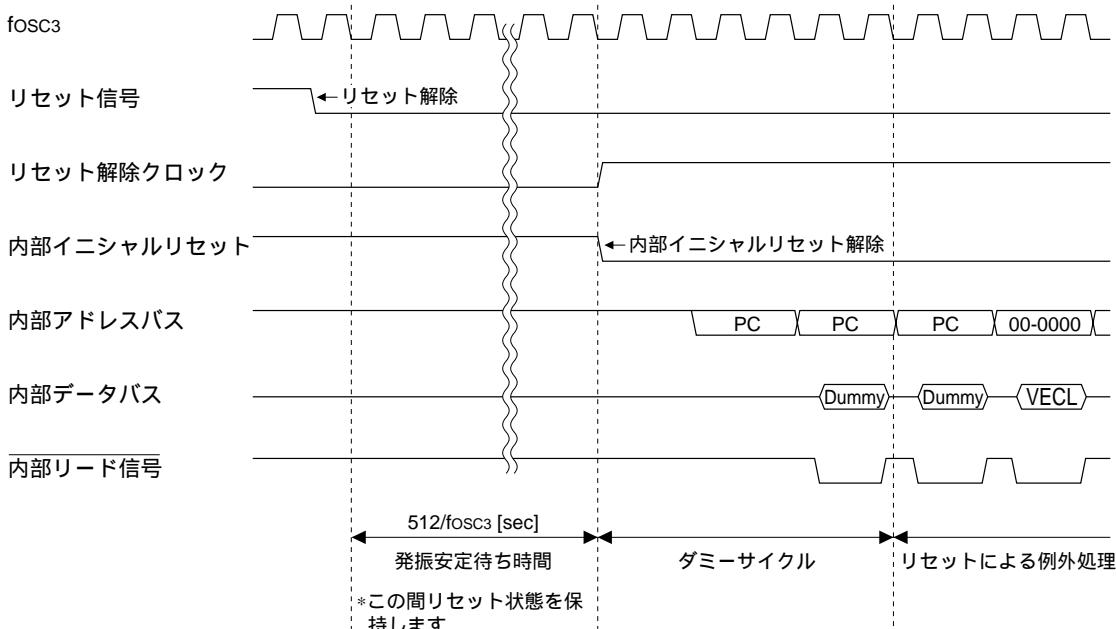

図4.1.3.1 イニシャルリセット解除後の動作シーケンス

### 4.1.3 イニシャルリセットシーケンス

電源投入時のRESET端子へのLOWレベル入力解除後、発振安定待ち時間(512/fosc3秒)が経過するまでCPUの起動は待たれます。

図4.1.3.1にイニシャルリセット解除後の動作シーケンスを示します。

CPUはリセット解除後fosc3に同期して起動します。

なお、入力ポート(K00～K03)への同時LOWレベル入力によるイニシャルリセット手段を使用する場合は、次の点に注意してください。

(1) SLEEP状態時、および電源投入時の発振安定待ち期間中は時間検定回路がバイパスされるため、LOWレベル同時入力直後にイニシャルリセットがかかります。この場合、LOWレベル同時入力解除後に発振安定時間を持ってCPUが起動します。

(2) (1)の状態以外はLOWレベル同時入力65536/fosc1秒後にイニシャルリセットがかかります。この場合は、S1C88650内部でリセット微分パルス(64/fosc1秒)が発生されるため、LOWレベル同時入力状態を解除しなくともCPUは起動します。

注! 発振安定待ち時間には、発振開始時間は含まれていません。そのため、電源投入時やSLEEP状態解除時の命令実行までの時間は、下図よりも長くなる場合があります。

## 4.2 イニシャルリセット時の初期設定

イニシャルリセットによりCPUの内部レジスタは

以下のように初期化されます。

表4.2.1 初期設定値

| レジスタ名称           | 記号 | ビット長 | 初期値 |

|------------------|----|------|-----|

| データレジスタA         | A  | 8    | 不定  |

| データレジスタB         | B  | 8    | 不定  |

| インデックス(データ)レジスタL | L  | 8    | 不定  |

| インデックス(データ)レジスタH | H  | 8    | 不定  |

| インデックスレジスタIX     | IX | 16   | 不定  |

| インデックスレジスタIY     | IY | 16   | 不定  |

| プログラムカウンタ        | PC | 16   | 不定* |

| スタックポインタ         | SP | 16   | 不定  |

| ベースレジスタ          | BR | 8    | 不定  |

| ゼロフラグ            | Z  | 1    | 0   |

| キャリーフラグ          | C  | 1    | 0   |

| オーバーフロー/フラグ      | V  | 1    | 0   |

| ネガティブフラグ         | N  | 1    | 0   |

| デシマルフラグ          | D  | 1    | 0   |

| アンパックフラグ         | U  | 1    | 0   |

| インターラプトフラグ0      | I0 | 1    | 1   |

| インターラプトフラグ1      | I1 | 1    | 1   |

| ニューコードバンクレジスタ    | NB | 8    | 01H |

| コードバンクレジスタ       | CB | 8    | 不定* |

| エクスパンドページレジスタ    | EP | 8    | 00H |

| IX用エクスパンドページレジスタ | XP | 8    | 00H |

| IY用エクスパンドページレジスタ | YP | 8    | 00H |

\* リセット例外処理によって、0バンクのメモリの先頭(000000H ~ 000001H)に格納されている値がPCにロードされます。また、このとき同時にNBの初期値01HがCBにロードされます。

イニシャルリセット時に初期化されない(不定)レジスタはソフトウェアで初期化してください。

内蔵RAMおよび表示メモリについてもイニシャルリセット時に初期化されませんので、同様にソフトウェアで初期化してください。

内蔵の周辺回路については、それぞれ所定の初期化が行われます。必要に応じてソフトウェアで初期化してください。

イニシャルリセット時の初期値については、次章のI/Oメモリマップまたは各周辺回路の説明を参照してください。

# 5 周辺回路と動作

S1C88650の周辺回路はメモリマップI/O方式でCPUとインターフェースされています。このため、他のメモリアクセスと同様にI/Oメモリを操作して周辺回路を制御することができます。以下、各周辺回路別にその動作と制御方法を説明します。

## 5.1 I/Oメモリマップ

表5.1.1(a) I/Oメモリマップ(00FF00H ~ 00FF03H)

| アドレス            | ビット | 名称     | 機能                          | 1            | 0            | SR             | R/W | 注釈          |

|-----------------|-----|--------|-----------------------------|--------------|--------------|----------------|-----|-------------|

| 00FF00<br>(MCU) | D7  | BUSMOD | バスモード                       | 拡張モード        | シングルチップ      | 0              | R/W | 予約レジスタ      |

|                 | D6  | CPUMOD | CPUモード                      | マキシマム        | ミニマム         | 0              | R/W |             |

|                 | D5  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D4  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D3  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D2  | CE2    | CE2 (R32)<br>CE信号出力イネーブル    | CE2有効        | CE2無効        | 0              | R/W | シングルチップ     |

|                 | D1  | CE1    | CE1 (R31)<br>有効: CE信号出力     | CE1有効        | CE1無効        | 0              | R/W | モードの場合、     |

| 00FF00<br>(MPU) | D0  | CE0    | CE0 (R30)<br>無効: DC出力(R3x)  | CE0有効        | CE0無効        | 0              | R/W | DC出力に固定     |

|                 | D7  | BUSMOD | バスモード                       | 拡張モード        | -            | 1              | R   | 拡張モードに固定    |

|                 | D6  | CPUMOD | CPUモード                      | マキシマム        | ミニマム         | 0              | R/W |             |

|                 | D5  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W | 予約レジスタ      |

|                 | D4  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D3  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D2  | CE2    | CE2 (R32)<br>CE信号出力イネーブル    | CE2有効        | CE2無効        | 0              | R/W |             |

| 00FF01          | D1  | CE1    | CE1 (R31)<br>有効: CE信号出力     | CE1有効        | CE1無効        | 0              | R/W |             |

|                 | D0  | CE0    | CE0 (R30)<br>無効: DC出力(R3x)  | CE0有効        | CE0無効        | 1              | R/W |             |

|                 | D7  | SPP7   | スタックポイントアドレス (MSB)          | 1            | 0            | 0              | R/W |             |

|                 | D6  | SPP6   |                             | 1            | 0            | 0              | R/W |             |

|                 | D5  | SPP5   | < SPページ割り付け可能アドレス >         | 1            | 0            | 0              | R/W |             |

|                 | D4  | SPP4   | ・シングルチップモード: 0ページのみ         | 1            | 0            | 0              | R/W |             |

|                 | D3  | SPP3   | ・拡張モード: 0 ~ 27Hページ          | 1            | 0            | 0              | R/W |             |

|                 | D2  | SPP2   |                             | 1            | 0            | 0              | R/W |             |

| 00FF02          | D1  | SPP1   |                             | 1            | 0            | 0              | R/W |             |

|                 | D0  | SPP0   | (LSB)                       | 1            | 0            | 0              | R/W |             |

|                 | D7  | EBR    | バス解放イネーブル<br>(K03, R33端子仕様) | K03<br>R33   | BREQ<br>BACK | 入力ポート<br>出力ポート | 0   | R/W         |

|                 | D6  | WT2    | ウェイトステート制御                  |              |              |                | 0   | R/W         |

|                 |     |        | WT2 WT1 WT0 ステート数           | 1 1 1 14     |              |                |     |             |

|                 | D5  | WT1    |                             | 1 1 0 12     |              |                | 0   | R/W         |

|                 |     |        |                             | 1 0 1 10     |              |                |     |             |

|                 | D4  | WT0    |                             | 1 0 0 8      |              |                | 0   | R/W         |

| 00FF03          |     |        |                             | 0 1 1 6      |              |                |     |             |

|                 |     |        |                             | 0 0 1 2      |              |                |     |             |

|                 |     |        |                             | 0 0 0 ノーウェイト |              |                |     |             |

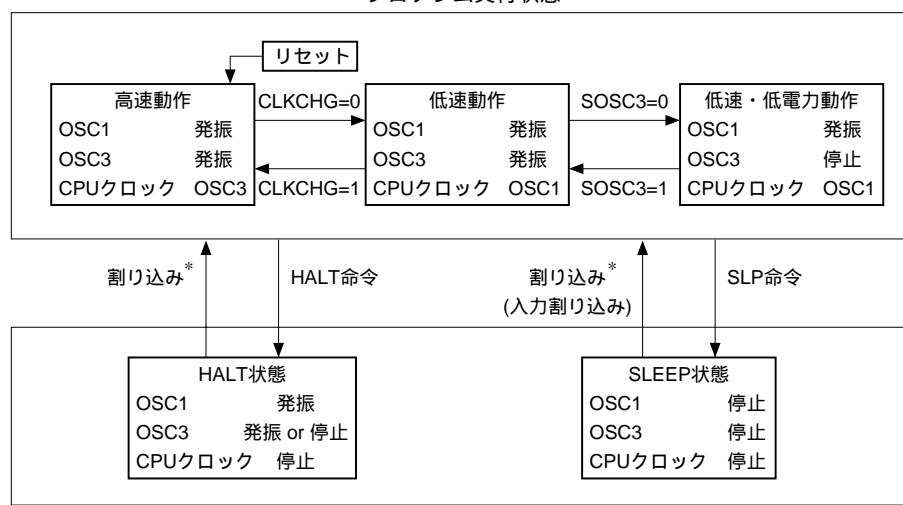

|                 | D3  | CLKCHG | CPU動作クロック切り換え               | OSC3         | OSC1         | 1              | R/W |             |

|                 | D2  | SOSC3  | OSC3発振On/Off制御              | On           | Off          | 1              | R/W |             |

|                 | D1  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W | 予約レジスタ      |

|                 | D0  | -      | 汎用レジスタ                      | 1            | 0            | 0              | R/W |             |

|                 | D7  | -      | -                           | -            | -            | -              |     | 読み出し時は常時"0" |

|                 | D6  | -      | -                           | -            | -            | -              |     |             |

|                 | D5  | -      | -                           | -            | -            | -              |     |             |

|                 | D4  | -      | -                           | -            | -            | -              |     |             |

|                 | D3  | -      | -                           | -            | -            | -              |     |             |

|                 | D2  | -      | -                           | -            | -            | -              |     |             |

|                 | D1  | VDSEL  | 液晶系定電圧回路用電源選択               | VD2          | VDD          | 0              | R/W |             |

|                 | D0  | DBON   | 電源電圧昇圧回路On/Off制御            | On           | Off          | 0              | R/W |             |

注! アドレス"00FF00H"および"00FF01H"に任意の値をそれぞれ書き込むまで、NMIを含めたすべての割り込みはマスクされます。

表5.1.1(b) I/Oメモリマップ(00FF10H ~ 00FF14H)

| アドレス   | ビット                                    | 名称     | 機能                                                                                                                             | 1     | 0         | SR | R/W | 注釈                      |

|--------|----------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----|-----|-------------------------|

| 00FF10 | D7                                     | HLMOD  | 重負荷保護モード                                                                                                                       | On    | Off       | 0  | R/W |                         |

|        | D6                                     | SEGREV | SEG出力対応反転                                                                                                                      | 反転    | 通常        | 0  | R/W |                         |

|        | D5                                     | —      | 汎用レジスタ                                                                                                                         | 1     | 0         | 0  | R/W | 予約レジスタ                  |

|        | D4                                     | —      | 汎用レジスタ                                                                                                                         | 1     | 0         | 0  | R/W |                         |

|        | D3                                     | —      | 汎用レジスタ                                                                                                                         | 1     | 0         | 0  | R/W |                         |

|        | D2                                     | DTFNT  | LCDドットフォント選択                                                                                                                   | 12×12 | 16×16/5×8 | 0  | R/W |                         |

|        | D1                                     | LDUTY1 | LCD駆動デューティ選択                                                                                                                   |       |           | 1  | R/W |                         |

|        | <u>LDUTY1 LDUTY0 デューティ</u>             |        |                                                                                                                                |       |           |    |     |                         |

|        | D0                                     | LDUTY0 | 1 1 禁止<br>1 0 1/16<br>0 1 1/32<br>0 0 1/8                                                                                      |       |           | 0  | R/W |                         |

|        | D7                                     | FRMCS  | LCDフレーム周波数源振クロック選択                                                                                                             | Pタイマ  | fosc1     | 0  | R/W |                         |

| 00FF11 | D6                                     | DSPAR  | LCD表示メモリ領域選択                                                                                                                   | 表示領域1 | 表示領域0     | 0  | R/W |                         |

|        | D5                                     | LCDC1  | LCD表示制御                                                                                                                        |       |           | 0  | R/W | SLP命令実行時に<br>(0,0)にリセット |

|        | <u>LCDC1 LCDC0 LCD表示</u>               |        |                                                                                                                                |       |           |    |     |                         |

|        | D4                                     | LCDC0  | 1 1 全点灯<br>1 0 全消灯<br>0 1 通常表示<br>0 0 駆動Off                                                                                    |       |           | 0  | R/W |                         |

|        | D3                                     | LC3    | LCDコントラスト調整                                                                                                                    |       |           | 0  | R/W |                         |

|        | D2                                     | LC2    | <u>LC3 LC2 LC1 LC0 コントラスト</u>                                                                                                  |       |           | 0  | R/W |                         |

|        | D1                                     | LC1    | 1 1 1 0 : :                                                                                                                    |       |           | 0  | R/W |                         |

|        | D0                                     | LC0    | 0 0 0 0 淡                                                                                                                      |       |           | 0  | R/W |                         |

|        | D7                                     | —      | —                                                                                                                              | —     | —         | —  |     | 読み出し時は<br>常時"0"         |

|        | D6                                     | —      | —                                                                                                                              | —     | —         | —  |     |                         |

| 00FF12 | D5                                     | SVDDT  | SVD検出データ                                                                                                                       | Low   | Normal    | 0  | R   |                         |

|        | D4                                     | SVDON  | SVD回路On/Off                                                                                                                    | On    | Off       | 0  | R/W |                         |

|        | D3                                     | SVDS3  | SVD比較電圧設定                                                                                                                      |       |           | 0  | R/W |                         |

|        | <u>SVDS3 SVDS2 SVDS1 SVDS0 電圧(V)</u>   |        |                                                                                                                                |       |           |    |     |                         |

|        | D2                                     | SVDS2  | 1 1 1 1 2.7                                                                                                                    |       |           | 0  | R/W |                         |

|        | D1                                     | SVDS1  | 1 1 0 1 2.5                                                                                                                    |       |           | 0  | R/W |                         |

|        | D0                                     | SVDS0  | : : : : :                                                                                                                      |       |           | 0  | R/W |                         |

|        |                                        |        | 0 0 1 1 1.8                                                                                                                    |       |           |    |     |                         |

| 00FF14 | D7                                     | PRPRT1 | プログラマブルタイマ1クロック制御                                                                                                              | On    | Off       | 0  | R/W |                         |

|        | D6                                     | PST12  | プログラマブルタイマ1分周比                                                                                                                 |       |           | 0  | R/W |                         |

|        | <u>PST12 PST11 PST10 (OSC3) (OSC1)</u> |        |                                                                                                                                |       |           |    |     |                         |

|        | D5                                     | PST11  | 1 1 1 fosc3 / 4096 fosc1 / 128<br>1 1 0 fosc3 / 1024 fosc1 / 64<br>1 0 1 fosc3 / 256 fosc1 / 32<br>1 0 0 fosc3 / 64 fosc1 / 16 |       |           | 0  | R/W |                         |

|        | D4                                     | PST10  | 0 1 1 fosc3 / 32 fosc1 / 8<br>0 1 0 fosc3 / 8 fosc1 / 4<br>0 0 1 fosc3 / 2 fosc1 / 2<br>0 0 0 fosc3 / 1 fosc1 / 1              |       |           | 0  | R/W |                         |

|        | D3                                     | PRPRT0 | プログラマブルタイマ0クロック制御                                                                                                              | On    | Off       | 0  | R/W |                         |

|        | D2                                     | PST02  | プログラマブルタイマ0分周比                                                                                                                 |       |           | 0  | R/W |                         |

|        | <u>PST02 PST01 PST00 (OSC3) (OSC1)</u> |        |                                                                                                                                |       |           |    |     |                         |

|        | D1                                     | PST01  | 1 1 1 fosc3 / 4096 fosc1 / 128<br>1 1 0 fosc3 / 1024 fosc1 / 64<br>1 0 1 fosc3 / 256 fosc1 / 32<br>1 0 0 fosc3 / 64 fosc1 / 16 |       |           | 0  | R/W |                         |

|        | D0                                     | PST00  | 0 1 1 fosc3 / 32 fosc1 / 8<br>0 1 0 fosc3 / 8 fosc1 / 4<br>0 0 1 fosc3 / 2 fosc1 / 2<br>0 0 0 fosc3 / 1 fosc1 / 1              |       |           | 0  | R/W |                         |

表5.1.1(c) I/Oメモリマップ(00FF15H ~ 00FF18H)

| アドレス   | ビット | 名称     | 機能                                                | 1  | 0   | SR | R/W | 注釈          |

|--------|-----|--------|---------------------------------------------------|----|-----|----|-----|-------------|

| 00FF15 | D7  | PRPRT3 | プログラマブルタイマ3クロック制御                                 | On | Off | 0  | R/W | 読み出し時は常時"0" |

|        | D6  | PST32  | プログラマブルタイマ3分周比<br>PST32 PST31 PST30 (OSC3) (OSC1) |    |     | 0  | R/W |             |

|        |     |        | 1 1 1 fosc3 / 4096 fosc1 / 128                    |    |     |    |     |             |

|        |     |        | 1 1 0 fosc3 / 1024 fosc1 / 64                     |    |     | 0  | R/W |             |

|        |     |        | 1 0 1 fosc3 / 256 fosc1 / 32                      |    |     |    |     |             |

|        |     |        | 1 0 0 fosc3 / 64 fosc1 / 16                       |    |     |    |     |             |

|        |     |        | 0 1 1 fosc3 / 32 fosc1 / 8                        |    |     |    |     |             |

|        |     |        | 0 1 0 fosc3 / 8 fosc1 / 4                         |    |     | 0  | R/W |             |

|        |     |        | 0 0 1 fosc3 / 2 fosc1 / 2                         |    |     |    |     |             |

|        |     |        | 0 0 0 fosc3 / 1 fosc1 / 1                         |    |     |    |     |             |

| 00FF17 | D3  | PRPRT2 | プログラマブルタイマ2クロック制御                                 | On | Off | 0  | R/W | 読み出し時は常時"0" |

|        | D2  | PST22  | プログラマブルタイマ2分周比<br>PST22 PST21 PST20 (OSC3) (OSC1) |    |     | 0  | R/W |             |

|        |     |        | 1 1 1 fosc3 / 4096 fosc1 / 128                    |    |     |    |     |             |

|        |     |        | 1 1 0 fosc3 / 1024 fosc1 / 64                     |    |     | 0  | R/W |             |

|        |     |        | 1 0 1 fosc3 / 256 fosc1 / 32                      |    |     |    |     |             |

|        |     |        | 1 0 0 fosc3 / 64 fosc1 / 16                       |    |     |    |     |             |

|        |     |        | 0 1 1 fosc3 / 32 fosc1 / 8                        |    |     |    |     |             |

|        |     |        | 0 1 0 fosc3 / 8 fosc1 / 4                         |    |     | 0  | R/W |             |

|        |     |        | 0 0 1 fosc3 / 2 fosc1 / 2                         |    |     |    |     |             |

|        |     |        | 0 0 0 fosc3 / 1 fosc1 / 1                         |    |     |    |     |             |

| 00FF18 | D7  | PRPRT5 | プログラマブルタイマ5クロック制御                                 | On | Off | 0  | R/W | 読み出し時は常時"0" |

|        | D6  | PST52  | プログラマブルタイマ5分周比<br>PST52 PST51 PST50 (OSC3) (OSC1) |    |     | 0  | R/W |             |

|        |     |        | 1 1 1 fosc3 / 4096 fosc1 / 128                    |    |     |    |     |             |

|        |     |        | 1 1 0 fosc3 / 1024 fosc1 / 64                     |    |     | 0  | R/W |             |

|        |     |        | 1 0 1 fosc3 / 256 fosc1 / 32                      |    |     |    |     |             |

|        |     |        | 1 0 0 fosc3 / 64 fosc1 / 16                       |    |     |    |     |             |

|        |     |        | 0 1 1 fosc3 / 32 fosc1 / 8                        |    |     | 0  | R/W |             |

|        |     |        | 0 1 0 fosc3 / 8 fosc1 / 4                         |    |     |    |     |             |

|        |     |        | 0 0 1 fosc3 / 2 fosc1 / 2                         |    |     |    |     |             |

|        |     |        | 0 0 0 fosc3 / 1 fosc1 / 1                         |    |     |    |     |             |

| 00FF19 | D3  | PRPRT4 | プログラマブルタイマ4クロック制御                                 | On | Off | 0  | R/W | 読み出し時は常時"0" |

|        | D2  | PST42  | プログラマブルタイマ4分周比<br>PST42 PST41 PST40 (OSC3) (OSC1) |    |     | 0  | R/W |             |

|        |     |        | 1 1 1 fosc3 / 4096 fosc1 / 128                    |    |     |    |     |             |

|        |     |        | 1 1 0 fosc3 / 1024 fosc1 / 64                     |    |     | 0  | R/W |             |

|        |     |        | 1 0 1 fosc3 / 256 fosc1 / 32                      |    |     |    |     |             |

|        |     |        | 1 0 0 fosc3 / 64 fosc1 / 16                       |    |     |    |     |             |

|        |     |        | 0 1 1 fosc3 / 32 fosc1 / 8                        |    |     |    |     |             |

|        |     |        | 0 1 0 fosc3 / 8 fosc1 / 4                         |    |     | 0  | R/W |             |

|        |     |        | 0 0 1 fosc3 / 2 fosc1 / 2                         |    |     |    |     |             |

|        |     |        | 0 0 0 fosc3 / 1 fosc1 / 1                         |    |     |    |     |             |

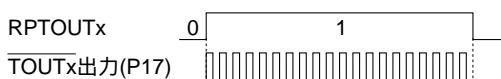

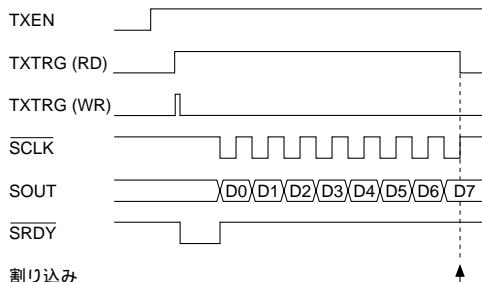

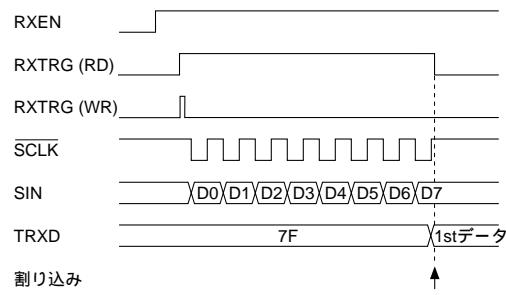

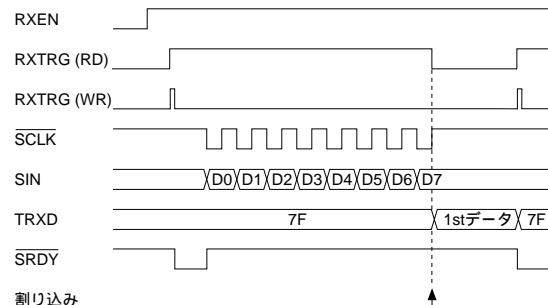

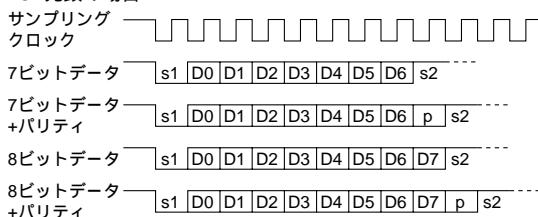

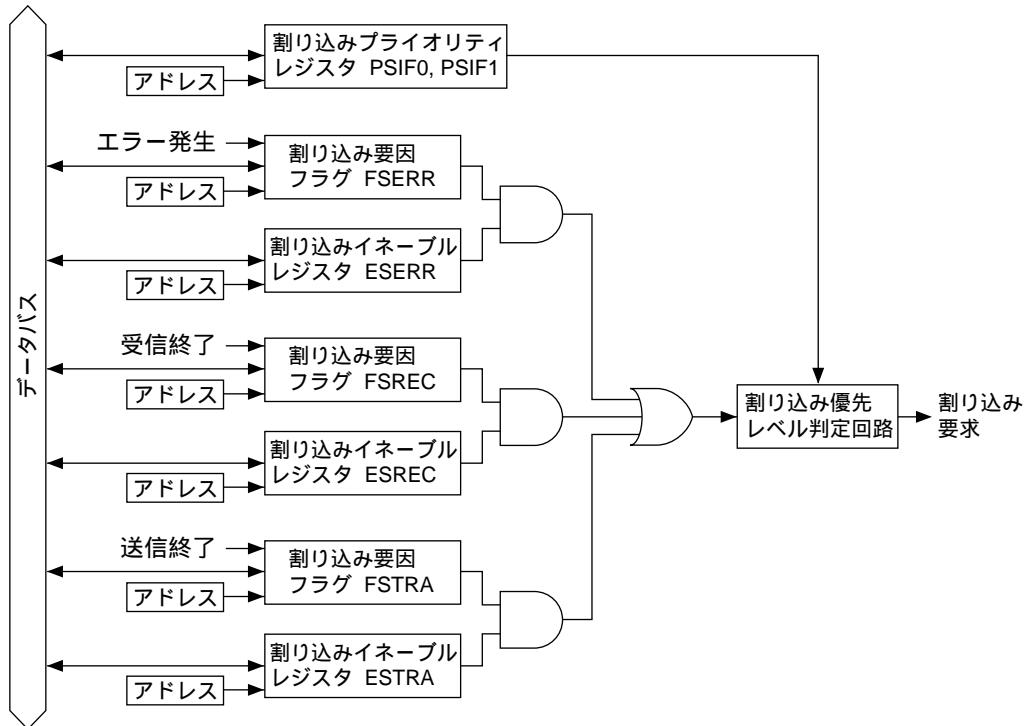

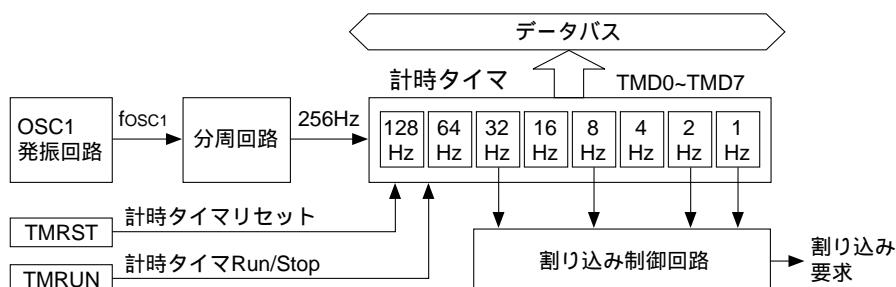

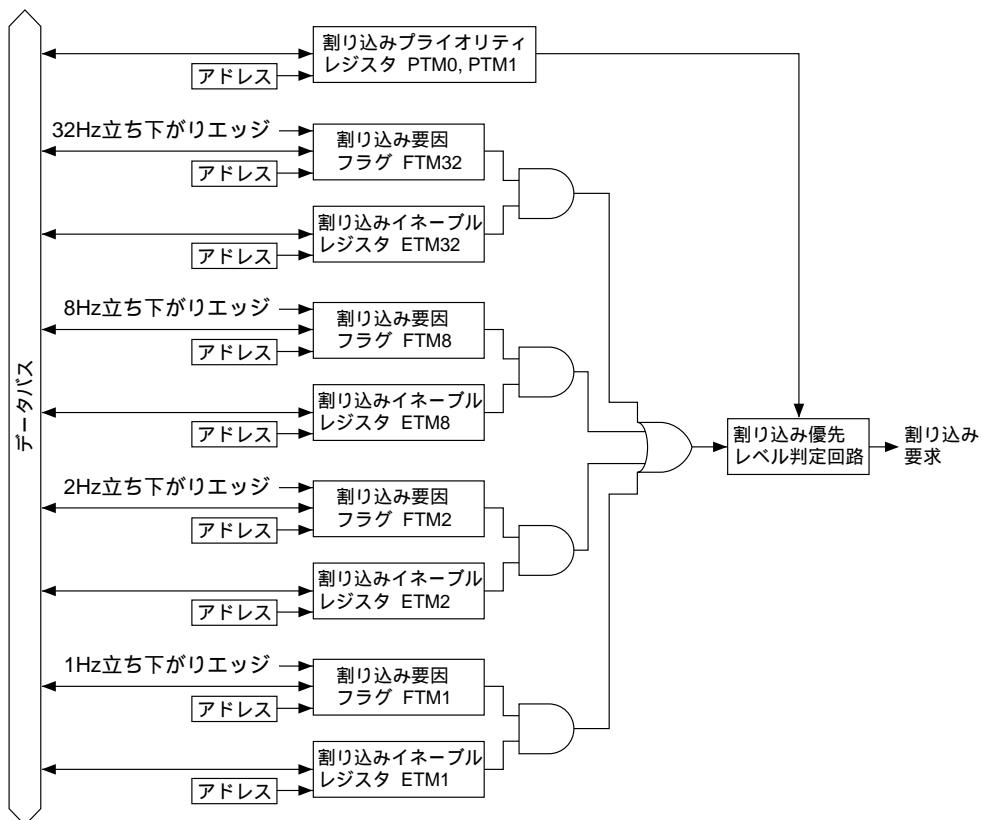

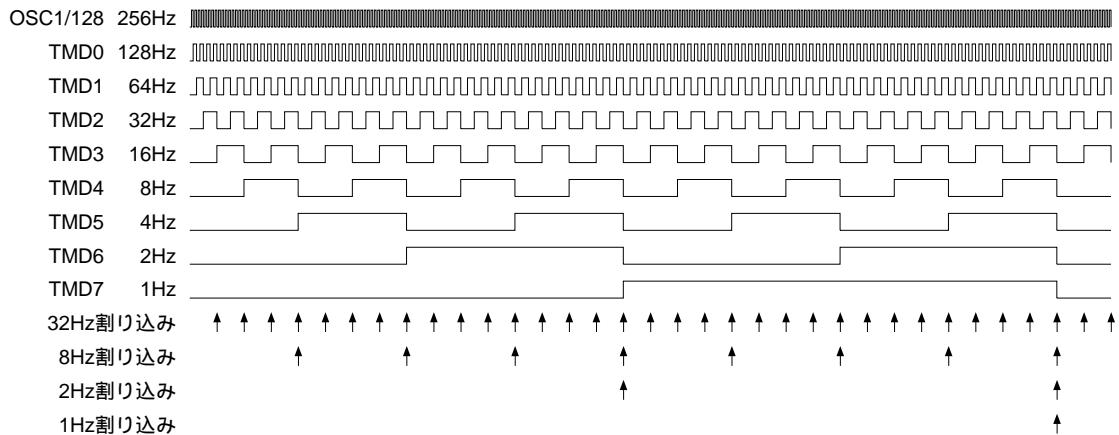

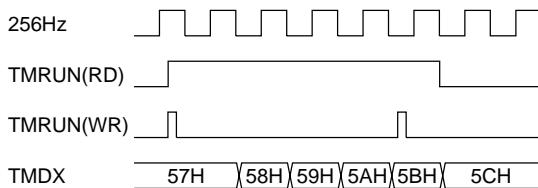

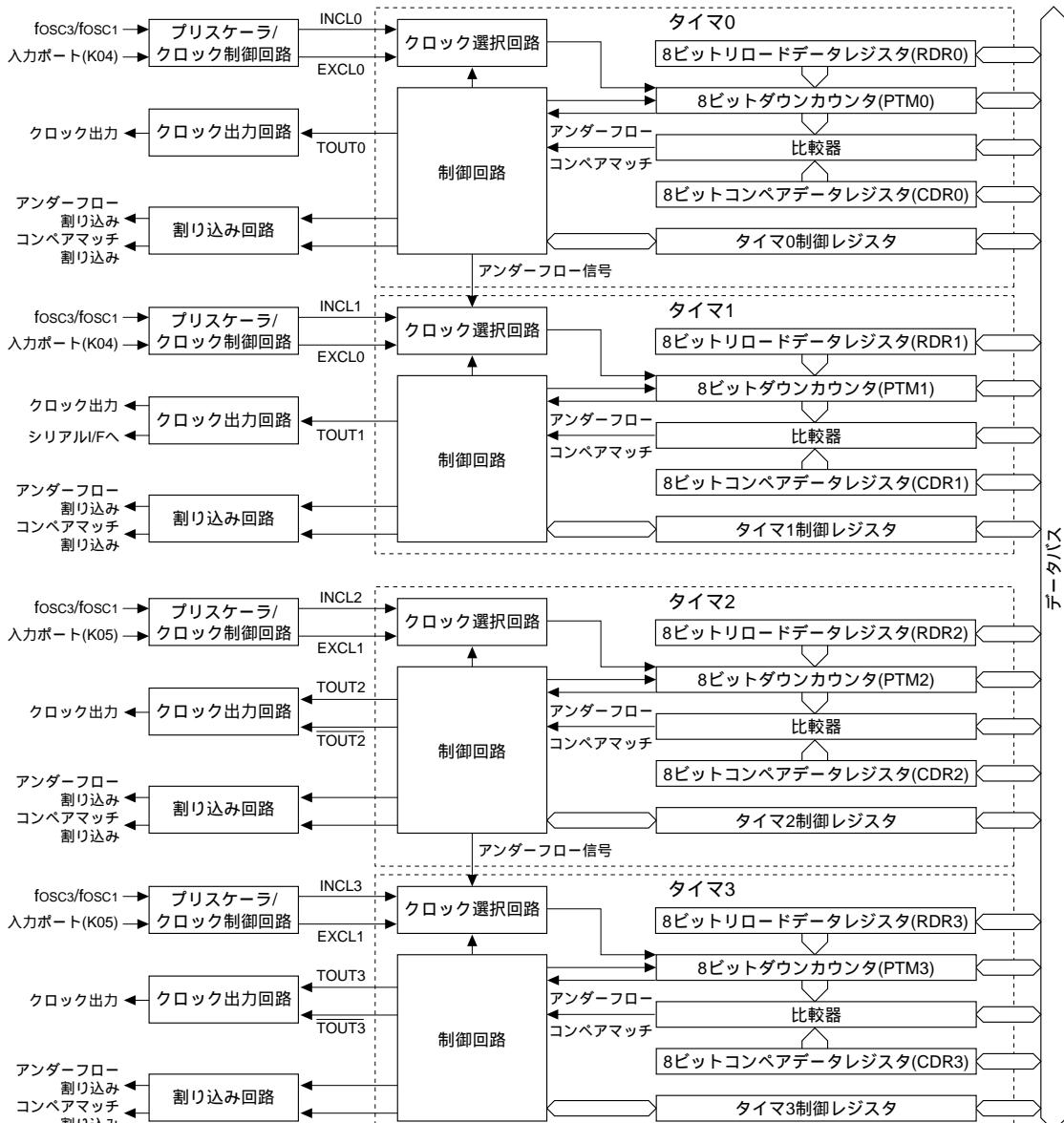

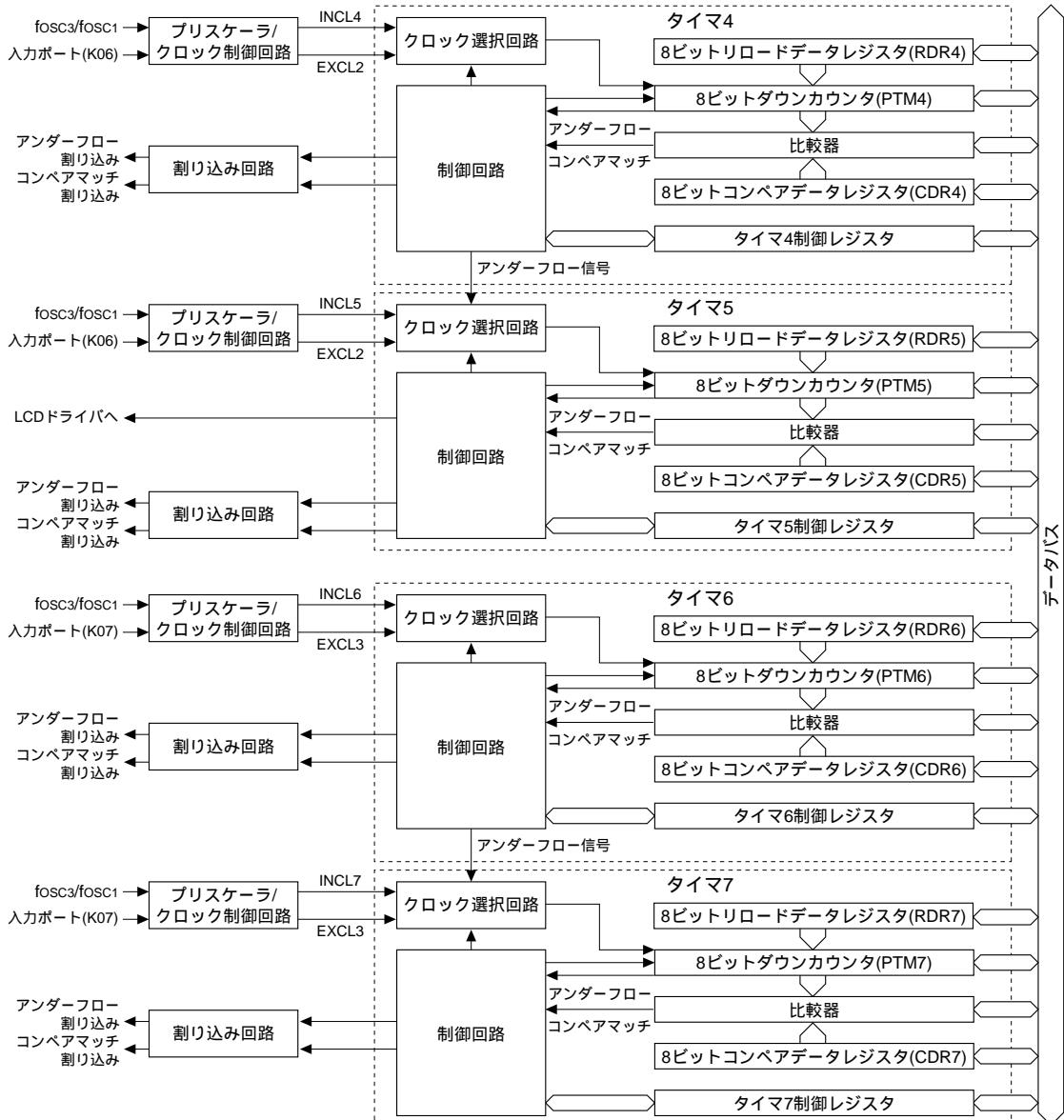

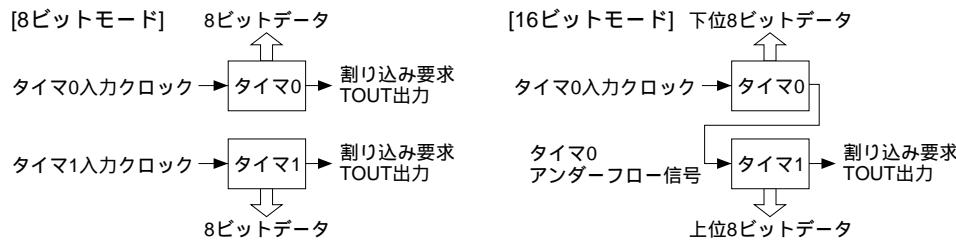

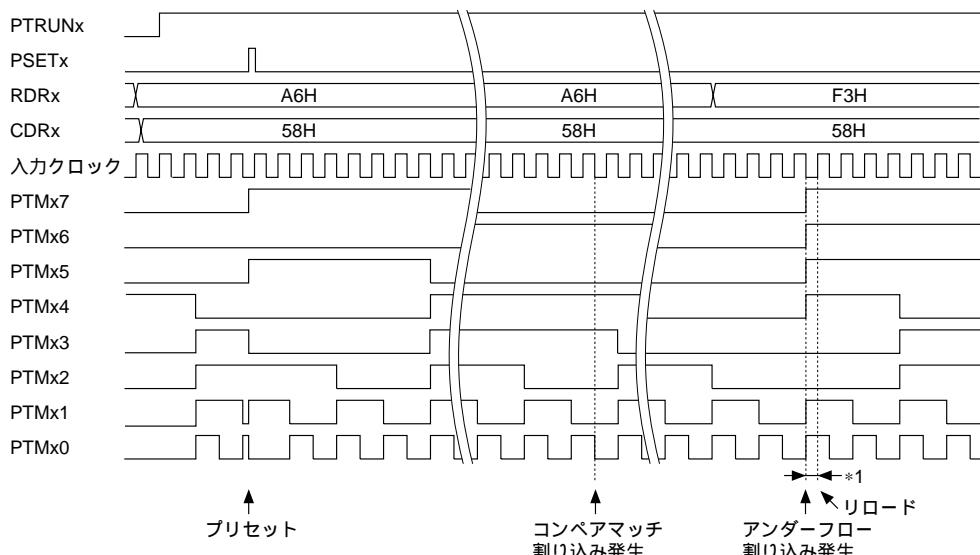

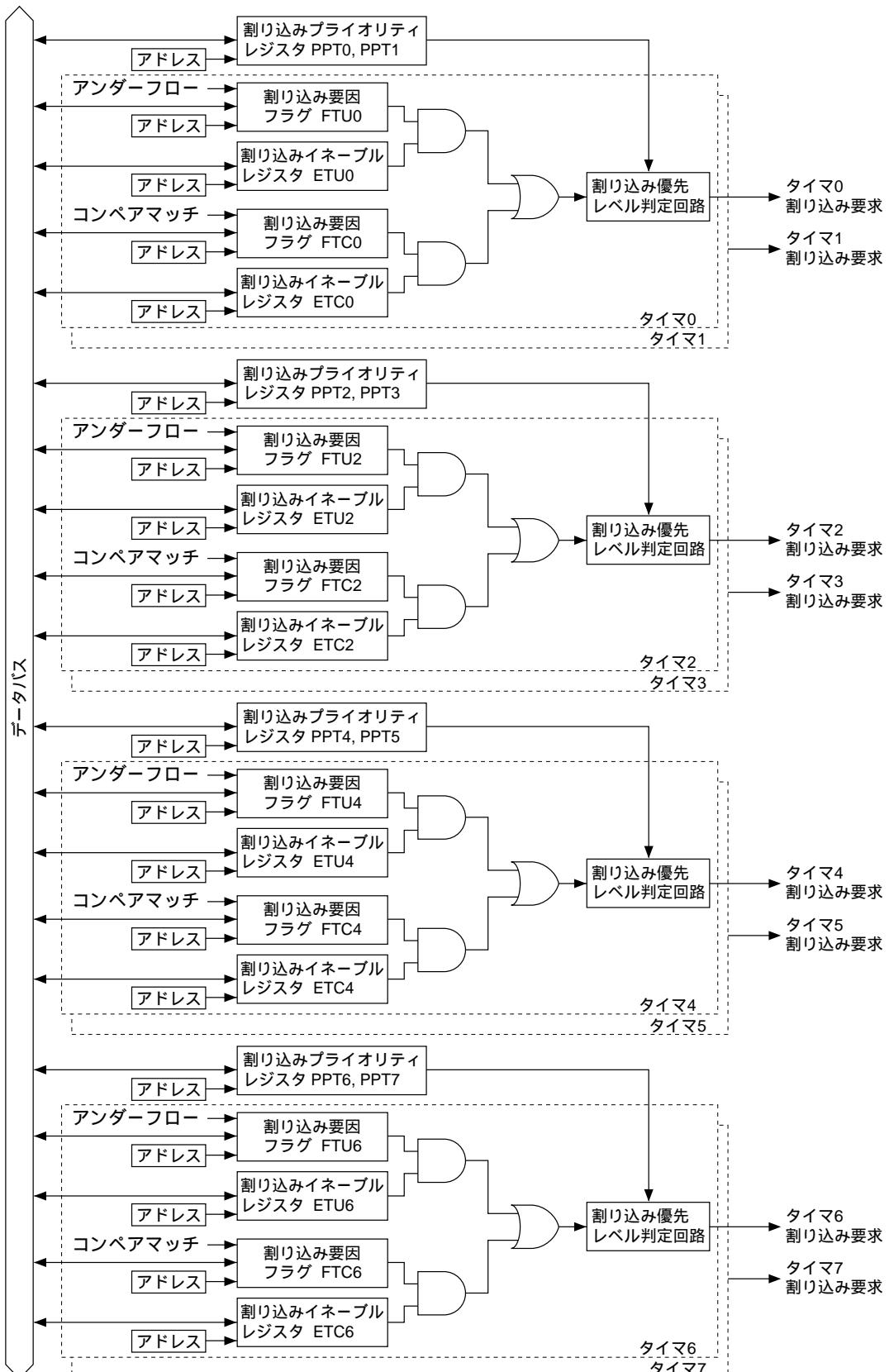

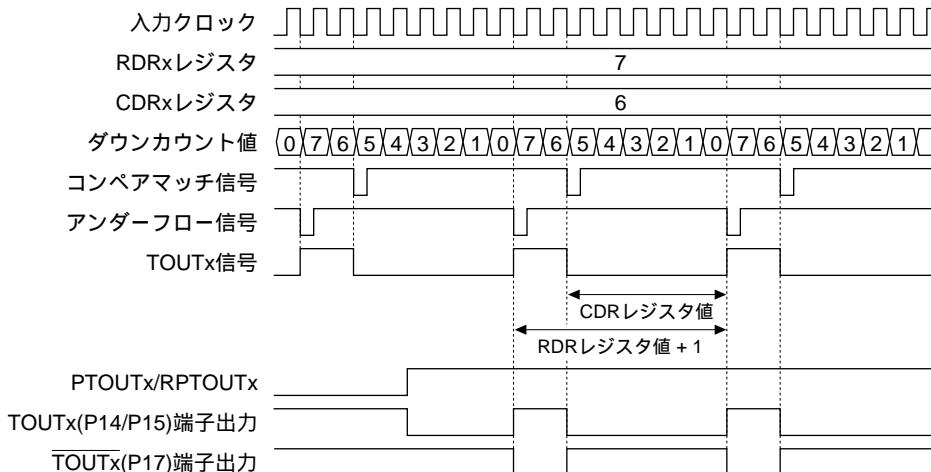

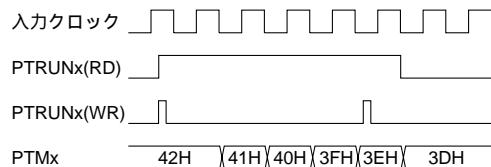

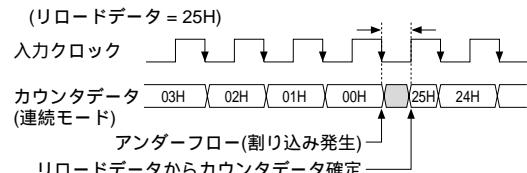

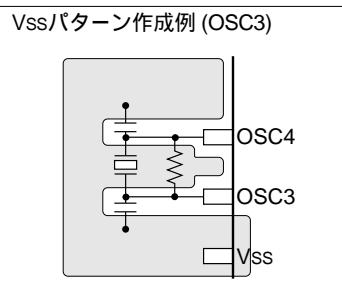

表5.1.1(d) I/Oメモリマップ(00FF19H ~ 00FF22H)