**EPSON**

CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

# S1C60N05

テクニカルマニュアル

S1C60N05 Technical Hardware

セイコーエプソン株式会社

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

## 本版で改訂または追加された箇所

| 章        | 節/項 | 頁  | 項目            | 内容            |

|----------|-----|----|---------------|---------------|

| Appendix | B.2 | 79 | A/Dコンバータの誤差要因 | 図B.2.4と説明文を追加 |

|          | C   | 82 | 特性定格<br>外形寸法図 | 表を変更<br>図を変更  |

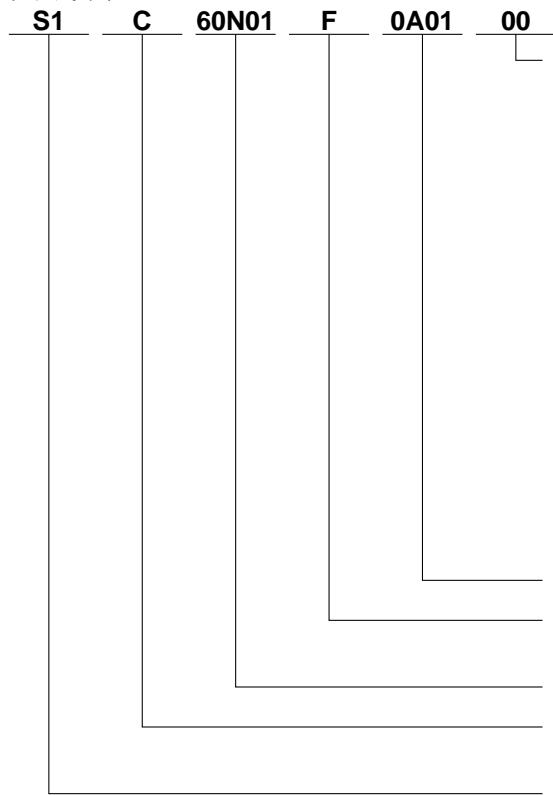

## 製品型番体系

デバイス

### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

### 仕様

[D: ベアチップ、F: QFP]

### 機種番号

#### 機種名称

[C: マイコン、デジタル製品]

#### 製品分類

[S1: 半導体]

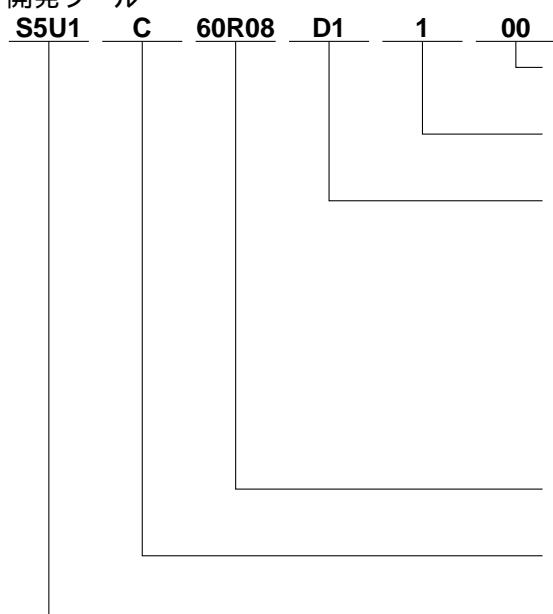

開発ツール

### 梱包仕様

[00: 標準梱包]

### バージョン

[1: Version 1]

### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ペリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

### 対応機種番号

[60R08: S1C60R08用]

### ツール分類

[C: マイコン用]

### 製品分類

[S5U1: 半導体用開発ツール]

- 目 次 -

|       |                                 |    |

|-------|---------------------------------|----|

| 1     | 概要 .....                        | 1  |

| 1.1   | 機種構成 .....                      | 1  |

| 1.2   | 特長 .....                        | 1  |

| 1.3   | ブロック図 .....                     | 2  |

| 1.4   | 端子配置図 .....                     | 3  |

| 1.5   | 端子説明 .....                      | 4  |

| 2     | 電源およびイニシャルリセット .....            | 5  |

| 2.1   | 電源 .....                        | 5  |

| 2.2   | イニシャルリセット .....                 | 7  |

| 2.2.1 | 発振検出回路 .....                    | 8  |

| 2.2.2 | リセット端子 (RESET) .....            | 8  |

| 2.2.3 | 入力ポート(K00 ~ K03)の同時HIGH入力 ..... | 8  |

| 2.2.4 | イニシャルリセット時の内部レジスタ .....         | 9  |

| 2.3   | テスト端子 (TEST) .....              | 9  |

| 3     | CPU, ROM, RAM .....             | 10 |

| 3.1   | CPU .....                       | 10 |

| 3.2   | ROM .....                       | 10 |

| 3.3   | RAM .....                       | 10 |

| 4     | 周辺回路と動作 .....                   | 11 |

| 4.1   | メモリマップ .....                    | 11 |

| 4.2   | 発振回路 .....                      | 14 |

| 4.2.1 | 水晶発振回路 .....                    | 14 |

| 4.2.2 | CR発振回路 .....                    | 14 |

|        |                                            |    |

|--------|--------------------------------------------|----|

| 4.3    | 入力ポート (K00 ~ K03) .....                    | 15 |

| 4.3.1  | 入力ポートの構成 .....                             | 15 |

| 4.3.2  | 割り込み機能 .....                               | 15 |

| 4.3.3  | マスクオプション .....                             | 16 |

| 4.3.4  | 入力ポートの制御 .....                             | 16 |

| 4.4    | 出力ポート (R00 ~ R03) .....                    | 18 |

| 4.4.1  | 出力ポートの構成 .....                             | 18 |

| 4.4.2  | マスクオプション .....                             | 19 |

| 4.4.3  | 出力ポートの制御 .....                             | 21 |

| 4.5    | 入出力兼用ポート (P00 ~ P03) .....                 | 23 |

| 4.5.1  | 入出力兼用ポートの構成 .....                          | 23 |

| 4.5.2  | I/Oコントロールレジスタと入力/出力モード .....               | 23 |

| 4.5.3  | マスクオプション .....                             | 24 |

| 4.5.4  | 入出力兼用ポートの制御 .....                          | 24 |

| 4.6    | LCD ドライバ (COM0 ~ COM3, SEG0 ~ SEG19) ..... | 26 |

| 4.6.1  | LCD ドライバの構成 .....                          | 26 |

| 4.6.2  | 発振周波数の歩度調整 .....                           | 32 |

| 4.6.3  | マスクオプション .....                             | 33 |

| 4.6.4  | LCD ドライバの制御 .....                          | 35 |

| 4.7    | 計時タイマ .....                                | 36 |

| 4.7.1  | 計時タイマの構成 .....                             | 36 |

| 4.7.2  | 割り込み機能 .....                               | 36 |

| 4.7.3  | 計時タイマの制御 .....                             | 37 |

| 4.8    | A/Dコンバータ .....                             | 39 |

| 4.8.1  | A/Dコンバータの構成 .....                          | 39 |

| 4.8.2  | A/Dコンバータの動作 .....                          | 40 |

| 4.8.3  | 割り込み機能 .....                               | 43 |

| 4.8.4  | A/Dコンバータの使用例 .....                         | 44 |

| 4.8.5  | A/Dコンバータの制御 .....                          | 45 |

| 4.9    | 重負荷保護機能 .....                              | 48 |

| 4.9.1  | 重負荷保護機能の動作 .....                           | 48 |

| 4.9.2  | 重負荷保護機能の制御 .....                           | 48 |

| 4.10   | 割り込みとHALT .....                            | 49 |

| 4.10.1 | 割り込み要因 .....                               | 50 |

| 4.10.2 | 割り込みの個別マスク .....                           | 51 |

| 4.10.3 | 割り込みベクタ .....                              | 51 |

| 4.10.4 | 割り込みの制御 .....                              | 52 |

|                              |    |

|------------------------------|----|

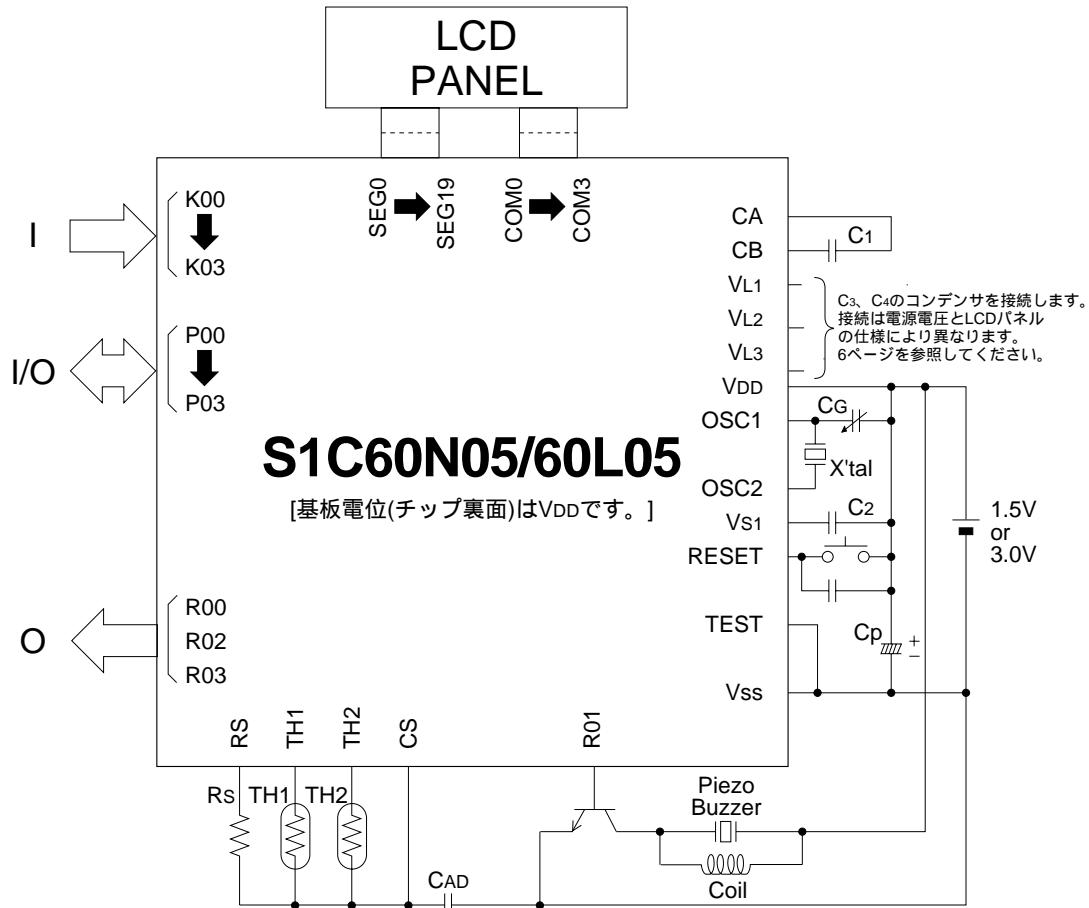

| 5 基本外部結線図 .....              | 53 |

| 6 電気的特性 .....                | 55 |

| 6.1 絶対最大定格 .....             | 55 |

| 6.2 推奨動作条件 .....             | 56 |

| 6.3 DC特性 .....               | 57 |

| 6.4 アナログ回路特性・消費電流 .....      | 59 |

| 6.5 発振特性 .....               | 63 |

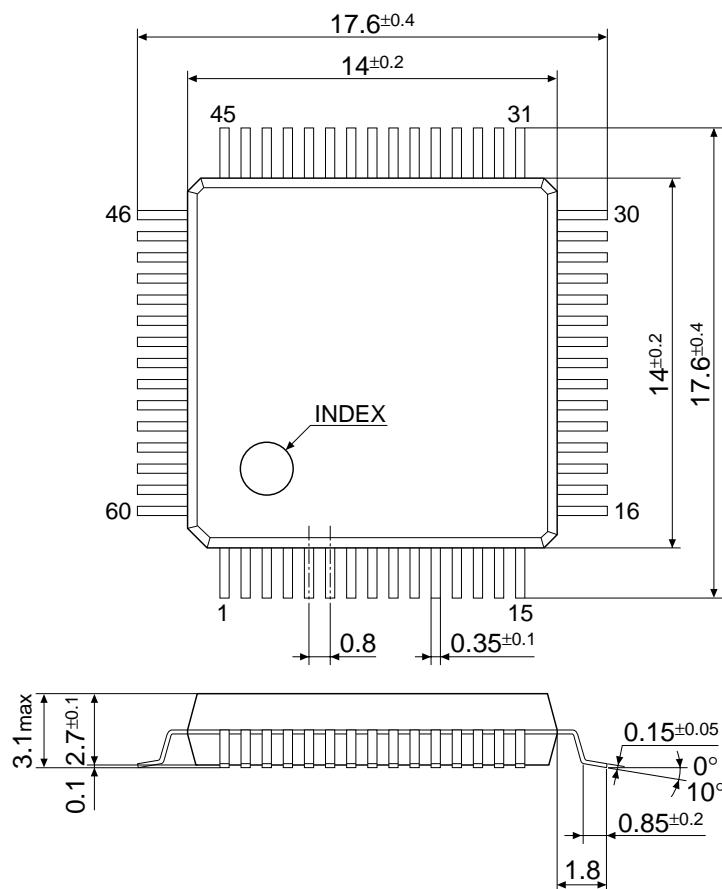

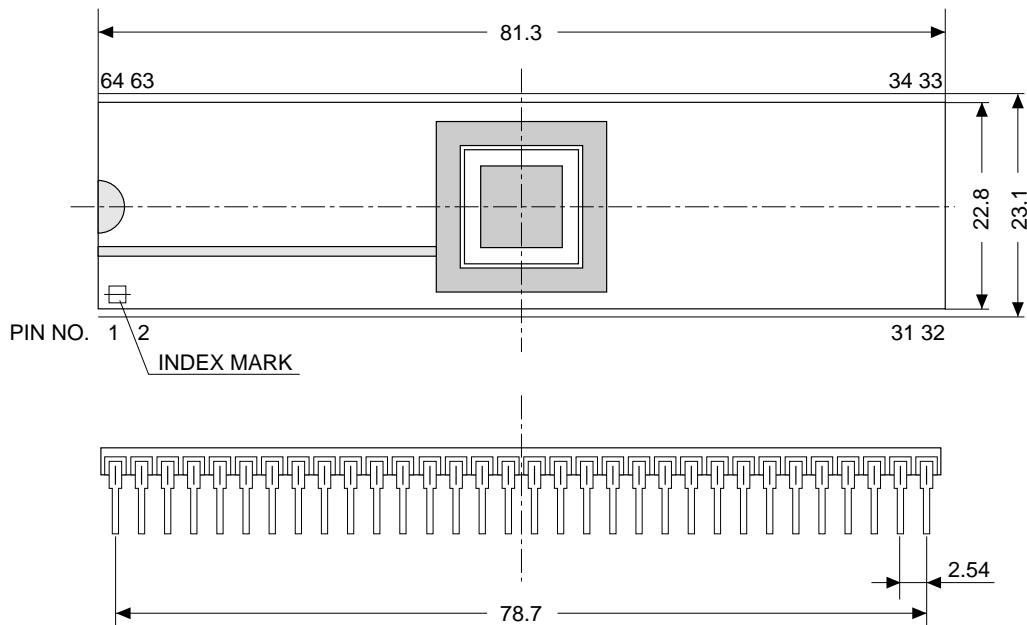

| 7 パッケージ .....                | 65 |

| 7.1 プラスチックパッケージ .....        | 65 |

| 7.2 テストサンプル用セラミックパッケージ ..... | 66 |

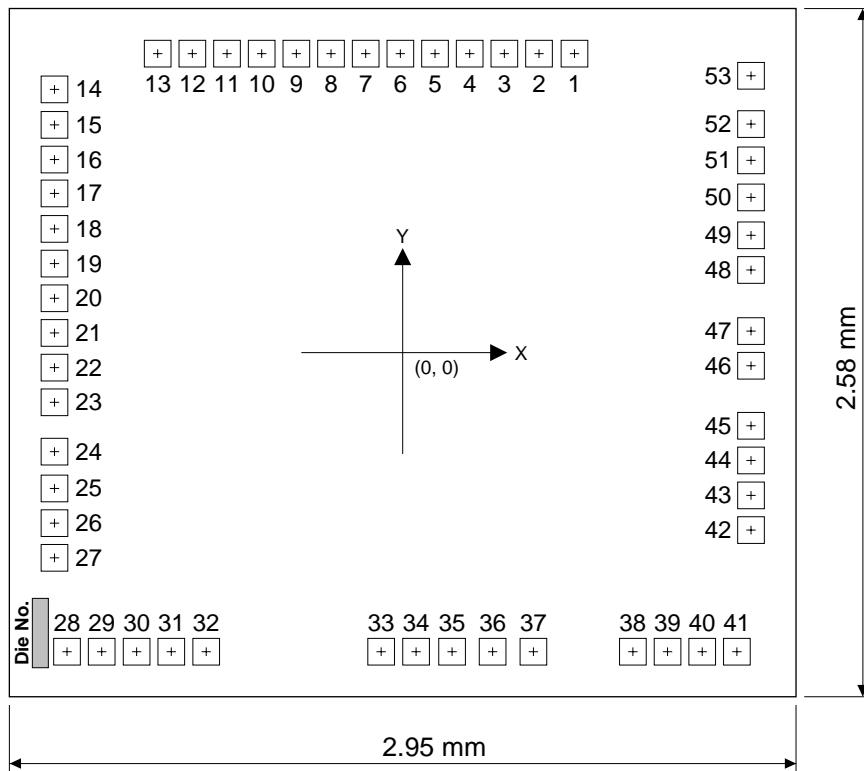

| 8 パッド配置 .....                | 67 |

| 8.1 パッド配置図 .....             | 67 |

| 8.2 パッド座標 .....              | 68 |

| 9 実装上の注意事項 .....             | 69 |

| Appendix S1C60N05技術情報 .....  | 71 |

| A 温度計の設計手順 .....             | 71 |

| A.1 設計手順 .....               | 71 |

| A.2 コンデンサ容量と発振周波数の求め方 .....  | 73 |

| A.3 アップカウンタ初期値の設定 .....      | 73 |

| A.4 直線近似による表示温度の算出 .....     | 74 |

| B 誤差要因 .....                 | 76 |

| B.1 サーミスタ抵抗値のばらつき .....      | 76 |

| B.2 A/Dコンバータの誤差要因 .....      | 76 |

| B.3 浮遊容量による誤差 .....          | 80 |

| B.4 ソフトウェア上の誤差 .....         | 80 |

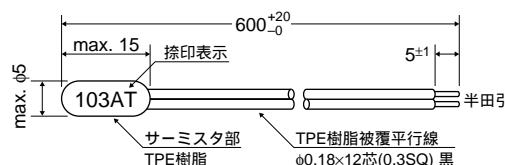

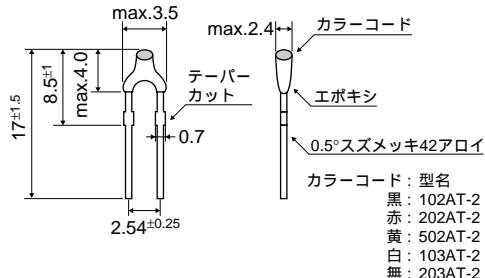

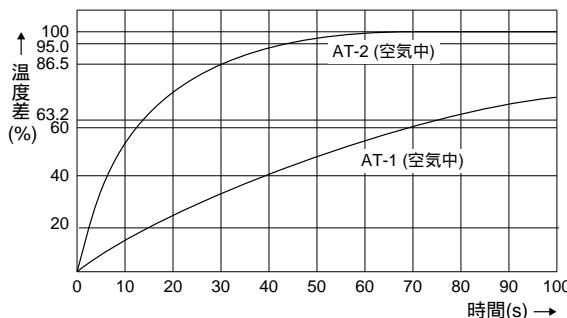

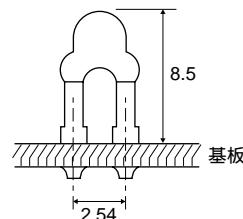

| C 参考: ATサーミスタの仕様 .....       | 81 |

# 1 概要

---

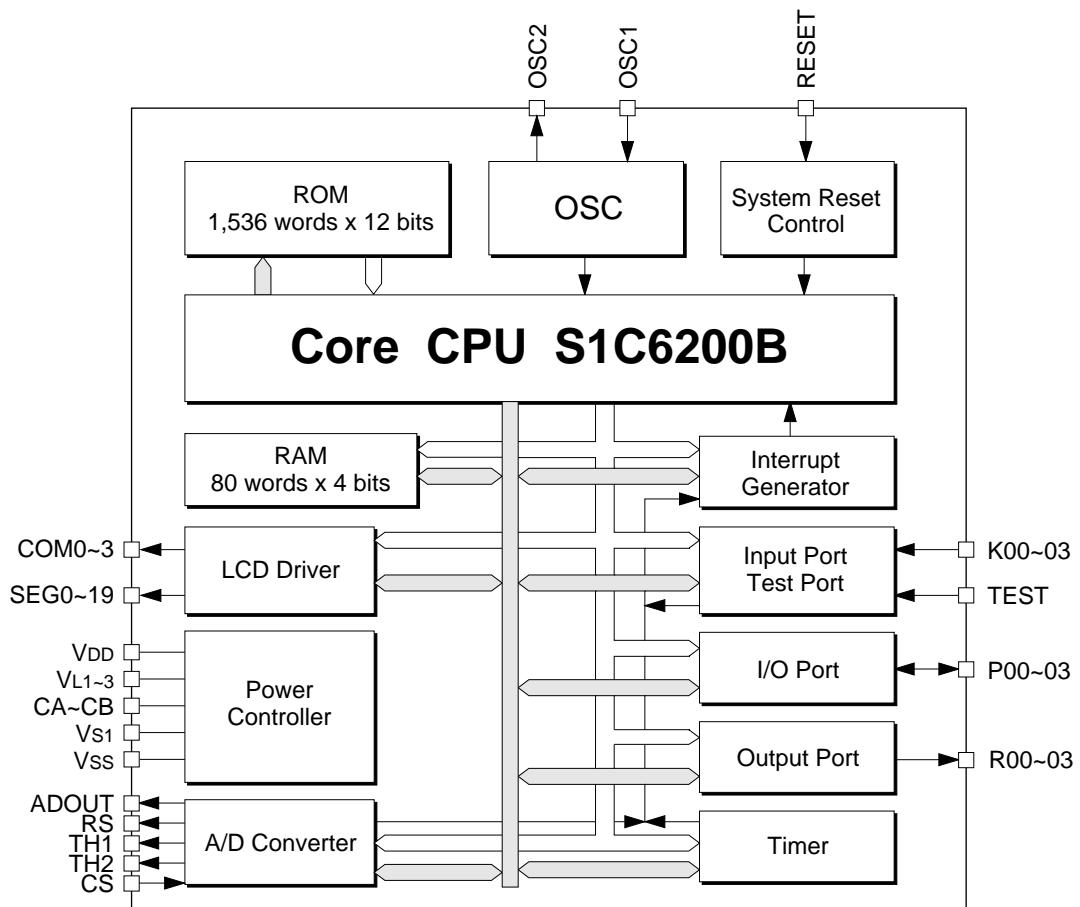

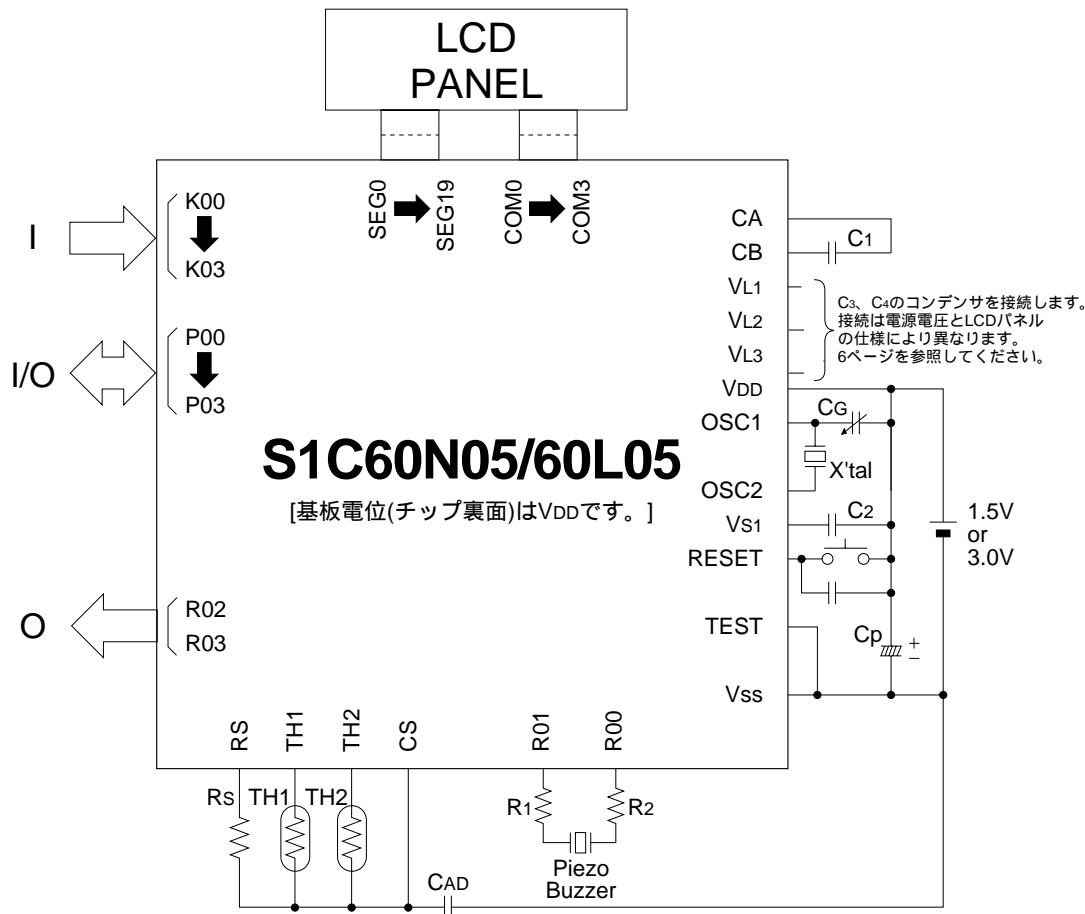

S1C60N05シリーズは4ビットコアCPU S1C6200Bを中心にして、1,536ワードのROM(12ビット/ワード)、80ワードのRAM(4ビット/ワード)、LCDドライバ、入力ポート4ビット(K00～K03)、出力ポート4ビット(R00～R03)、入出力兼用ポート4ビット(P00～P03)、計時タイマ、A/Dコンバータを内蔵した4ビットシングルチップマイクロコンピュータです。S1C60N05シリーズは低電圧動作、低消費電力であるため、各種システムに広範囲に対応できます。

## 1.1 機種構成

S1C60N05シリーズは使用する電源電圧により、次のような機種構成となります。

表1.1.1 機種構成

| 機種名      | 電源電圧     | 発振回路            |

|----------|----------|-----------------|

| S1C60N05 | 1.8～3.5V | 水晶発振回路またはCR発振回路 |

| S1C60L05 | 1.2～2.0V | 水晶発振回路またはCR発振回路 |

## 1.2 特長

- コアCPU ..... S1C6200B

- 内蔵発振回路 ..... 水晶発振回路またはCR発振回路 32,768Hz (Typ.)

- インストラクションセット ..... 100種類

- ROM容量 ..... 1,536ワード×12ビット

- RAM容量 ..... 80ワード×4ビット

- 入力ポート ..... 4ビット(マスクオプションによりプルダウン抵抗の付加が可能)

- 出力ポート ..... 4ビット(マスクオプションによりピエゾブザーのダイレクト駆動とプログラマブル周波数出力が可能)

- 入出力兼用ポート ..... 4ビット

- LCDドライバ ..... 20セグメント×4コモン(または3、2コモン)

- タイムベースカウンタ ..... 計時タイマ

- A/Dコンバータ ..... CR発振方式 A/Dコンバータ内蔵(2チャンネル)

- 割り込み 外部割り込み： ..... 入力ポート割り込み 1系統

内部割り込み： ..... タイマ割り込み 1系統

A/Dコンバータ割り込み 1系統

- 電源電圧 ..... 1.5V (1.2V～2.0V) S1C60L05 (A/D変換時)

3.0V (1.8V～3.5V) S1C60N05

- 消費電流 (Typ.値) ..... 0.8μA (水晶発振 CLK=32,768Hz、HALT時)

1.5μA (水晶発振 CLK=32,768Hz、実行時)

- 出荷形態 ..... QFP6-60pin(プラスチック)またはチップ

## 1.3 ブロック図

図1.3.1 ブロック図

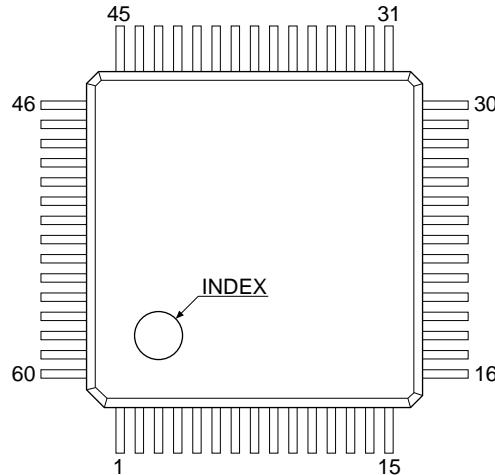

## 1.4 端子配置図

**QFP6-60pin**

| ピン番号 | 端子名 | ピン番号 | 端子名   | ピン番号 | 端子名   | ピン番号 | 端子名  |

|------|-----|------|-------|------|-------|------|------|

| 1    | 非接続 | 16   | 非接続   | 31   | TEST  | 46   | VL3  |

| 2    | 非接続 | 17   | ADOUT | 32   | RESET | 47   | VL2  |

| 3    | K00 | 18   | SEG0  | 33   | SEG12 | 48   | VL1  |

| 4    | K01 | 19   | SEG1  | 34   | SEG13 | 49   | CA   |

| 5    | K02 | 20   | SEG2  | 35   | SEG14 | 50   | CB   |

| 6    | K03 | 21   | SEG3  | 36   | SEG15 | 51   | VSS  |

| 7    | R00 | 22   | SEG4  | 37   | SEG16 | 52   | VDD  |

| 8    | R01 | 23   | SEG5  | 38   | SEG17 | 53   | OSC1 |

| 9    | R02 | 24   | SEG6  | 39   | SEG18 | 54   | OSC2 |

| 10   | R03 | 25   | SEG7  | 40   | SEG19 | 55   | VS1  |

| 11   | RS  | 26   | SEG8  | 41   | COM0  | 56   | P00  |

| 12   | TH1 | 27   | SEG9  | 42   | COM1  | 57   | P01  |

| 13   | TH2 | 28   | SEG10 | 43   | COM2  | 58   | P02  |

| 14   | CS  | 29   | SEG11 | 44   | COM3  | 59   | P03  |

| 15   | 非接続 | 30   | 非接続   | 45   | 非接続   | 60   | 非接続  |

図1.4.1 端子配置図

## 1.5 端子説明

表1.5.1 端子説明

| 端子名             | ピン番号           | 入出力 | 機能                                      |

|-----------------|----------------|-----|-----------------------------------------|

| VDD             | 52             | (I) | 電源(+)端子                                 |

| VSS             | 51             | (I) | 電源(-)端子                                 |

| V <sub>S1</sub> | 55             | O   | 発振および内部ロジック系定電圧出力端子                     |

| V <sub>L1</sub> | 48             | O   | LCD系定電圧出力端子                             |

| V <sub>L2</sub> | 47             | O   | LCD系昇圧出力端子                              |

| V <sub>L3</sub> | 46             | O   | LCD系昇圧出力端子                              |

| CA, CB          | 49, 50         | -   | 昇圧キャパシタ接続端子                             |

| OSC1            | 53             | I   | 水晶またはCR発振入力端子                           |

| OSC2            | 54             | O   | 水晶またはCR発振出力端子                           |

| K00~K03         | 3~6            | I   | 入力端子                                    |

| P00~P03         | 56~59          | I/O | 入出力端子                                   |

| R00~R03         | 7~10           | O   | 出力端子                                    |

| SEGO~19         | 18~29<br>33~40 | O   | LCDセグメント出力端子<br>(マスクオプションによりDC出力端子へ転用可) |

| COM0~3          | 41~44          | O   | LCDコモン出力端子                              |

| CS              | 14             | I   | A/Dコンバータ CR発振入力端子                       |

| RS              | 11             | O   | A/Dコンバータ CR発振出力端子                       |

| TH1, TH2        | 12, 13         | O   | A/Dコンバータ CR発振出力端子                       |

| ADOUT           | 17             | O   | A/Dコンバータ 発振周波数出力端子                      |

| RESET           | 32             | I   | 初期設定入力端子                                |

| TEST            | 31             | I   | テスト入力端子                                 |

## 2 電源およびイニシャルリセット

### 2.1 電源

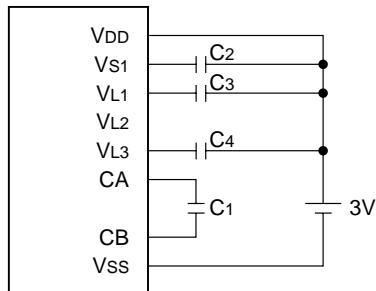

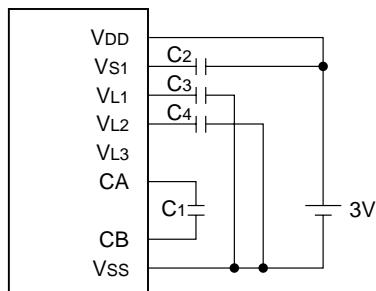

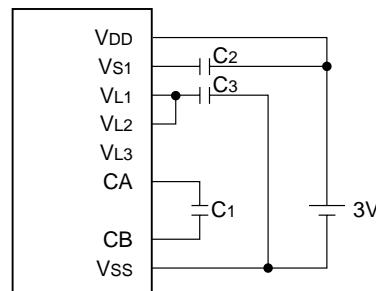

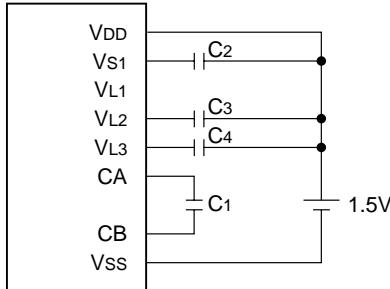

S1C60N05シリーズは外部より単一電源(\*)をV<sub>DD</sub> - V<sub>SS</sub>間に与えることにより、内部で必要な電圧を定電圧回路(発振回路および内部回路用電圧<V<sub>S1</sub>>)および昇降圧回路(LCD駆動用電圧<V<sub>L2</sub>、V<sub>L3</sub>またはV<sub>L1</sub>、V<sub>L3</sub>>)により発生します。

S1C60N05の4.5V LCDパネル用電源をマスクオプションで選択した場合、<V<sub>L2</sub>>はIC内部で<V<sub>SS</sub>>と短絡され、<V<sub>L1</sub>>と<V<sub>L3</sub>>が昇降圧回路より出力されます。3.0Vパネル用電源を選択した場合は<V<sub>L3</sub>>がIC内部で<V<sub>SS</sub>>と短絡され、<V<sub>L1</sub>>と<V<sub>L2</sub>>が降圧回路より出力されます。

S1C60L05では<V<sub>L1</sub>>がIC内部で<V<sub>SS</sub>>と短絡され、<V<sub>L2</sub>>と<V<sub>L3</sub>>が昇圧回路より出力されます。定電圧回路にて発生される内部回路用電圧<V<sub>S1</sub>>は-1.2V(V<sub>DD</sub>基準)となります。

\* 電源電圧: S1C60N05 ..... 3.0V

S1C60L05 ..... 1.5V

- 注:

- 定電圧回路および昇降圧回路の出力電圧による外付け負荷の駆動は禁止します。

- 電圧値については"6 電気的特性"を参照してください。

図2.1.1にLCD系定電圧回路を使用しない場合の外付け部品の構成を示します。

S1C60N05の場合

<LCD 4.5V用パネル>

1/4、1/3、1/2デューティ、1/3バイアス

注: IC内部でVL2とVssが短絡されます。

<LCD 3V用パネル>

1/4、1/3、1/2デューティ、1/3バイアス

1/4、1/3、1/2デューティ、1/2バイアス

注: IC内部でVL3とVssが短絡されます。

S1C60L05の場合

<LCD 4.5V用パネル>

1/4、1/3、1/2デューティ、1/3バイアス

<LCD 3V用パネル>

1/4、1/3、1/2デューティ、1/2バイアス

注: IC内部でVL1とVssが短絡されます。

図2.1.1 LCD系定電圧回路を使用しない場合の外付け部品の構成

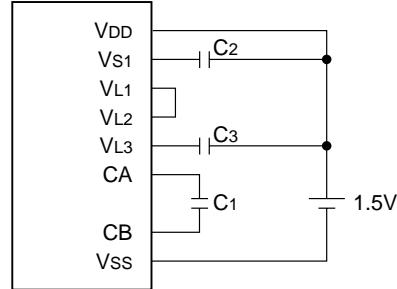

## 2.2 イニシャルリセット

S1C60N05シリーズは回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては以下の3種類があります。

- (1) 発振検出回路によるイニシャルリセット(注)

- (2) RESET端子による外部イニシャルリセット

- (3) K00～K03端子の同時HIGHレベル入力による外部イニシャルリセット(マスクオプションで設定)

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

注: (1)の発振検出回路によるイニシャルリセットは、電源の投入方法により回路が正常に動作しない場合もありますので、(2)、(3)に示すいずれかのイニシャルリセットの方法を採用してください。

### 2.2.1 発振検出回路

発振検出回路は電源投入時に発振回路が発振を開始するまで、または何らかの原因で発振回路が停止した場合にイニシャルリセット信号を出力しますが、発振検出回路によるイニシャルリセットは、電源の投入方法により回路が正常に動作しない場合もありますので、以下に示すいずれかのイニシャルリセットの方法を採用してください。

### 2.2.2 リセット端子 (RESET)

外部よりリセット端子をHIGHレベルにすることにより、イニシャルリセットが行えます。イニシャルリセット回路はノイズリジェクト回路を内蔵しているため、5ms(発振周波数fosc=32kHzの場合)以上HIGHレベルを保ってください。リセット端子がLOWレベルになると、CPUが動作を開始します。

### 2.2.3 入力ポート(K00 ~ K03)の同時HIGH入力

マスクオプションで選択された入力ポート(K00 ~ K03)に外部から同時にHIGH入力を与えることによりイニシャルリセットが行えます。ノイズリジェクト回路を内蔵しているため、4秒(発振周波数fosc=32kHzの場合)以上、指定の入力ポート端子をHIGHレベルに保ってください。表2.2.3.1にマスクオプションで選択できる入力ポート(K00 ~ K03)の組合せを示します。

表2.2.3.1 入力ポートの組合せ

|   |                       |

|---|-----------------------|

| A | 使用しない                 |

| B | K00 * K01             |

| C | K00 * K01 * K02       |

| D | K00 * K01 * K02 * K03 |

たとえば、マスクオプションでDの"K00 \* K01 \* K02 \* K03"を選択した場合、K00 ~ K03の4端子の入力が同時にHIGHレベルになったときにイニシャルリセットを行います。

なお、この機能を使用する場合、通常動作時に指定ポートが同時にHIGHレベルにならないように注意してください。

### 2.2.4 イニシャルリセット時の内部レジスタ

イニシャルリセットにより、CPUは以下のように初期化されます。

表2.2.4.1 初期設定値

| CPU コア        |     |      |     |

|---------------|-----|------|-----|

| 名 称           | 記号  | ビット長 | 設定値 |

| プログラムカウンタステップ | PCS | 8    | 00H |

| プログラムカウンタページ  | PCP | 4    | 1H  |

| ニューページポインタ    | NPP | 4    | 1H  |

| スタックポインタ      | SP  | 8    | 不定  |

| インデックスレジスタX   | X   | 8    | 不定  |

| インデックスレジスタY   | Y   | 8    | 不定  |

| レジスタポインタ      | RP  | 4    | 不定  |

| 汎用Aレジスタ       | A   | 4    | 不定  |

| 汎用Bレジスタ       | B   | 4    | 不定  |

| 割り込みフラグ       | I   | 1    | 0   |

| デシマルフラグ       | D   | 1    | 0   |

| ゼロフラグ         | Z   | 1    | 不定  |

| キャリーフラグ       | C   | 1    | 不定  |

| 周辺回路     |      |     |

|----------|------|-----|

| 名 称      | ビット長 | 設定値 |

| RAM      | 80×4 | 不定  |

| 表示メモリ    | 20×4 | 不定  |

| その他の周辺回路 | -    | *   |

\* "4.1 メモリマップ"参照

### 2.3 テスト端子 (TEST)

ICの出荷検査時に使用する端子です。通常動作時は必ずVssに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C60N05シリーズはCPU部分に4ビットコアCPU S1C6200Bを使用しているため、レジスタ構成、命令等は他のS1C6200Bを使用したファミリプロセッサとほぼ同様です。S1C6200Bについては "S1C6200/6200AコアCPUマニュアル"を参照してください。

なお、S1C60N05シリーズにおいては、以下の点に注意してください。

- (1) SLEEP動作を想定していないため、SLP命令は使用できません。

- (2) ROM容量が1,536ワード(12ビット/ワード)のためバンクビットの必要がなく、PCBおよびNBPは使用していません。

- (3) RAMは0ページのみの設定となっているため、RAMアドレスの指定を行うインデックスレジスタのページ部分(XP、YP)は無効となります。

このため、以下の命令は使用できません。

|      |      |      |      |

|------|------|------|------|

| PUSH | XP   | PUSH | YP   |

| POP  | XP   | POP  | YP   |

| LD   | XP,r | LD   | YP,r |

| LD   | r,XP | LD   | r,YP |

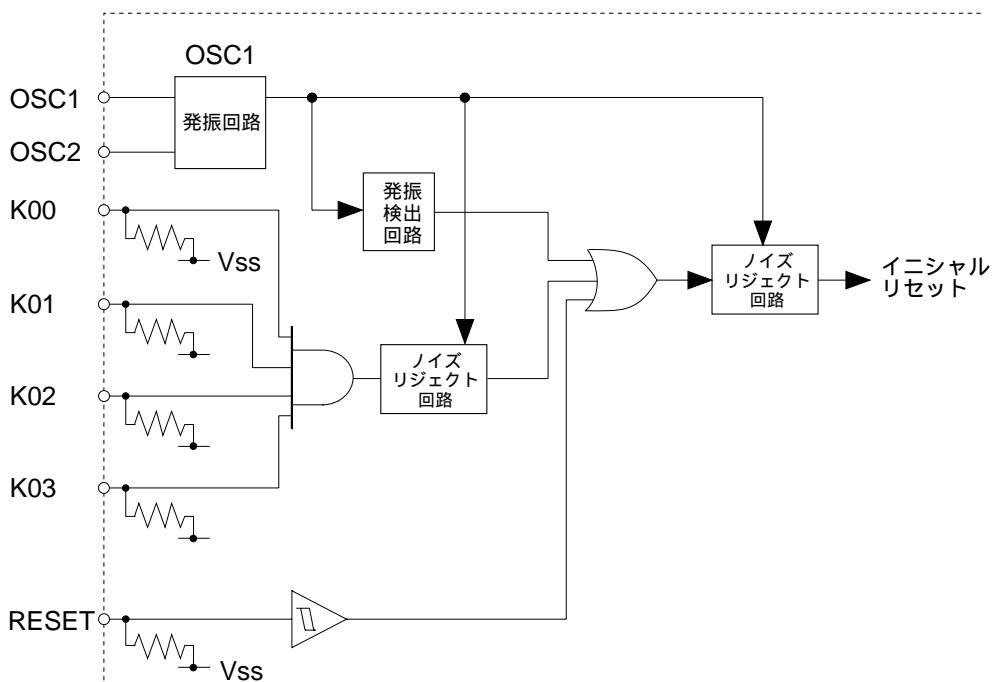

### 3.2 ROM

内蔵ROMはプログラム格納用のマスクROMで、1,536ステップ×12ビットの容量があります。プログラム領域は6ページ(0～5)×256ステップ(00H～FFH)となっており、イニシャルリセット後のプログラム開始番地が1ページ00Hステップに、割り込みベクタが1ページ01H～07Hステップに割り当てられています。

図3.2.1 ROMの構成

### 3.3 RAM

RAMは種々のデータを格納するデータメモリで、80ワード×4ビットの容量があります。プログラミングの際には以下の点に注意してください。

- (1) RAMの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データ領域とスタック領域が重ならないように注意してください。

- (2) サブルーチンコール、割り込み等ではスタック領域を3ワード消費します。

- (3) RAMのアドレス00H～0FHはレジスタポインタRPによってアドレス指定されるメモリレジスタ領域です。

## 4 周辺回路と動作

S1C60N05シリーズの周辺回路(タイマ、I/O等)はメモリマップド方式でCPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下、各周辺回路の動作について説明します。

### 4.1 メモリマップ

S1C60N05シリーズのデータメモリは137ワードのアドレス空間を持っており、そのうち32ワードが表示メモリ、25ワードがI/Oメモリとして割り付けられています。

図4.1.1にS1C60N05シリーズの全体のメモリマップを、表4.1.1(a)、(b)に周辺回路(I/O空間)のメモリマップを示します。

| Address | Low  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | A  | B  | C  | D  | E  | F  |

|---------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Page    | High |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 0       | 0    | M0 | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 | M9 | MA | MB | MC | MD | ME | MF |

|         | 1    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 2    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 3    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 4    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 5    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 6    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 7    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 8    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 9    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | A    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | B    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | C    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | D    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | E    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | F    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

未使用領域

図4.1.1 メモリマップ

注: メモリマップ中の未使用領域、およびこの章で示されていないメモリ領域にはメモリが実装されていません。このため、これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

表4.1.1(a) I/Oメモリマップ(アドレス 0E0H ~ 0EFH)

| アドレス | レジスタ  |       |       |       | Name  | Init *1 | 1      | 0    | 注釈                       |

|------|-------|-------|-------|-------|-------|---------|--------|------|--------------------------|

|      | D3    | D2    | D1    | D0    |       |         |        |      |                          |

| 0E0H | K03   | K02   | K01   | K00   | K03   | - *2    | High   | Low  | 入力ポートデータ K03             |

|      | R     |       |       |       | K02   | - *2    | High   | Low  | 入力ポートデータ K02             |

|      | R     |       |       |       | K01   | - *2    | High   | Low  | 入力ポートデータ K01             |

|      | R     |       |       |       | K00   | - *2    | High   | Low  | 入力ポートデータ K00             |

| 0E3H | TM3   | TM2   | TM1   | TM0   | TM3   | - *3    | High   | Low  | 計時タイマデータ 2Hz             |

|      | R     |       |       |       | TM2   | - *3    | High   | Low  | 計時タイマデータ 4Hz             |

|      | R     |       |       |       | TM1   | - *3    | High   | Low  | 計時タイマデータ 8Hz             |

|      | R     |       |       |       | TM0   | - *3    | High   | Low  | 計時タイマデータ 16Hz            |

| 0E4H | TC3   | TC2   | TC1   | TC0   | TC3   | - *3    | 1      | 0    | アップダウンカウンタデータ TC3        |

|      | R/W   |       |       |       | TC2   | - *3    | 1      | 0    | アップダウンカウンタデータ TC2        |

|      | R/W   |       |       |       | TC1   | - *3    | 1      | 0    | アップダウンカウンタデータ TC1        |

|      | R/W   |       |       |       | TC0   | - *3    | 1      | 0    | アップダウンカウンタデータ TC0 (LSB)  |

| 0E5H | TC7   | TC6   | TC5   | TC4   | TC7   | - *3    | 1      | 0    | アップダウンカウンタデータ TC7        |

|      | R/W   |       |       |       | TC6   | - *3    | 1      | 0    | アップダウンカウンタデータ TC6        |

|      | R/W   |       |       |       | TC5   | - *3    | 1      | 0    | アップダウンカウンタデータ TC5        |

|      | R/W   |       |       |       | TC4   | - *3    | 1      | 0    | アップダウンカウンタデータ TC4        |

| 0E6H | TC11  | TC10  | TC9   | TC8   | TC11  | - *3    | 1      | 0    | アップダウンカウンタデータ TC11       |

|      | R/W   |       |       |       | TC10  | - *3    | 1      | 0    | アップダウンカウンタデータ TC10       |

|      | R/W   |       |       |       | TC9   | - *3    | 1      | 0    | アップダウンカウンタデータ TC9        |

|      | R/W   |       |       |       | TC8   | - *3    | 1      | 0    | アップダウンカウンタデータ TC8        |

| 0E7H | TC15  | TC14  | TC13  | TC12  | TC15  | - *3    | 1      | 0    | アップダウンカウンタデータ TC15 (MSB) |

|      | R/W   |       |       |       | TC14  | - *3    | 1      | 0    | アップダウンカウンタデータ TC14       |

|      | R/W   |       |       |       | TC13  | - *3    | 1      | 0    | アップダウンカウンタデータ TC13       |

|      | R/W   |       |       |       | TC12  | - *3    | 1      | 0    | アップダウンカウンタデータ TC12       |

| 0E8H | EIK03 | EIK02 | EIK01 | EIK00 | EIK03 | 0       | Enable | Mask | 割り込みマスクレジスタ K03          |

|      | R/W   |       |       |       | EIK02 | 0       | Enable | Mask | 割り込みマスクレジスタ K02          |

|      | R/W   |       |       |       | EIK01 | 0       | Enable | Mask | 割り込みマスクレジスタ K01          |

|      | R/W   |       |       |       | EIK00 | 0       | Enable | Mask | 割り込みマスクレジスタ K00          |

| 0EBH | 0     | EIT2  | EIT8  | EIT32 | 0     | 0       | Enable | Mask | 割り込みマスクレジスタ(タイマ) 2Hz     |

|      | R/W   |       |       |       | EIT2  | 0       | Enable | Mask | 割り込みマスクレジスタ(タイマ) 8Hz     |

|      | R/W   |       |       |       | EIT8  | 0       | Enable | Mask | 割り込みマスクレジスタ(タイマ) 32Hz    |

|      | R/W   |       |       |       | EIT32 | 0       | Enable | Mask | *5                       |

| 0ECH | 0     | 0     | 0     | EIAD  | 0     | 0       |        |      | *5                       |

|      | R/W   |       |       |       | 0     | 0       |        |      | *5                       |

|      | R/W   |       |       |       | EIAD  | 0       | Enable | Mask | *5                       |

|      | R/W   |       |       |       | 0     | 0       |        |      | *5                       |

| 0EDH | 0     | 0     | 0     | IK0   | 0     | 0       |        |      | *5                       |

|      | R     |       |       |       | 0     | 0       |        |      | *5                       |

|      | R     |       |       |       | IK0   | 0       | Yes    | No   | *5                       |

|      | R     |       |       |       | IK0   | 0       | Yes    | No   | 割り込み要因フラグ(K00 ~ K03)     |

| 0EFH | 0     | IT2   | IT8   | IT32  | 0     | 0       | Yes    | No   | *4                       |

|      | R     |       |       |       | IT2   | 0       | Yes    | No   | *4                       |

|      | R     |       |       |       | IT8   | 0       | Yes    | No   | *4                       |

|      | R     |       |       |       | IT32  | 0       | Yes    | No   | *4                       |

I/Oメモリマップの \* は以下のとおりです。

\*1 イニシャルリセット時の初期値

\*2 回路上設定されない

\*3 不定

\*4 読み出し直後、リセット(0)

\*5 読み出し時は常時"0"

\*6 本編参照

表4.1.1(b) I/Oメモリマップ(アドレス 0F0H~0FEH)

| アドレス | レジスタ  |     |        |        | Name   | Init <sup>*1</sup> | 1      | 0                                                                        | 注釈                                                                                 |  |

|------|-------|-----|--------|--------|--------|--------------------|--------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

|      | D3    | D2  | D1     | D0     |        |                    |        |                                                                          |                                                                                    |  |

| 0F0H | 0     | 0   | 0      | IAD    | 0      | IAD                | Yes    | No                                                                       | 割り込み要因フラグ(A/D)<br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup><br><sup>*4</sup> |  |

|      | R     |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

|      | CHTH  | 0   | 0      | ADRUN  | CHTH   |                    | TH2    | TH1                                                                      | A/Dチャンネル選択<br><sup>*5</sup><br><sup>*5</sup>                                       |  |

|      | R/W   | R   |        | R/W    | 0      |                    |        |                                                                          |                                                                                    |  |

| 0F3H | R03   | R02 | R01    | R00    | R03    | 0                  | High   | Low                                                                      | 出力ポートデータ R03                                                                       |  |

|      |       |     | BUZZER | FOUT   | R02    | 0                  | High   | Low                                                                      | 出力ポートデータ R02                                                                       |  |

|      | R/W   |     |        |        | R01    | 0                  | High   | Low                                                                      | 出力ポートデータ R01                                                                       |  |

|      |       |     |        |        | BUZZER | 0                  | On     | Off                                                                      | ブザー On/Off 制御レジスタ                                                                  |  |

|      |       |     |        |        | R00    | 0                  | High   | Low                                                                      | 出力ポートデータ R00                                                                       |  |

|      |       |     |        |        | FOUT   | 0                  | On     | Off                                                                      | 周波数出力制御レジスタ                                                                        |  |

| 0F4H | P03   | P02 | P01    | P00    | P03    | - <sup>*2</sup>    | High   | Low                                                                      | 入出力ポートデータ P03                                                                      |  |

|      | R/W   |     |        |        | P02    | - <sup>*2</sup>    | High   | Low                                                                      | 入出力ポートデータ P02                                                                      |  |

|      |       |     |        |        | P01    | - <sup>*2</sup>    | High   | Low                                                                      | 入出力ポートデータ P01                                                                      |  |

|      |       |     |        |        | P00    | - <sup>*2</sup>    | High   | Low                                                                      | 入出力ポートデータ P00                                                                      |  |

| 0F5H | C3    | C2  | C1     | C0     | C3     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C3                                                                      |  |

|      | R/W   |     |        |        | C2     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C2                                                                      |  |

|      |       |     |        |        | C1     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C1                                                                      |  |

|      |       |     |        |        | C0     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C0 (LSB)                                                                |  |

| 0F6H | C7    | C6  | C5     | C4     | C7     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C7                                                                      |  |

|      | R/W   |     |        |        | C6     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C6                                                                      |  |

|      |       |     |        |        | C5     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C5                                                                      |  |

|      |       |     |        |        | C4     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C4                                                                      |  |

| 0F7H | C11   | C10 | C9     | C8     | C11    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C11                                                                     |  |

|      | R/W   |     |        |        | C10    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C10                                                                     |  |

|      |       |     |        |        | C9     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C9                                                                      |  |

|      |       |     |        |        | C8     | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C8                                                                      |  |

| 0F8H | C15   | C14 | C13    | C12    | C15    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C15 (MSB)                                                               |  |

|      | R/W   |     |        |        | C14    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C14                                                                     |  |

|      |       |     |        |        | C13    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C13                                                                     |  |

|      |       |     |        |        | C12    | - <sup>*3</sup>    | 1      | 0                                                                        | アップカウンタデータ C12                                                                     |  |

| 0F9H | 0     | 0   | 0      | TMRST  | 0      | TMRST              | Reset  | -                                                                        | 計時タイマリセット<br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup>      |  |

|      | R     |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

|      | W     |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

|      |       |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

| 0FAH | HLMOD | 0   | 0      | 0      | HLMOD  | 0                  | Heavy  | Normal                                                                   | 重負荷保護モード<br><sup>*5</sup><br><sup>*5</sup>                                         |  |

|      | R/W   | R   |        |        | 0      | 0                  |        |                                                                          |                                                                                    |  |

| 0FBH | CSDC  | 0   | 0      | 0      | CSDC   | 0                  | Static | Dynamic                                                                  | LCD駆動切り換え<br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup>                       |  |

|      | R/W   | R   |        |        | 0      | 0                  |        |                                                                          |                                                                                    |  |

| 0FCH | 0     | 0   | 0      | IOC    | 0      | IOC                | Out    | In                                                                       | 入出力 In/Out 制御レジスタ<br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup>               |  |

|      | R     |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

|      | R/W   |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

|      |       |     |        |        | 0      |                    |        |                                                                          |                                                                                    |  |

| 0FDH | XBZR  | 0   | XFOUT1 | XFOUT0 | XBZR   | 0                  | 2kHz   | 4kHz                                                                     | ブザー周波数制御<br><sup>*5</sup><br><sup>*6</sup>                                         |  |

|      | R/W   | R   | R/W    |        | XFOUT1 | 0                  |        |                                                                          |                                                                                    |  |

| 0FEH | 0     | 0   | 0      | ADCLK  | 0      | 65kHz              | 32kHz  | A/Dクロック選択 65kHz/32kHz<br><sup>*5</sup><br><sup>*5</sup><br><sup>*5</sup> |                                                                                    |  |

|      | R     |     |        |        | ADCLK  | 0                  |        |                                                                          |                                                                                    |  |

## 4.2 発振回路

S1C60N05シリーズは発振回路を内蔵しています。

発振回路は水晶発振またはCR発振がマスクオプションによって選択できます。

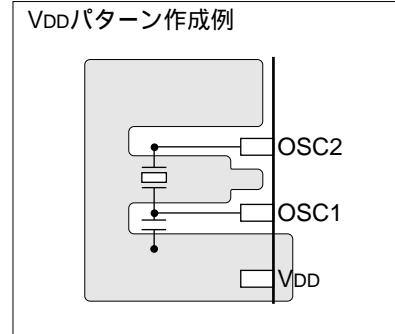

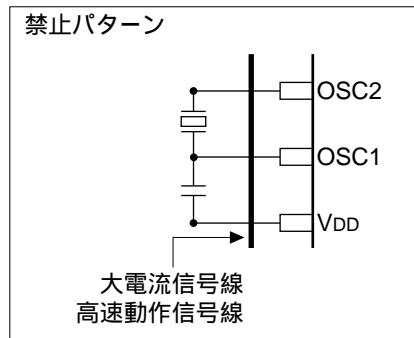

### 4.2.1 水晶発振回路

水晶発振回路は外付け素子として水晶振動子(Typ. 32.768kHz)とトリマコンデンサ(5~25pF)を接続することにより、CPUおよび周辺回路の動作クロックを発生します。

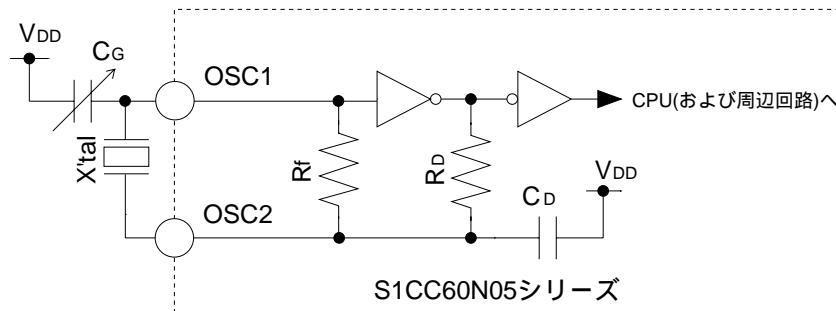

図4.2.1.1に水晶発振回路の構成を示します。

図4.2.1.1 水晶発振回路の構成

図4.2.1.1に示すとおり、OSC1端子とOSC2端子間に水晶振動子(X'tal)を、OSC1端子とVDD間にトリマコンデンサ(CG)をそれぞれ接続することにより、容易に水晶発振回路を構成することができます。

### 4.2.2 CR発振回路

S1C60N05シリーズはマスクオプションによりCR発振回路(Typ. 65kHz)を選択することができます。

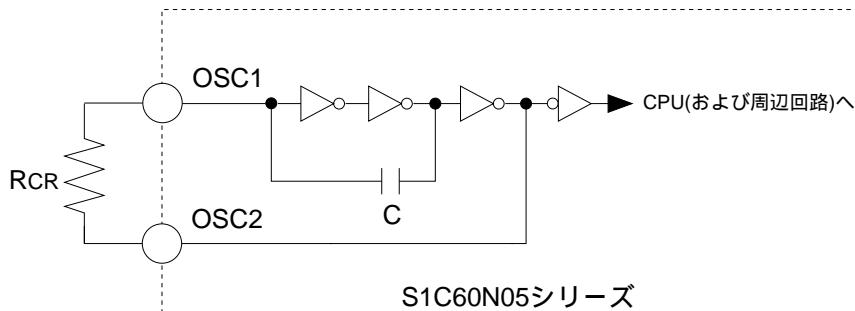

図4.2.2.1にCR発振回路の構成を示します。

図4.2.2.1 CR発振回路の構成

図4.2.2.1に示すとおり、容量(C)が内蔵されているため、OSC1端子とOSC2端子間に抵抗(RCR)を接続するだけでCR発振回路を構成することができます。RCRの値については"6 電気的特性"を参照してください。

## 4.3 入力ポート (K00 ~ K03)

### 4.3.1 入力ポートの構成

S1C60N05シリーズは4ビットの汎用入力ポートを内蔵しています。入力ポートの各ビットにはマスクオプションによりプルダウン抵抗を付加することができます。

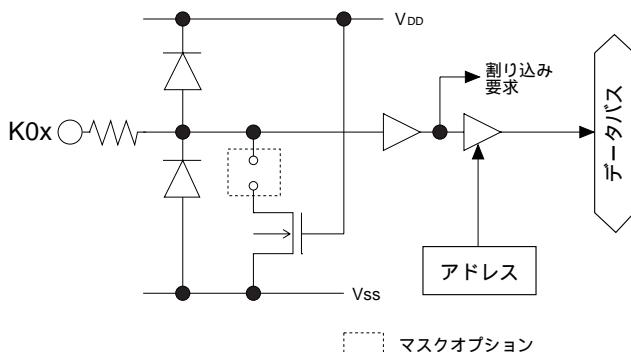

図4.3.1.1に入力ポートの構成を示します。

図4.3.1.1 入力ポートの構成

マスクオプションにより入力ポートにプルダウン抵抗を付加した場合、プッシュスイッチ、キーマトリクス等の入力に適当です。プルダウン抵抗を付加しない場合はスライドスイッチ、他LSIとのインターフェースなどに使用できます。

### 4.3.2 割り込み機能

入力ポート4ビット(K00 ~ K03)は、すべて割り込み機能を持っています。割り込みの発生条件と割り込みのマスクは、ソフトウェアにより各ビット個別に設定することができます。

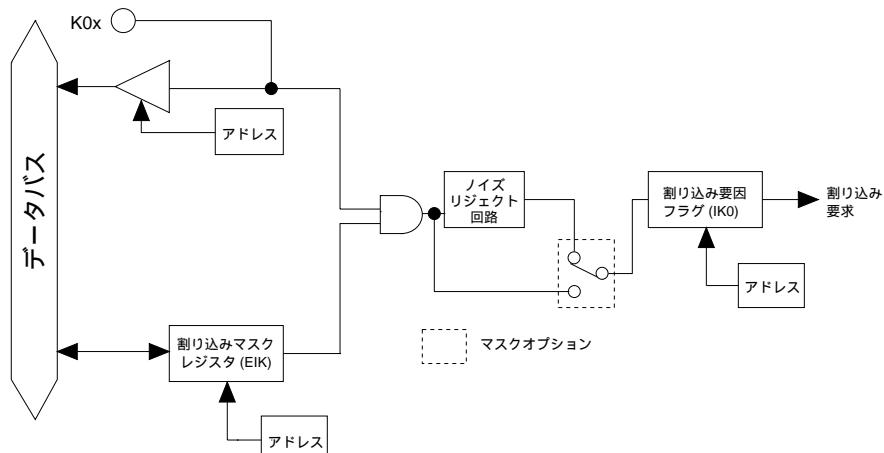

図4.3.2.1に入力割り込み回路の構成を示します。

図4.3.2.1 入力割り込み回路の構成

割り込みマスクレジスタEIK00 ~ EIK03により、入力割り込みのマスクを個別に設定することができます。K00 ~ K03の入力割り込みは、割り込みマスクレジスタにより割り込みが許可されている入力の立上りエッジで発生します。このとき、割り込み要因フラグIK0が"1"にセットされます。

### 4.3.3 マスクオプション

入力ポートのマスクオプションで選択できる内容は以下のとおりです。

- (1) 4ビットの入力ポート(K00 ~ K03)に対して、1ビットごとに内蔵プルダウン抵抗の有無を選択できます。

"プルダウン抵抗なし"を選択した場合は、入力にフローティング状態が発生しないように注意してください。

使用しない入力ポートには"プルダウン抵抗あり"を選択してください。

- (2) ノイズ等による割り込みの誤発生を防ぐため、入力割り込み回路にはノイズリジェクト回路が内蔵されています。

このノイズリジェクト回路を使用するかしないか、入力端子ごとに選択できます。

"使用する"を選択した場合、割り込み条件成立から割り込み要因フラグIK0が"1"にセットされるまで、最大0.5ms(fosc=32kHz)の遅延が生じます。

### 4.3.4 入力ポートの制御

表4.3.4.1に入力ポートの制御レジスタを示します。

表4.3.4.1 I/Oメモリ(入力ポート)

| アドレス | レジスタ  |       |       |       | Name  | Init <sup>*1</sup> | 1      | 0    | 注釈                                 |

|------|-------|-------|-------|-------|-------|--------------------|--------|------|------------------------------------|

|      | D3    | D2    | D1    | D0    |       |                    |        |      |                                    |

| 0E0H | K03   | K02   | K01   | K00   | K03   | - <sup>*2</sup>    | High   | Low  | 入力ポートデータ K03                       |

|      |       |       |       | R     | K02   | - <sup>*2</sup>    | High   | Low  | 入力ポートデータ K02                       |

|      |       |       |       |       | K01   | - <sup>*2</sup>    | High   | Low  | 入力ポートデータ K01                       |

|      |       |       |       |       | K00   | - <sup>*2</sup>    | High   | Low  | 入力ポートデータ K00                       |

| 0E8H | EIK03 | EIK02 | EIK01 | EIK00 | EIK03 | 0                  | Enable | Mask | 割り込みマスクレジスタ K03                    |

|      |       |       |       | R/W   | EIK02 | 0                  | Enable | Mask | 割り込みマスクレジスタ K02                    |

|      |       |       |       |       | EIK01 | 0                  | Enable | Mask | 割り込みマスクレジスタ K01                    |

|      |       |       |       |       | EIK00 | 0                  | Enable | Mask | 割り込みマスクレジスタ K00                    |

| 0EDH | 0     | 0     | 0     | IK0   | 0     |                    |        |      | <sup>*5</sup>                      |

|      |       |       |       | R     | 0     |                    |        |      | <sup>*5</sup>                      |

|      |       |       |       |       | 0     |                    |        |      | <sup>*5</sup>                      |

|      |       |       |       |       | IK0   | 0                  | Yes    | No   | 割り込み要因フラグ(K00 ~ K03) <sup>*4</sup> |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

K00 ~ K03: 入力ポートデータ (0E0H)

入力ポート端子の入力データをこれらのレジスタから読み出すことができます。

- "1"読み出し: HIGHレベル

- "0"読み出し: LOWレベル

- 書き込み: 無効

入力ポート4ビット(K00 ~ K03)の端子電圧がそれぞれHIGH(VDD)レベルのときに"1"、LOW(Vss)レベルのときに"0"として読み出せます。

これらのレジスタは読み出し専用のため、書き込み動作は無効となります。

---

### EIK00～EIK03: 割り込みマスクレジスタ (0E8H)

入力割り込みのマスクを設定します。

- "1"書き込み: 割り込み許可

- "0"書き込み: 割り込みをマスク

- 読み出し: 可能

K00～K03の各ビットごとに、割り込みのマスクを設定できます。

イニシャルリセット時、これらのレジスタはすべて"0"(割り込みをマスク)に設定されます。

### IK0: 割り込み要因フラグ (0EDH D0)

入力割り込みの発生状態を示すフラグです。

- "1"読み出し: 割り込みあり

- "0"読み出し: 割り込みなし

- 書き込み: 無効

IK0はK00～K03に対応する割り込み要因フラグです。

このフラグを読み出すことによって、入力割り込みの有無を判断できます。なお、フラグは読み出し直後に"0"にリセットされます。

EI時、割り込み要因フラグの読み込みは可能ですが、以下の場合には注意が必要です。

読み込もうとする割り込み要因フラグに対応する割り込みマスクレジスタの値が"1"にセットされている(マスクされていない)場合、割り込み要因フラグが"1"にセットされるタイミングにより、CPUに対し割り込み要求を発生する場合と、割り込み要因フラグが読み込みによりクリアされ、割り込み要求が発生しない場合があります。

イニシャルリセット時、このフラグは"0"(割り込みなし)に設定されます。

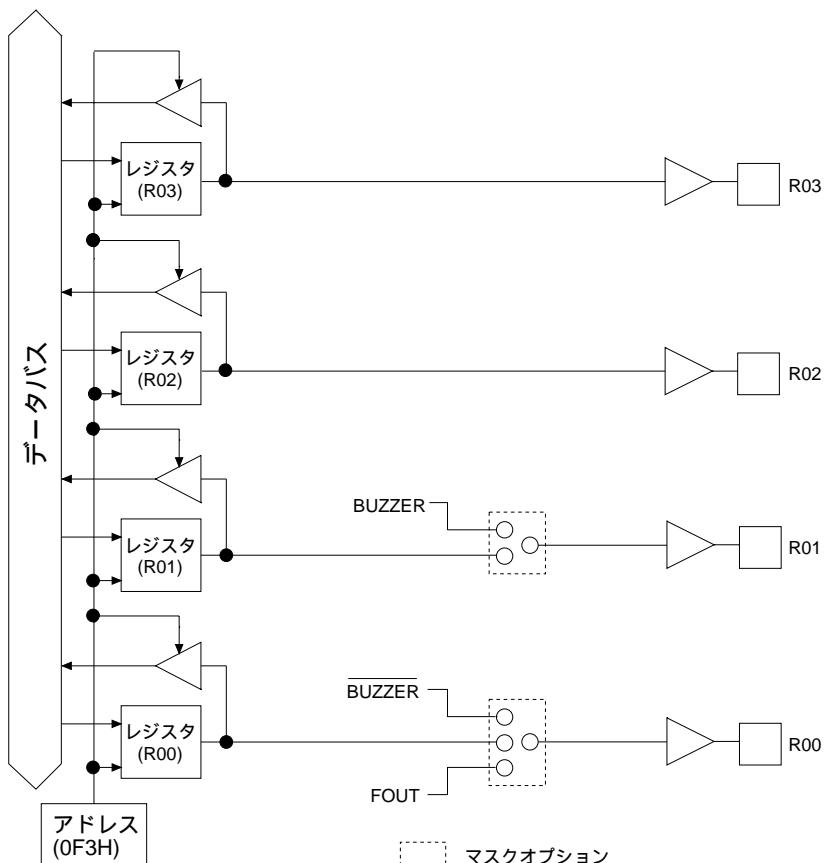

## 4.4 出力ポート (R00 ~ R03)

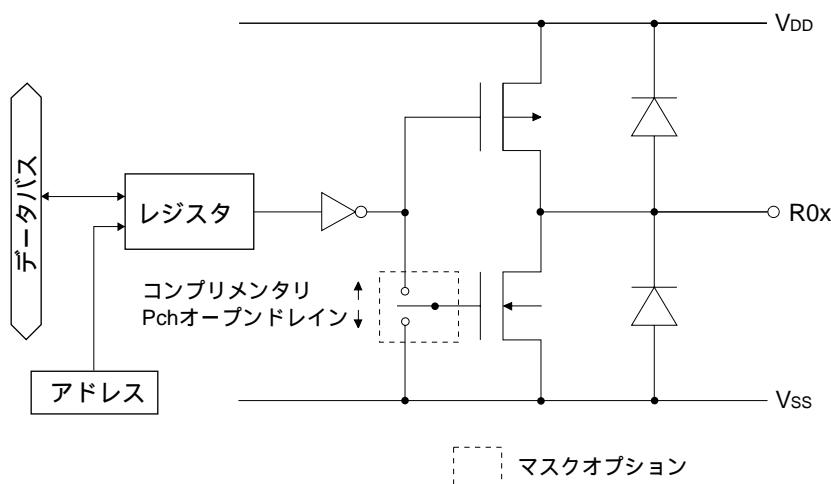

### 4.4.1 出力ポートの構成

S1C60N05シリーズは4ビットの出力ポートR00～R03を内蔵しています。

各出力ポートの出力仕様は、マスクオプションによりコンプリメンタリ出力、あるいはPチャンネルオーブンドレイン出力のいずれかを選択できます。

また、出力ポートR00およびR01はマスクオプションにより特殊出力ポートとしても使用できます。図4.4.1.1に出力ポートの構成を示します。

図4.4.1.1 出力ポートの構成

#### 4.4.2 マスクオプション

出力ポートはマスクオプションにより以下の選択が行えます。

##### (1) 出力ポートの出力仕様

出力ポート(R00～R03)の出力仕様は、4ビットのポート個々にコンプリメンタリ出力、あるいはPチャンネルオーブンドレイン出力のいずれかが選択できます。

ただし、Pチャンネルオーブンドレイン出力を選択した場合でも、出力ポートに電源電圧を越える電圧の印加は禁止します。

##### (2) 特殊出力

出力ポートR00およびR01は通常のDC出力の他に、表4.4.2.1に示す特殊出力を選択できます。

図4.4.2.1に出力ポートR00～R03の構造を示します。

表4.4.2.1 特殊出力

| レジスタ | 特殊出力選択時         |

|------|-----------------|

| R00  | FOUTまたはBUZZER出力 |

| R01  | BUZZER出力        |

図4.4.2.1 出力ポートR00～R03の構造

**FOUT (R00)**

出力ポートR00をFOUT出力に設定した場合、このポートはfosc(CPU動作クロック周波数)またはfoscを分周したクロックを出力します。クロックの周波数はF1～F4のそれぞれについて5種類から1つをマスクオプションで選択でき、ソフトウェアでF1～F4のいずれかを選択して使用します。選択できる周波数の種類は表4.4.2.2のとおりです。

表4.4.2.2 FOUTクロック周波数

| 設定値 | クロック周波数 (Hz)       |                    |                    |                    | fosc=32,768 |

|-----|--------------------|--------------------|--------------------|--------------------|-------------|

|     | F1                 | F2                 | F3                 | F4                 |             |

|     | (D1,D0)=(0,0)      | (D1,D0)=(0,1)      | (D1,D0)=(1,0)      | (D1,D0)=(1,1)      |             |

| 1   | 256<br>(fosc/128)  | 512<br>(fosc/64)   | 1,024<br>(fosc/32) | 2,048<br>(fosc/16) |             |

| 2   | 512<br>(fosc/64)   | 1,024<br>(fosc/32) | 2,048<br>(fosc/16) | 4,096<br>(fosc/8)  |             |

| 3   | 1,024<br>(fosc/32) | 2,048<br>(fosc/16) | 4,096<br>(fosc/8)  | 8,192<br>(fosc/4)  |             |

| 4   | 2,048<br>(fosc/16) | 4,096<br>(fosc/8)  | 8,192<br>(fosc/4)  | 16,384<br>(fosc/2) |             |

| 5   | 4,096<br>(fosc/8)  | 8,192<br>(fosc/4)  | 16,384<br>(fosc/2) | 32,768<br>(fosc/1) |             |

(D1, D0) = (XFOUT1, XFOUT0)

注: FOUT出力信号はON/OFF時にハザードを生じる可能性があります。

**BUZZER, BUZZER (R01, R00)**

出力ポートR01とR00はそれぞれをBUZZER出力、BUZZER出力(BUZZER反転出力)に設定でき、圧電ブザーのダイレクト駆動が可能です。

BUZZER出力(R00)は、R01をBUZZER出力にした場合のみ設定できます。この場合、BUZZER出力のON/OFFをR00レジスタで行うか、R01レジスタでBUZZER出力と同時に制御するかについてもマスクオプションで選択できます。

BUZZER出力の周波数は、2kHzまたは4kHzのいずれかをソフトウェアによって選択することができます。

注: BUZZER出力信号はON/OFF時にハザードを生じる可能性があります。

#### 4.4.3 出力ポートの制御

表4.4.3.1に出力ポートの制御レジスタを示します。

表4.4.3.1 I/Oメモリ(出力ポート)

| アドレス | レジスタ |     |        |        | Name   | Init *1 | 1    | 0    | 注釈                |  |

|------|------|-----|--------|--------|--------|---------|------|------|-------------------|--|

|      | D3   | D2  | D1     | D0     |        |         |      |      |                   |  |

| 0F3H | R03  | R02 | R01    | R00    | R03    | 0       | High | Low  | 出力ポートデータ R03      |  |

|      |      |     | BUZZER | FOUT   | R02    | 0       | High | Low  | 出力ポートデータ R02      |  |

|      |      |     |        |        | R01    | 0       | High | Low  | 出力ポートデータ R01      |  |

|      | R/W  |     |        |        | BUZZER | 0       | On   | Off  | ブザー On/Off 制御レジスタ |  |

|      |      |     |        |        | R00    | 0       | High | Low  | 出力ポートデータ R00      |  |

|      |      |     |        |        | FOUT   | 0       | On   | Off  | 周波数出力制御レジスタ       |  |

| 0FDH | XBZR | 0   | XFOUT1 | XFOUT0 | XBZR   | 0       | 2kHz | 4kHz | ブザー周波数制御          |  |

|      |      | R/W | R      | R/W    | XFOUT1 | 0       |      |      | *5                |  |

|      |      |     |        |        | XFOUT0 | 0       |      |      | FOUT周波数制御 *6      |  |

|      |      |     |        |        |        |         |      |      | FOUT周波数制御 *6      |  |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

R00～R03: 出力ポートデータ (0F3H)

各出力ポートの出力データを設定します。

"1"書き込み: HIGHレベル

"0"書き込み: LOWレベル

読み出し: 可能

出力ポート端子は対応するレジスタ(R00～R03)に書き込まれたデータを出力します。レジスタに "1"を書き込んだ場合は出力ポート端子はHIGH(VDD)レベルになり、"0"を書き込んだ場合はLOW(Vss)レベルになります。

イニシャルリセット時、これらのレジスタはすべて"0"になります。

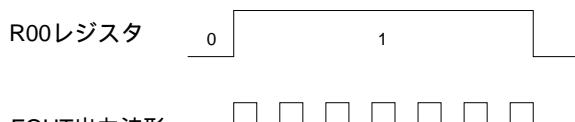

R00 (FOUT選択時): 特殊出力データ (0F3H D0)

FOUT(クロック)出力を制御します。

"1"書き込み: クロック出力

"0"書き込み: LOWレベル(DC)出力

読み出し: 可能

R00レジスタへのデータ書き込みにより、FOUT出力を制御できます。

イニシャルリセット時、このレジスタは"0"に設定されます。

図4.4.3.1にFOUT出力波形を示します。

図4.4.3.1 FOUT出力波形

XFOUT0, XFOUT1: FOUT周波数制御 (0FDH D0, 0FDH D1)

R00ポートをFOUT出力に設定した場合の出力周波数を選択します。

表4.4.3.2 FOUT周波数の選択

| XFOUT1 | XFOUT0 | 選択周波数 |

|--------|--------|-------|

| 0      | 0      | F1    |

| 0      | 1      | F2    |

| 1      | 0      | F3    |

| 1      | 1      | F4    |

イニシャルリセット時、これらのレジスタは"0"に設定されます。

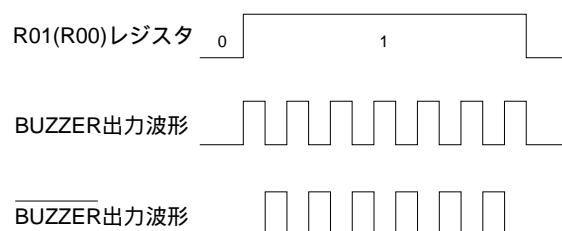

R00, R01 (BUZZER, BUZZER選択時): 特殊出力データ (0F3H D0, 0F3H D1)

BUZZER、BUZZER(ブザー)出力を制御します。

- "1"書き込み: ブザー出力

- "0"書き込み: LOWレベル(DC)出力

- 読み出し: 可能

R00レジスタおよびR01レジスタへのデータ書き込みにより、BUZZER出力、BUZZER出力を制御できます。

マスクオプションによりBUZZER出力をR01レジスタ制御に設定した場合はR01レジスタへのデータ書き込みにより、BUZZER出力とBUZZER出力の双方を同時に制御できます。

イニシャルリセット時、これらのレジスタは"0"に設定されます。

図4.4.3.2にブザー出力波形を示します。

図4.4.3.2 BUZZER出力波形

XBZR: ブザー周波数制御 (0FDH D3)

ブザー周波数を選択します。

- "1"書き込み: 2kHz

- "0"書き込み: 4kHz

- 読み出し: 可能

R00、R01ポートをブザー出力に設定した場合に、ブザー周波数の選択を行います。レジスタに"1"を書き込むと2kHz、"0"を書き込むと4kHzに設定されます。

イニシャルリセット時、このレジスタは"0"に設定されます。

## 4.5 入出力兼用ポート(P00～P03)

### 4.5.1 入出力兼用ポートの構成

S1C60N05シリーズは4ビットの汎用入出力兼用ポートを内蔵しています。

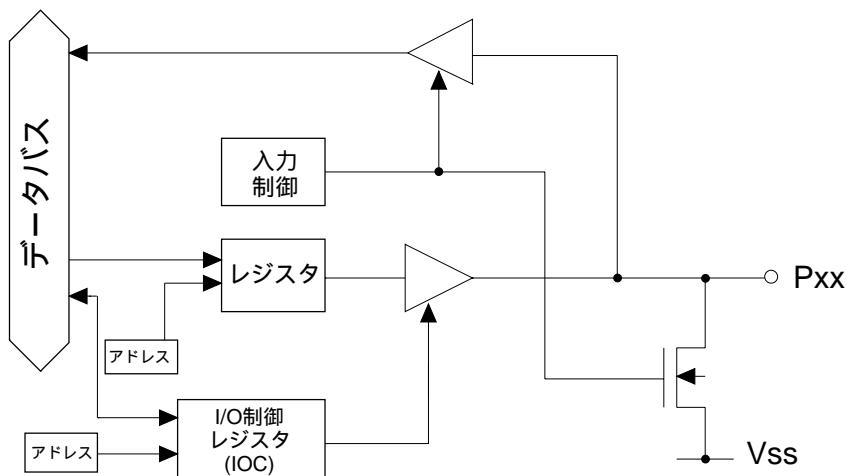

図4.5.1.1に入出力兼用ポートの構成を示します。

入出力兼用ポート(P00～P03)の4ビットは、I/Oコントロールレジスタ(IOC)にデータを書き込むことによって入力モードまたは出力モードに設定できます。

図4.5.1.1 入出力兼用ポートの構成

### 4.5.2 I/Oコントロールレジスタと入力/出力モード

入出力兼用ポートP00～P03はI/OコントロールレジスタIOCにデータを書き込むことにより、入力モードあるいは出力モードに設定されます。

入力モードに設定する場合はIOCに"0"を書き込みます。

入力モードに設定された入出力兼用ポートは、ハイインピーダンス状態となり入力ポートとして働きます。ただし、入力データの読み込み時は入力ラインがプルダウンされます。

出力モードに設定する場合はIOCに"1"を書き込みます。

出力モードに設定された入出力兼用ポートは出力ポートとして働き、レジスタへの書き込みデータが"1"のときにHIGH(VDD)レベル、"0"のときにLOW(Vss)レベルの出力を行います。

イニシャルリセット時、I/OコントロールレジスタIOCは"0"に設定され、入出力兼用ポートは入力モードになります。

### 4.5.3 マスクオプション

入出力兼用ポートは出力モード時(IOC="1")の出力仕様としてコンプリメンタリ出力、またはPチャンネルオープンドレイン出力のいずれかを選択することができます。この選択はポートの1ビットごとに行えます。

ただし、Pチャンネルオープンドレイン出力を選択した場合でも、ポートに電源電圧を越える電圧を印加することは禁止します。

### 4.5.4 入出力兼用ポートの制御

表4.5.4.1に入出力兼用ポートの制御レジスタを示します。

表4.5.4.1 I/Oメモリ(入出力兼用ポート)

| アドレス | レジスタ |     |     |     | Name | Init *1 | 1    | 0   | 注釈                |

|------|------|-----|-----|-----|------|---------|------|-----|-------------------|

|      | D3   | D2  | D1  | D0  |      |         |      |     |                   |

| 0F4H | P03  | P02 | P01 | P00 | P03  | - *2    | High | Low | 入出力ポートデータ P03     |

|      |      |     |     |     | P02  | - *2    | High | Low | 入出力ポートデータ P02     |

|      | R/W  |     |     |     | P01  | - *2    | High | Low | 入出力ポートデータ P01     |

|      |      |     |     |     | P00  | - *2    | High | Low | 入出力ポートデータ P00     |

| 0FCH | 0    | 0   | 0   | IOC | 0    |         |      |     | *5                |

|      |      |     |     |     | 0    |         |      |     | *5                |

|      | R    |     | R/W |     | IOC  | 0       | Out  | In  | 入出力 In/Out 制御レジスタ |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

P00～P03: 入出力兼用ポートデータ (0F4H)

入出力兼用ポートデータの読み出し、および出力データの設定を行います。

- データ書き込み時

"1"書き込み: HIGHレベル

"0"書き込み: LOWレベル

入出力兼用ポートが出力モードに設定されている場合、このレジスタに書き込んだデータがそのまま入出力兼用ポート端子に出力されます。ポートデータとして"1"を書き込んだ場合はポート端子はHIGH(VDD)レベルになり、"0"を書き込んだ場合はLOW(Vss)レベルになります。

なお、入力モードの場合もポートデータの書き込みは行えます。

- データ読み出し時

- "1"読み出し: HIGHレベル

"0"読み出し: LOWレベル

入出力兼用ポートの端子電圧レベルを読み出します。入出力兼用ポートが入力モードの場合はポート端子に入力されている電圧レベルが読み出され、出力モードに設定されている場合は出力電圧レベルが読み出されます。端子電圧がHIGH(VDD)レベルの場合は読み出されるポートデータが"1"、LOW(Vss)レベルの場合は"0"となります。

また、読み出し時は内蔵プルダウン抵抗がONとなり、入出力兼用ポート端子がプルダウンされます。

- 注:

- 入出力兼用ポートが出力モードに設定され、ポート端子に低インピーダンスの負荷が接続されている場合、レジスタに書き込んだデータと読み出したデータが異なることがあります。

- 入出力兼用ポートが入力モードに設定され、入力が内蔵プルダウンによりHIGH(VDD)からLOW(Vss)に変化した場合、入力ラインの容量性負荷と内蔵プルダウン抵抗との時定数により誤入力となる場合があります。端子の電位がCPUシステムクロックの0.5周期以内に定まらない場合は、プルダウン抵抗を外部に設けるか、複数回の読み出しを行うなどの対策が必要です。

#### IOC: I/Oコントロールレジスタ (0FCH D0)

入出力兼用ポートの入力/出力モードを設定します。

- "1"書き込み: 出力モード

"0"書き込み: 入力モード

読み出し: 可能

IOCに"1"を書き込むことにより入出力兼用ポートの全ビットが出力モードに、"0"を書き込むことにより入力モードになります。

イニシャルリセット時、このレジスタは"0"(入力モード)に設定されます。

## 4.6 LCD ドライバ (COM0 ~ COM3, SEG0 ~ SEG19)

### 4.6.1 LCD ドライバの構成

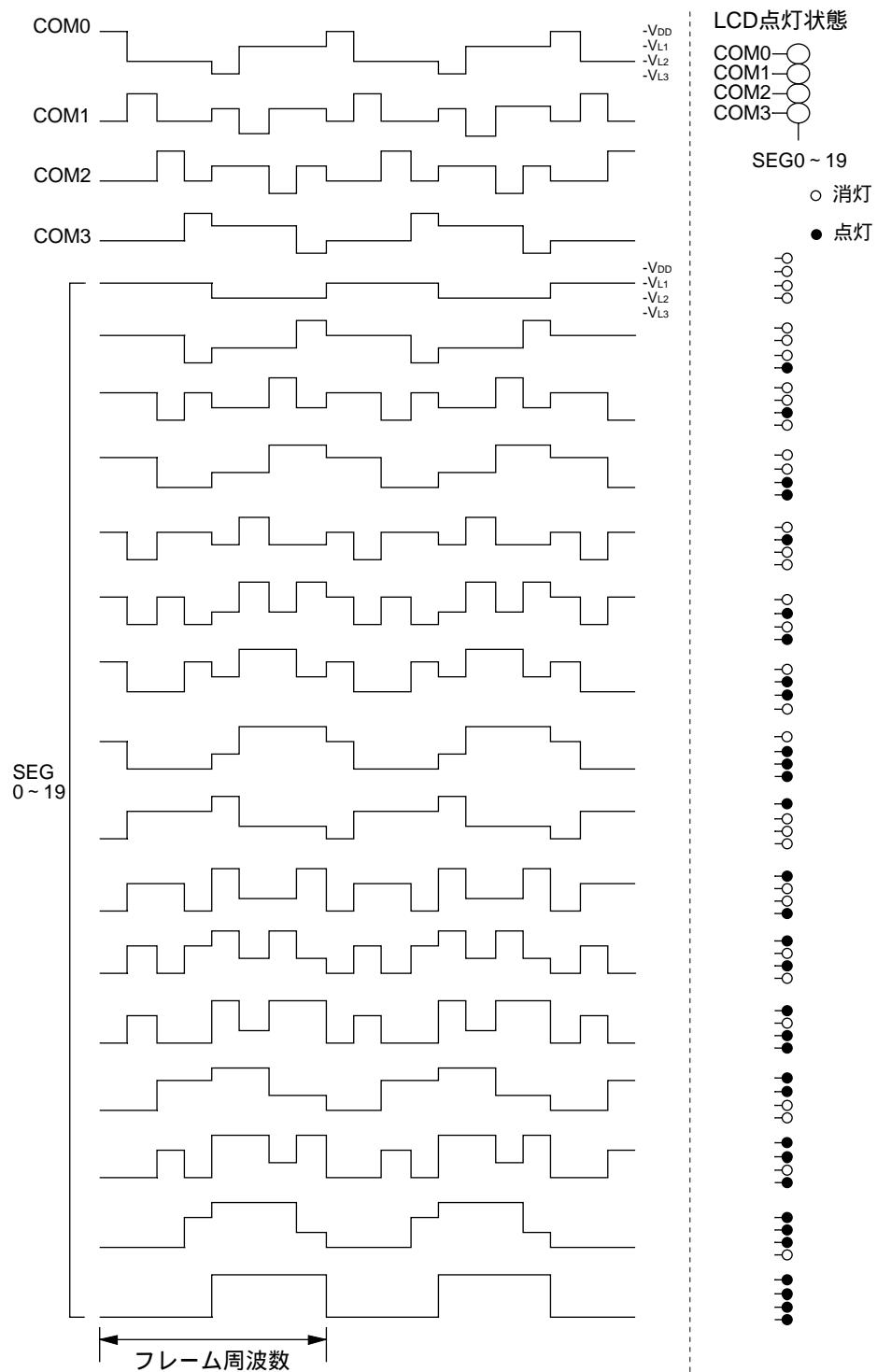

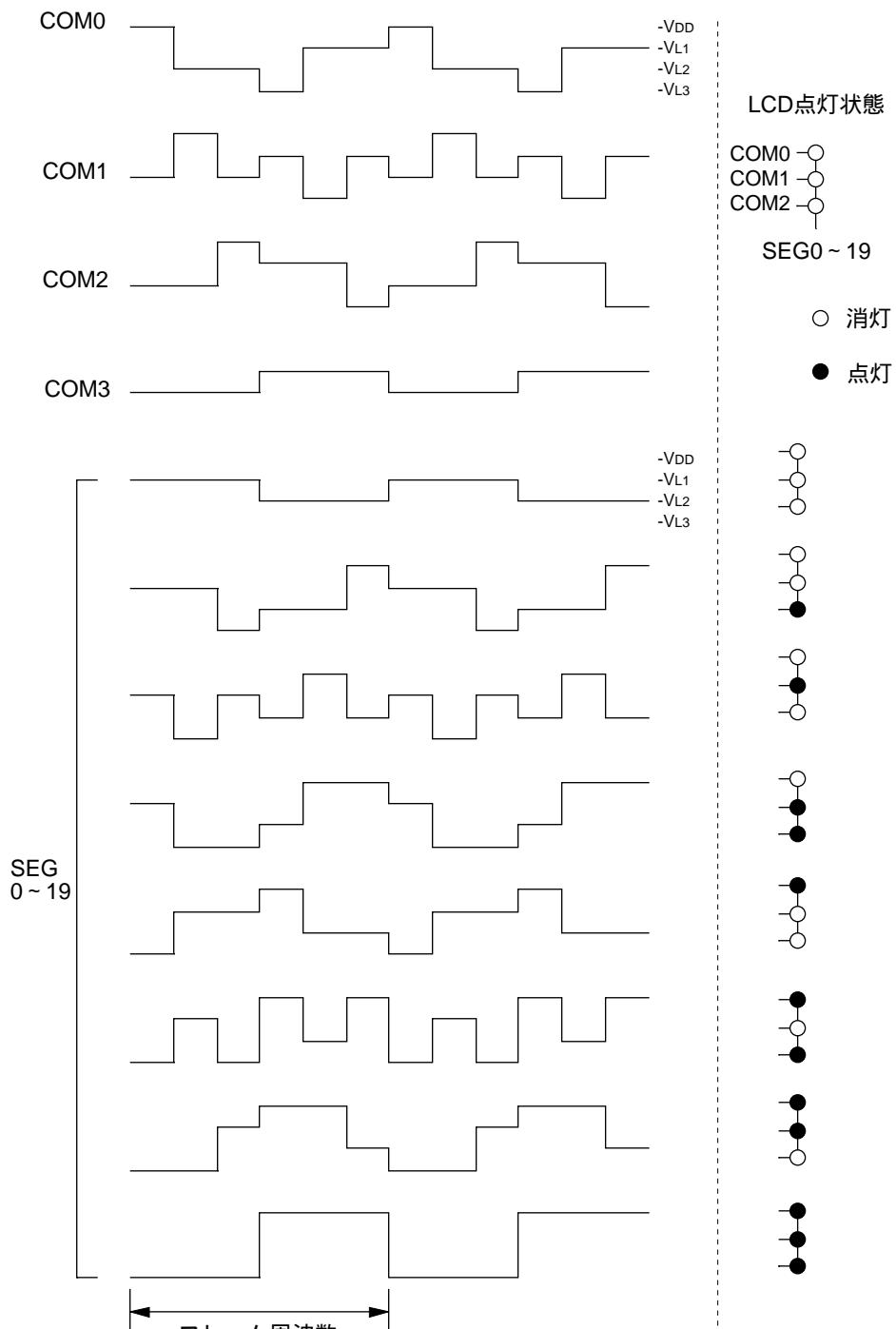

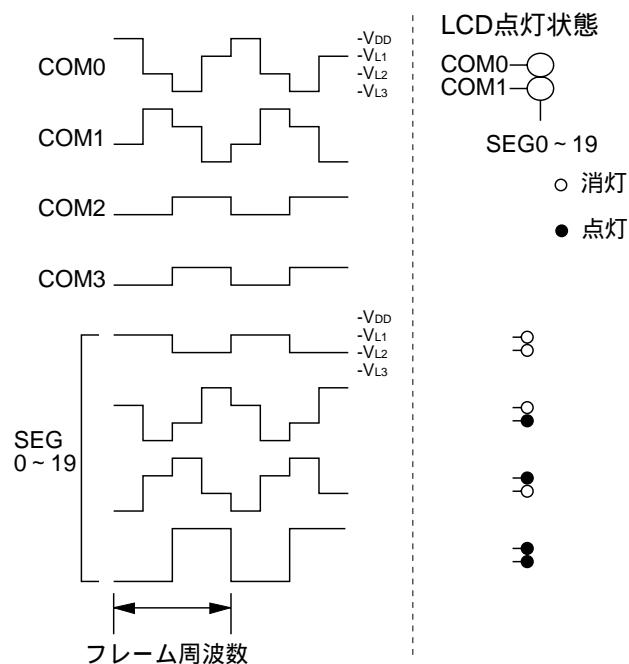

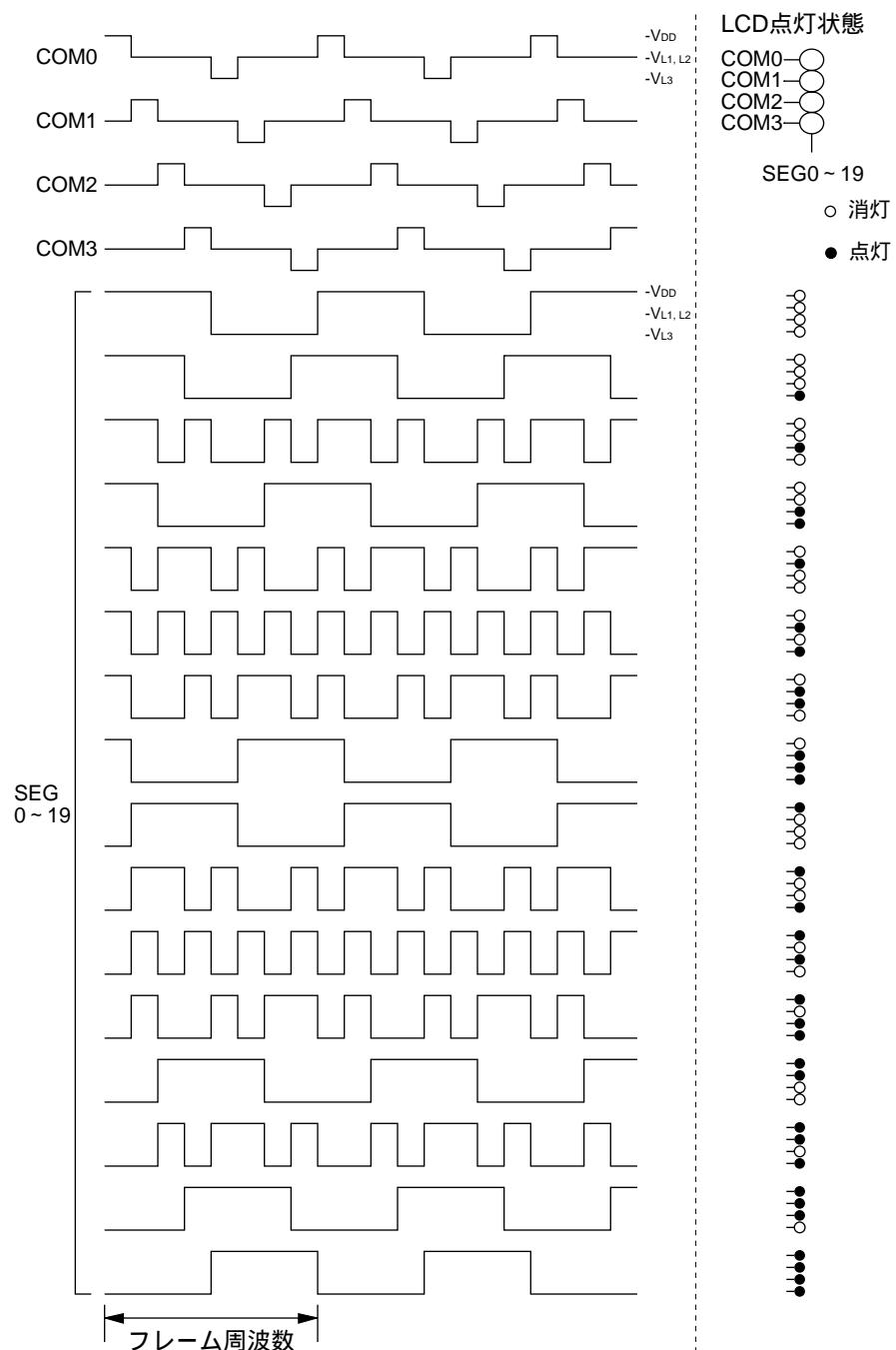

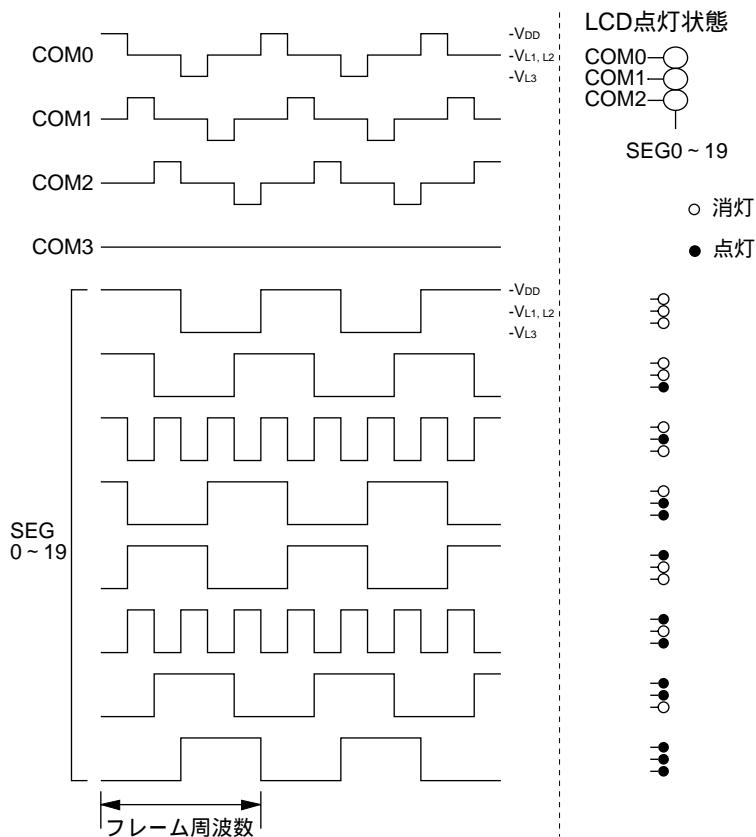

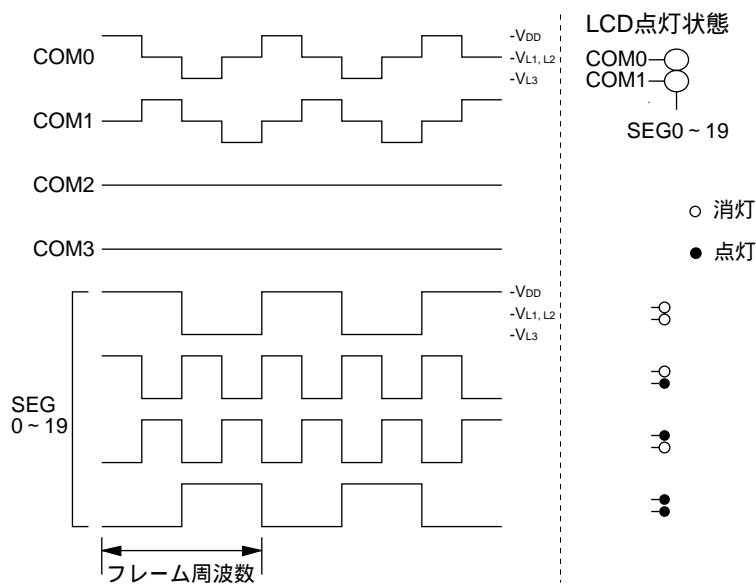

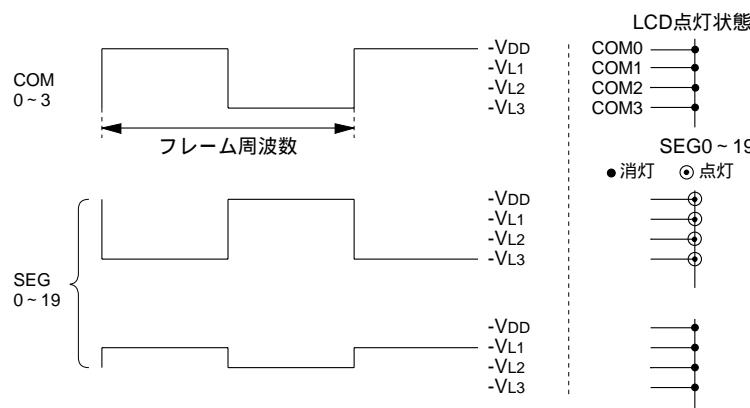

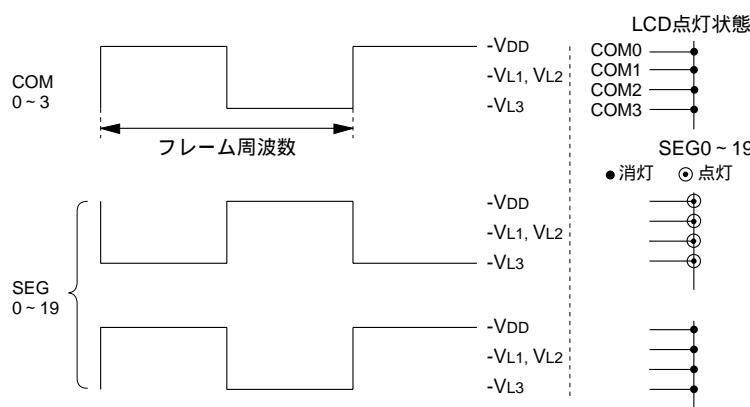

S1C60N05シリーズは4本のコモン端子(COM0 ~ COM3)と20本のセグメント端子(SEG0 ~ SEG19)を持ち、最大80( $20 \times 4$ )セグメントのLCDを駆動できます。

LCD駆動用電源はCPUの内部回路により発生するため、外部から特別に与える必要はありません。駆動方式はV<sub>DD</sub>、V<sub>L1</sub>、V<sub>L2</sub>、V<sub>L3</sub>の4電位(1/3バイアス)による1/4デューティ(マスクオプションで1/3、1/2デューティも可)ダイナミック駆動です。また、マスクオプションにより、V<sub>DD</sub>、V<sub>L1</sub>=V<sub>L2</sub>、V<sub>L3</sub>の3電位(1/2バイアス)による1/4デューティ(マスクオプションで1/3、1/2デューティも可)ダイナミック駆動も選択できます。

1/2バイアス選択は、LCD系定電圧回路を使用しない場合にのみ有効で、V<sub>L1</sub>端子とV<sub>L2</sub>端子をIC外部にて接続してください。

フレーム周波数は1/4デューティのとき32Hz、1/3デューティのとき42.7Hz、1/2デューティのとき32Hzになります(fosc=32.768kHz)。

図4.6.1.1に1/4デューティ(1/3バイアス)、図4.6.1.2に1/3デューティ(1/3バイアス)、

図4.6.1.3に1/2デューティ(1/3バイアス)、図4.6.1.4に1/4デューティ(1/2バイアス)、

図4.6.1.5に1/3デューティ(1/2バイアス)、図4.6.1.6に1/2デューティ(1/2バイアス)の駆動波形を示します。

注: foscは発振回路の発振周波数を示します。

図4.6.1.1 1/4デューティの駆動波形 (1/3バイアス)

図4.6.1.2 1/3デューティの駆動波形 (1/3バイアス)

図4.6.1.3 1/2デューティの駆動波形 (1/3バイアス)

図4.6.1.4 1/4デューティの駆動波形 (1/2バイアス)

図4.6.1.5 1/3デューティの駆動波形(1/2バイアス)

図4.6.1.6 1/2デューティの駆動波形(1/2バイアス)

#### 4.6.2 発振周波数の歩度調整

S1C60N05シリーズはソフトウェアによりLCD駆動デューティを1/1デューティに設定できます。この機能により、発振回路の発振周波数を簡単に調整(歩度調整)できます。

LCD駆動を1/1デューティに設定する手順は以下のとおりです。

- ① アドレス"0FBH D3"のレジスタCSDCに"1"を書き込みます。

- ② 表示メモリのCOM0～COM3に対応するレジスタにはすべて同一の値を書き込みます。

フレーム周波数は32Hz(fosc1/1,024、fosc1=32.768kHzのとき)となります。

- 注:

- マスクオプションにて1/3、1/2デューティを選択している場合でも、ソフトウェアで1/1デューティ駆動にすると全てのCOMが有効になります。そのため、1/1デューティ駆動の場合、1/3、1/2デューティを選択してもCOM0～COM3に対応する全ての表示メモリに同じ値を設定してください。

- 歩度調整時はLCDが全点灯となるようにCOM0～COM3に対応する全ての表示データをセットしてください。

図4.6.2.1に1/1デューティ駆動波形(1/3バイアス)、図4.6.2.2に1/1デューティ駆動波形(1/2バイアス)を示します。

図4.6.2.1 1/1デューティ駆動波形 (1/3バイアス)

図4.6.2.2 1/1デューティ駆動波形 (1/2バイアス)

### 4.6.3 マスクオプション

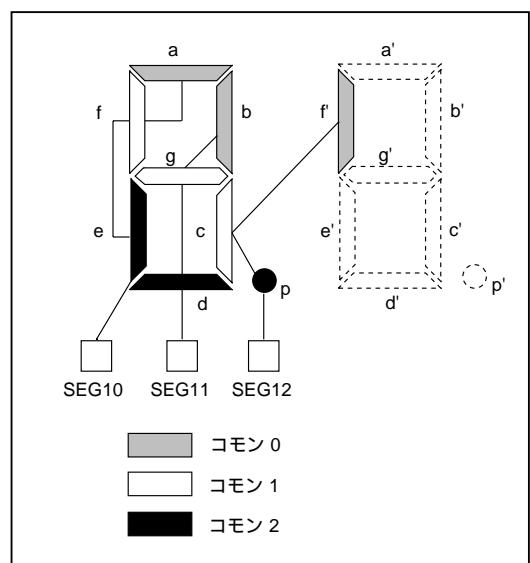

#### (1) セグメント割り付け

S1C60N05シリーズのセグメントデータは、図4.1.1に示すようにメモリ空間上アドレス"090H ~ 0AFH"の表示メモリに表示データを書き込むことにより決定されます。

表示メモリのアドレスおよびビットは、マスクオプションにより任意のセグメント端子(SEG0 ~ SEG19)に対応させることができます。このため、液晶パネルの自由度が増し設計が容易になります。

図4.6.3.1にLCDセグメント(パネル上)と表示メモリの関係を1/3デューティの場合を例として示します。

| アドレス | データ |    |    |    |

|------|-----|----|----|----|

|      | D3  | D2 | D1 | D0 |

| 09AH | d   | c  | b  | a  |

| 09BH | p   | g  | f  | e  |

| 09CH | d'  | c' | b' | a' |

| 09DH | p'  | g' | f' | e' |

表示メモリ割り付け表

|       | コモン 0          | コモン 1         | コモン 2         |

|-------|----------------|---------------|---------------|

| SEG10 | 9A, D0<br>(a)  | 9B, D1<br>(f) | 9B, D0<br>(e) |

| SEG11 | 9A, D1<br>(b)  | 9B, D2<br>(g) | 9A, D3<br>(d) |

| SEG12 | 9D, D1<br>(f') | 9A, D2<br>(c) | 9B, D3<br>(p) |

端子アドレス割り付け表

図4.6.3.1 セグメント割り付け

## (2) 駆動デューティ

LCDの駆動デューティとして1/4デューティ、1/3デューティまたは1/2デューティをマスクオプションで選択します。

表4.6.3.1に選択デューティによるセグメント数等の差異を示します。

表4.6.3.1 選択デューティによる差異

| デューティ | 使用コモン端子  | 最大セグメント数    | フレーム周波数 (fosc=32kHzの場合) |

|-------|----------|-------------|-------------------------|

| 1/4   | COM0 ~ 3 | 80 (20 × 4) | 32Hz                    |

| 1/3   | COM0 ~ 2 | 60 (20 × 3) | 42.7Hz                  |

| 1/2   | COM0 ~ 1 | 40 (20 × 2) | 32Hz                    |

## (3) 出力仕様

- ① 各セグメント端子(SEG0 ~ SEG19)は2端子単位でセグメント信号出力かDC出力(VDD、VSSの2値出力)をマスクオプションで選択します。

DC出力を選択した場合は各セグメント端子のCOM0に対応するデータが出力されます。

- ② DC出力を選択した場合、コンプリメンタリ出力かPチャンネルオーブンドレイン出力を各端子ごとにマスクオプションで選択できます。

注: 2端子単位とはSEG(2・n)、SEG(2・n+1) (nは0 ~ 9の整数)の組合せです。

## (4) 駆動バイアス

LCDの駆動バイアスとして1/3バイアス、1/2バイアスをマスクオプションで選択します。

#### 4.6.4 LCD ドライバの制御

表4.6.4.1にLCD ドライバの制御レジスタを、図4.6.4.1に表示メモリマップを示します。

表4.6.4.1 I/Oメモリ (LCD ドライバ)

| アドレス | レジスタ |    |    |    | Name | Init <sup>*1</sup> | 1      | 0       | 注釈              |

|------|------|----|----|----|------|--------------------|--------|---------|-----------------|

|      | D3   | D2 | D1 | D0 |      |                    |        |         |                 |

| 0FBH | CSDC | 0  | 0  | 0  | CSDC | 0                  | Static | Dynamic | LCD駆動切り換え<br>*5 |

|      | R/W  | R  |    |    | 0    |                    |        |         | *5              |

|      |      |    |    |    | 0    |                    |        |         | *5              |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

|      |                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|------|------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| アドレス | 0                            | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 090  | 表示メモリ (書き込み専用)<br>32ワード×4ビット |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0A0  |                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

図4.6.4.1 表示メモリマップ

CSDC: LCD駆動切り換え (0FBH D3)

LCDの駆動方式を選択します。

"1"書き込み: スタティック駆動

"0"書き込み: ダイナミック駆動

読み出し: 可能

イニシャルリセット時はダイナミック駆動(CSDC="0")が選択されます。

表示メモリ (090H ~ 0AFH)

LCDセグメントを点灯/消灯させます。

"1"書き込み: 点灯

"0"書き込み: 消灯

読み出し: 不可

LCDセグメント(パネル上)を割り付けた表示メモリにデータを書き込むことにより、セグメントの点灯/消灯を行います。

イニシャルリセット時の表示メモリの内容は不定です。

## 4.7 計時タイマ

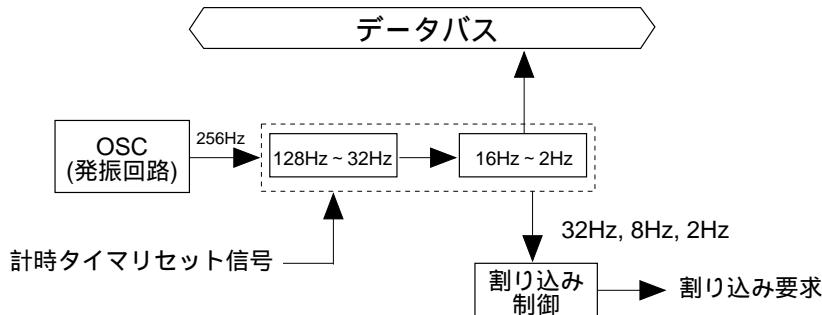

### 4.7.1 計時タイマの構成

S1C60N05シリーズは発振回路を原振とする計時タイマを内蔵しています。計時タイマは発振回路より出力される256Hz信号を入力クロックとする7ビットのバイナリカウンタで構成され、そのうち上位4ビット(16Hz ~ 2Hz)のデータをソフトウェアによって読み出すことができます。

図4.7.1.1に計時タイマの構成を示します。

図4.7.1.1 計時タイマの構成

通常は、この計時タイマを時計などのような各種の計時機能に用います。

### 4.7.2 割り込み機能

計時タイマは32Hz、8Hz、2Hzの各信号の立下りエッジにおいて割り込みを発生させることができます。

また、これらの割り込みに対して個別に割り込みをマスクするかしないかを、ソフトウェアで設定することができます。

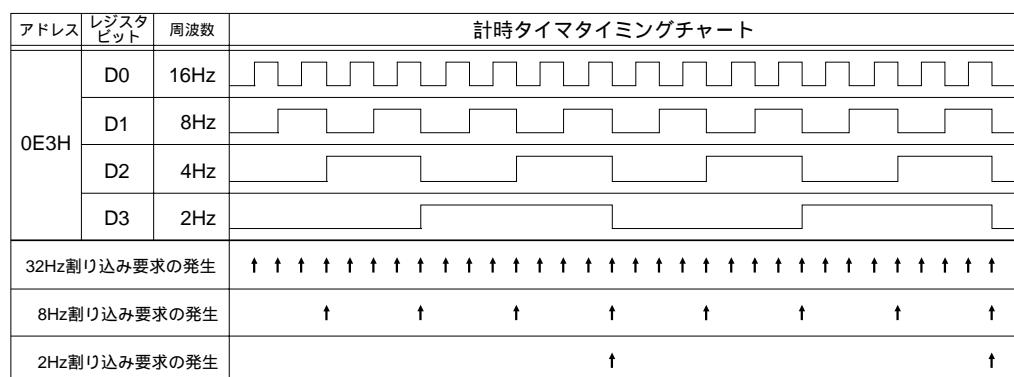

図4.7.2.1に計時タイマのタイミングチャートを示します。

図4.7.2.1 計時タイマのタイミングチャート

図4.7.2.1に示すとおり、割り込みは各周波数(32Hz、8Hz、2Hz)の信号の立下りエッジによって発生します。この時点で対応する割り込み要因フラグ(IT32、IT8、IT2)が"1"にセットされます。

また、各割り込みは割り込みマスクレジスタ(EIT32、EIT8、EIT2)によって個別にマスクを選択することができます。ただし、割り込み要因フラグは割り込みマスクレジスタの設定にかかわらず、対応する信号の立下りエッジで"1"にセットされます。たとえば、EIT2を"0"(マスク)に設定した場合でも、2Hz信号の立下りエッジによって割り込み要因フラグIT2が"1"にセットされます。

注: 割り込みマスクレジスタ(EIT32、EIT8、EIT2)への書き込みは、必ずDI(割り込みフラグ="0")状態時に行ってください。EI(割り込みフラグ="1")状態時に行うと誤動作の原因となります。

### 4.7.3 計時タイマの制御

表4.7.3.1に計時タイマの制御レジスタを示します。

表4.7.3.1 I/Oメモリ (計時タイマ)

| アドレス | レジスタ |      |      |       | Name  | Init <sup>*1</sup> | 注釈     |      |                                    |

|------|------|------|------|-------|-------|--------------------|--------|------|------------------------------------|

|      | D3   | D2   | D1   | D0    |       |                    | 1      | 0    |                                    |

| 0E3H | TM3  | TM2  | TM1  | TM0   | TM3   | - *3               | High   | Low  | 計時タイマデータ 2Hz                       |

|      |      |      |      |       | TM2   | - *3               | High   | Low  | 計時タイマデータ 4Hz                       |

|      | R    |      |      |       | TM1   | - *3               | High   | Low  | 計時タイマデータ 8Hz                       |

|      |      |      |      |       | TM0   | - *3               | High   | Low  | 計時タイマデータ 16Hz                      |

| 0EBH | 0    | EIT2 | EIT8 | EIT32 | 0     | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 2Hz <sup>*5</sup> |

|      | R    | R/W  |      |       | EIT2  | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 8Hz               |

|      |      |      |      |       | EIT8  | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 32Hz              |

| 0EFH | 0    | IT2  | IT8  | IT32  | 0     | 0                  | Yes    | No   | 割り込み要因フラグ(タイマ) 2Hz <sup>*5</sup>   |

|      | R    |      |      |       | IT2   | 0                  | Yes    | No   | 割り込み要因フラグ(タイマ) 8Hz <sup>*4</sup>   |

|      |      |      |      |       | IT8   | 0                  | Yes    | No   | 割り込み要因フラグ(タイマ) 32Hz <sup>*4</sup>  |

| 0F9H | 0    | 0    | 0    | TMRST | 0     |                    |        |      |                                    |

|      | R    |      |      |       | 0     |                    |        |      |                                    |

|      |      |      |      |       | 0     |                    |        |      |                                    |

|      |      |      |      |       | TMRST | Reset              | Reset  | -    | 計時タイマリセット <sup>*5</sup>            |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

#### TM0～TM3: タイマデータ (0E3H)

計時タイマの16Hz～2Hzのタイマデータが読み出せます。この4ビットは読み出し専用のため、書き込み動作は無効となります。

イニシャルリセット時、タイマデータは"0H"に初期化されます。

**EIT32, EIT8, EIT2: 割り込みマスクレジスタ (0EBH D0 ~ D2)**

計時タイマの割り込みについてマスクするかしないかを選択します。

- "1"書き込み: 割り込み許可

- "0"書き込み: 割り込みマスク

- 読み出し: 可能

割り込みマスクレジスタ(EIT32、EIT8、EIT2)によって、対応する各周波数(32Hz、8Hz、2Hz)の割り込みを個別にマスクするかしないか選択できます。

イニシャルリセット時、これらのレジスタはすべて"0"(マスク)に設定されます。

**IT32, IT8, IT2: 割り込み要因フラグ (0EFH D0 ~ D2)**

計時タイマ割り込みの発生状態を示すフラグです。

- "1"読み出し: 割り込みあり

- "0"読み出し: 割り込みなし

- 書き込み: 無効

割り込み要因フラグ(IT32、IT8、IT2)は、それぞれ各周波数(32Hz、8Hz、2Hz)の計時タイマ割り込みに対応します。これらのフラグによって、計時タイマ割り込みの有無をソフトウェアで判断することができます。なお、これらのフラグは割り込みをマスクしていても、対応する信号の立下りエッジで"1"にセットされます。

これらのフラグはソフトウェアで読み出すことによってリセットされます。

EI時、割り込み要因フラグの読み込みは可能ですが、以下の場合には注意が必要です。

読み込もうとする割り込み要因フラグに対応する割り込みマスクレジスタの値が"1"にセットされている(マスクされていない)場合、割り込み要因フラグが"1"にセットされるタイミングにより、CPUに対し割り込み要求を発生する場合と、割り込み要因フラグが読み込みによりクリアされ、割り込み要求が発生しない場合があります。

特に、同一アドレスに複数の割り込み要因フラグがある場合には、細心の注意が必要です。

イニシャルリセット時、これらのフラグはすべて"0"に設定されます。

**TMRST: 計時タイマリセット (0F9H D0)**

計時タイマをリセットします。

- "1"書き込み: 計時タイマリセット

- "0"書き込み: ノーオペレーション

- 読み出し: 常時"0"

計時タイマはTMRSTに"1"を書き込むことによりリセットされ、その直後リスタートします。

また、"0"の書き込みはノーオペレーションとなります。

このビットは書き込み専用のため、読み出し時は常時"0"となります。

## 4.8 A/Dコンバータ

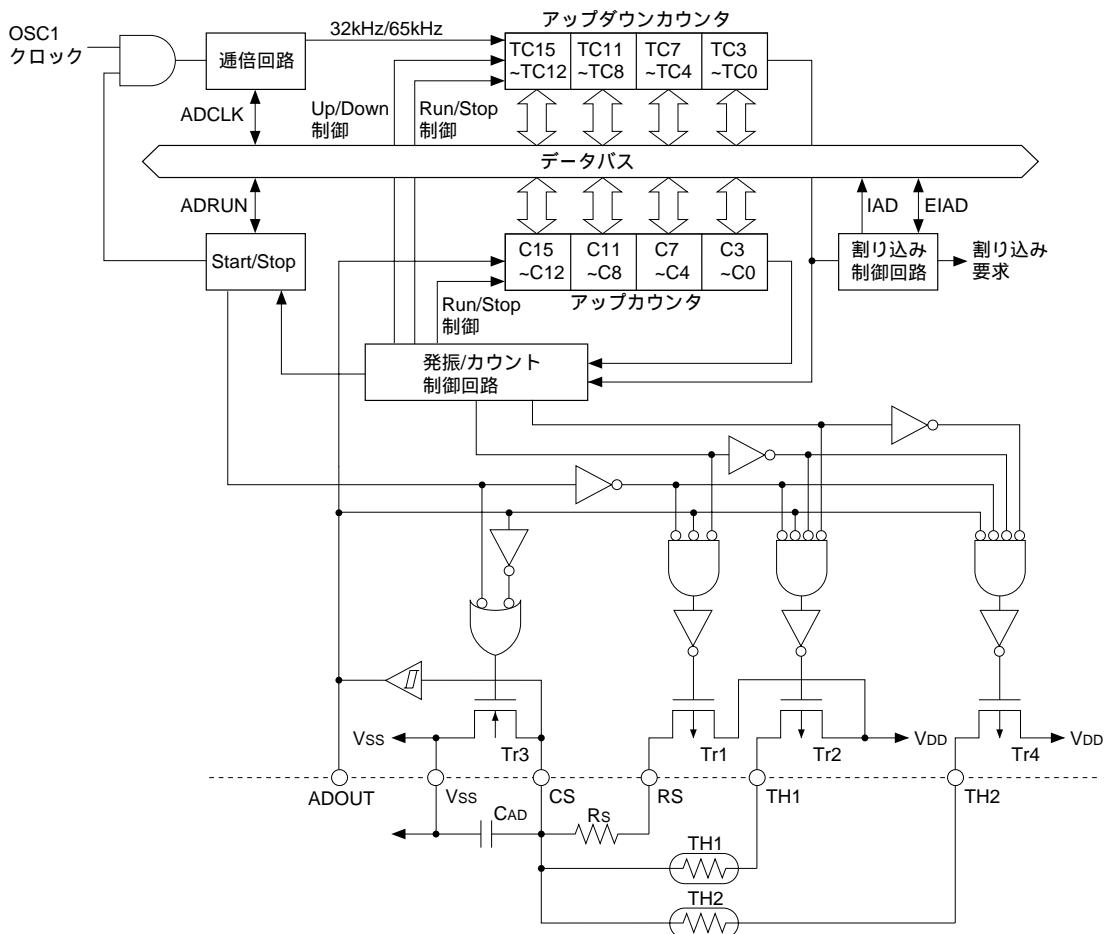

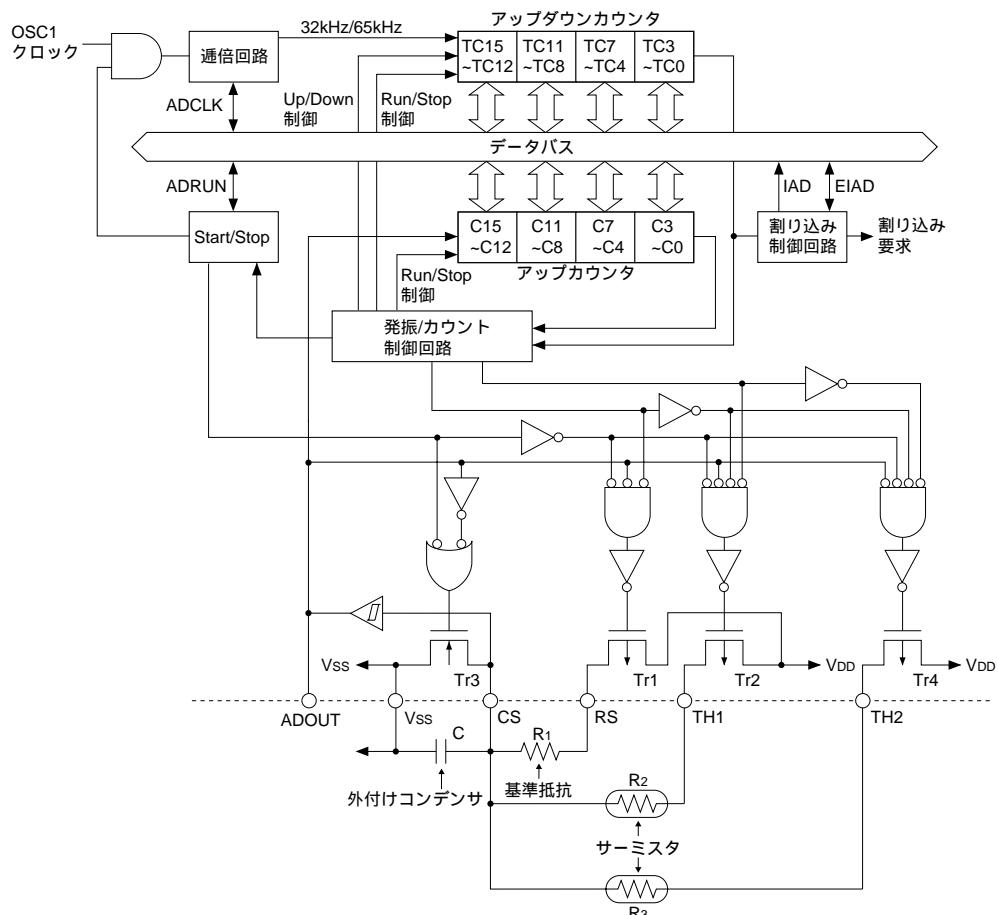

### 4.8.1 A/Dコンバータの構成

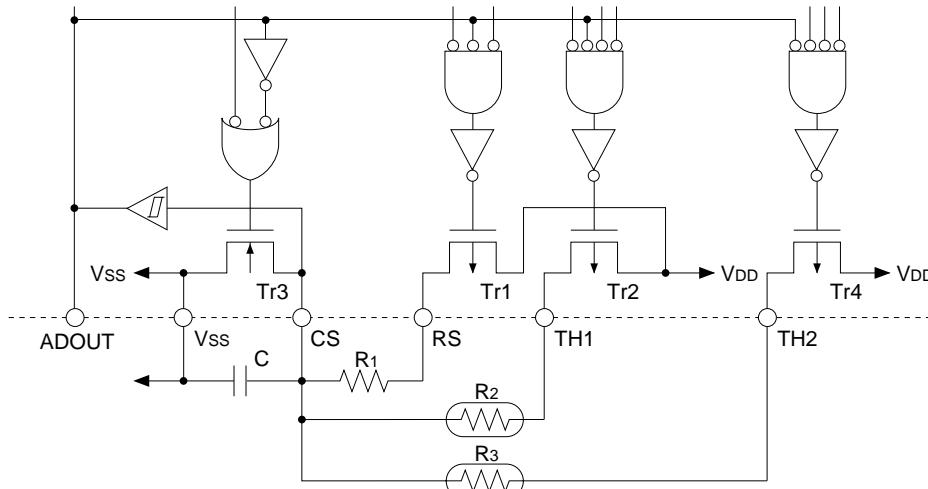

S1C60N05シリーズはCR発振方式のA/Dコンバータを2チャンネル内蔵しています。

このA/Dコンバータには2系統のCR発振回路とその発振周波数を計測するカウンタが設けられます。RS～CS端子間に温度などにより発振周波数がほとんど変化しない基準抵抗を、TH～CS端子間に温度などにより抵抗値が変化するセンサ等を接続して交互に発振させます。それぞれの発振周波数の差をカウント値の差として読み出すことができますので、たとえばサーミスタを利用した温度測定回路等の各種のセンサ回路が容易に実現できます。

図4.8.1.1にA/Dコンバータの構成を示します。

図4.8.1.1 A/Dコンバータの構成

発振入出力端子のRS～CS間には環境による抵抗値の変化がほとんどない基準抵抗を接続し、TH～CS間に抵抗値が変化するセンサ等を接続します。さらにCS～Vss間にコンデンサを接続することによりCR発振回路が構成されます。

#### 4.8.2 A/Dコンバータの動作

このA/Dコンバータは外部に接続した2個の抵抗それぞれによってCR発振を行い、その発振周波数をクロックとしてカウントを行います。それぞれの抵抗値の違いは発振周波数の違いとなってカウント値に現われますので、その差をプログラムで補正することにより抵抗値の変化による測定結果を得ることができます。

##### (1) 外部抵抗とコンデンサ

センサ(サーミスタ等の可変抵抗素子)をTH1/TH2端子～CS端子間に接続します。

ここで測定する内容の基準となる値(たとえば、温度測定の場合は基準温度)を設定し、その値におけるセンサの抵抗値と同じ値の基準抵抗をRS端子～CS端子間に接続します。なお、基準抵抗は温度など環境により変化しない素子を使用する必要があります。

CS端子～Vss端子間には基準抵抗とセンサのCR発振に共通に使用する発振用コンデンサを接続します。

##### (2) 発振回路

CR発振回路は、発振制御回路によって基準抵抗側とセンサ側が個別にどちらか一方だけが動作するようになっています。

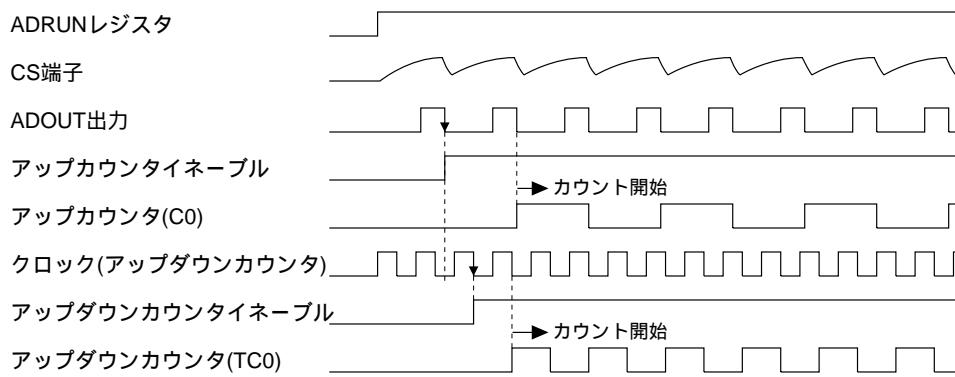

A/D変換はADRUNレジスタ(0F1H D0)に"1"を書き込むことにより開始し、発振回路も同時にONとなります。発振制御回路によってはじめに基準抵抗側(RS)の回路が動作し、その発振クロックによるカウントが終了した時点でセンサ側(TH1またはTH2)の回路に切り換わります。

TH1またはTH2はCHTHレジスタ(0F1H D3)によって選択されます。

それぞれの回路の発振動作はまったく同じで、次のようにになります。(例: CHTH="0"、 TH1が選択されている場合)

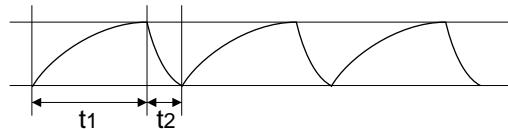

はじめにTr1(Tr2)がONになり、基準抵抗(センサ)を通してCS端子～Vss端子間に接続したコンデンサが充電されます。CS端子の電圧レベルが上がるとTr1(Tr2)がOFF、Tr3がONとなってコンデンサの電荷が放電され、CRの時定数による発振が行われます。

センサの抵抗値の変化によりこの時定数が変わり、基準抵抗の発振周波数と差が生じます。

発振波形はシュミットトリガにより整形されカウンタに送られます。このカウンタに送られるクロックはADOUT端子からも出力されますので、発振周波数をオシロスコープ等で確認することができます。このモニタは発振周波数に影響を与えませんので、CR発振周波数の調整等に利用できます。

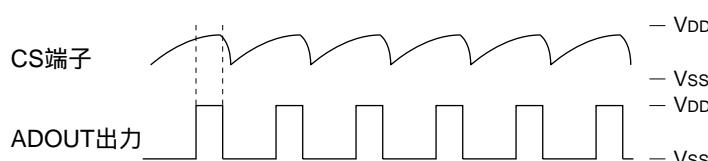

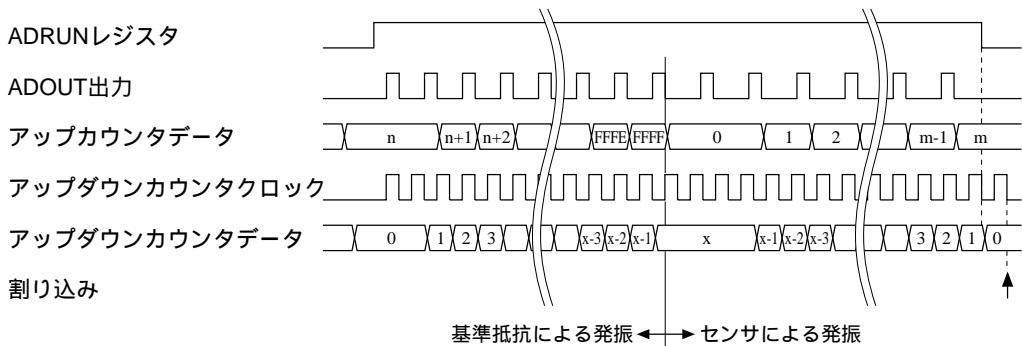

図4.8.2.1に発振波形とADOUTの出力波形を示します。

図4.8.2.1 発振波形

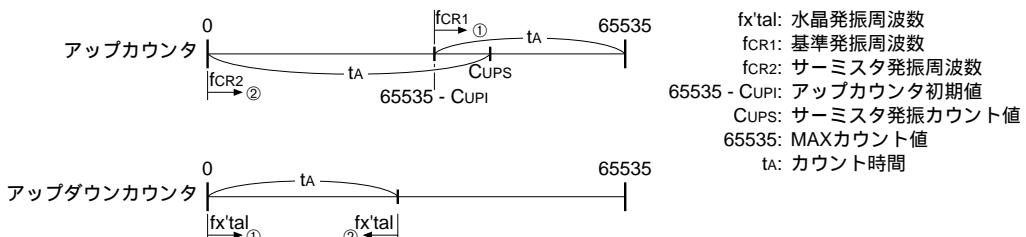

### (3) カウンタ

A/Dコンバータには2種類の16ビットカウンタが内蔵されています。1つは前記の発振クロックをカウントするアップカウンタC0～C15で、もう1つは内部クロックにより基準カウントを行うアップダウンカウンタTC0～TC15です。それぞれのカウンタは4ビット単位で読み出し、書き込みが可能です。

なお、アップダウンカウンタTC0～TC15の入力部には遅倍回路が設けられており、入力クロックとしてOSC1クロック(Typ. 32.768kHz)またはその遅倍クロック(Typ. 65.536kHz)のどちらか一方がソフトウェアにより選択できます。

ADRUNレジスタによりA/D変換を開始させると、はじめに基準抵抗による発振がONとなり、そのクロックによりアップカウンタC0～C15がアップカウントを行います。

これと同時にアップダウンカウンタTC0～TC15もカウントアップを開始します。

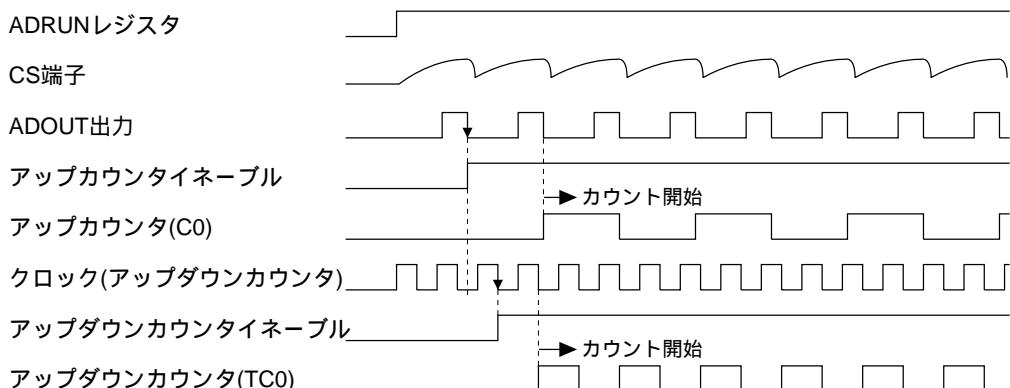

図4.8.2.2に発振開始とカウントアップ開始のタイミングを示します。

アップカウンタはCR発振開始後の最初のクロック立下りエッジでイネーブルとなり、次のクロックの立下りエッジからカウントアップを開始します。

アップダウンカウンタは最初のCR発振クロックの立下り直後に入力される内部クロック立下りエッジでイネーブルとなり、次の内部クロックの立下りエッジからカウントアップを開始します。

図4.8.2.2 カウントアップ開始タイミング

アップカウンタC0～C15がオーバーフローして"0000H"になると発振回路がセンサ側に切り換わり、今度はセンサ側の発振クロックによってカウントアップします。

アップダウンカウンタTC0～TC15はこの時点でダウンカウントに切り換わり、基準抵抗の発振によってカウントされた値から逆にカウントダウンします。

発振が切り換わった時点のカウントのタイミングは図4.8.2.2と同様です。

アップダウンカウンタTC0～TC15のカウントダウンが進み"0000H"になると、その時点で双方のカウンタのカウント動作とCR発振を停止し、割り込みを発生します。同時にADRUNレジスタが"0"に設定されA/Dコンバータの回路がすべて停止します。

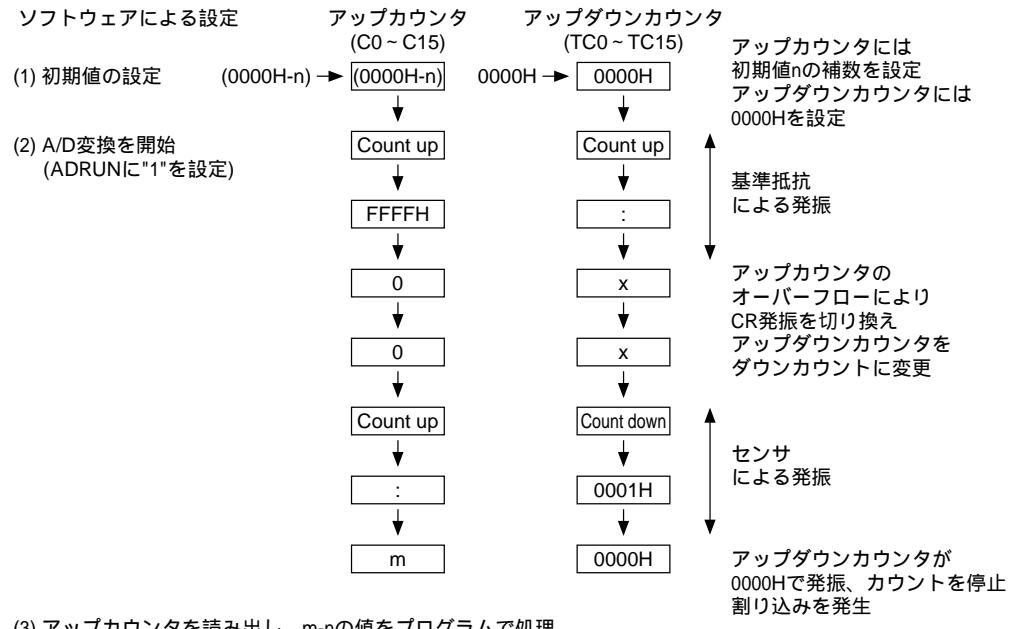

A/D変換を開始する前にアップダウンカウンタTC0～TC15を"0000H"に設定しておくことにより、基準抵抗の発振時間と同じ時間センサの発振を行いますので、発振周波数の差をアップカウンタC0～C15のカウント値から得ることができます。

基準抵抗の発振時間はアップカウンタC0～C15がオーバーフローするまでの時間となるため、A/D変換を開始するまえに適当な初期値を設定しておく必要があります。この初期値を小さな値にしておくとカウント期間が長くされ、検出の精度は上がります。同様にアップダウンカウンタTC0～TC15の入力クロックに65kHzを選択した場合も精度が上がります。ただし、通常は測定精度の関係からCR発振周波数をアップダウンカウンタTC0～TC15のクロックの周波数よりも低く設定するため、基準抵抗の発振をカウント中にアップダウンカウンタTC0～TC15がオーバーフローする可能性があります。このオーバーフローが発生した場合、その時点でCR発振およびA/D変換を終了します。なお、この場合もアップダウンカウンタの値が"0000H"になるため、割り込みが発生します。ただし、この割り込みがオーバーフローによるものか、正常に終了したものかの判定が行えません。オーバーフローした場合は正しい結果が得られませんので注意してください。

また、サーミスタによる測定範囲をどの程度に設定するか、およびその範囲のどの辺に基準抵抗値を設定するかによっても初期値の設定が変わってきます。

以上の点に注意して初期値の設定を行ってください。

初期値は補数(0000Hから減算した値)に変換してアップカウンタC0～C15に設定します。A/D変換が終了したアップカウンタC0～C15の内容がセンサが検出したデータとなりますので、その値と補数に変換する前の初期値との差をプログラムで処理して目的の数値を算出してください。

以上の動作を図4.8.2.3に示します。

図4.8.2.3 A/D変換のシーケンス

- 注: • ADRUNに"1"を設定する前に、TH1またはTH2を選択しておく必要があります(デフォルトはTH1)。

- アップカウンタC0~C15の初期値は、測定範囲およびアップダウンカウンタTC0~TC15のオーバーフローに注意して設定してください。

- A/D変換終了後にアップダウンカウンタTC0~TC15を読み出した場合、"0000H"になっていない場合があります。これはアップカウンタにカウント動作終了の制御信号を出力した後にダウンカウントのクロックが入力されることがあるためで、A/D変換終了のタイミングがずれたためではありません。

### 4.8.3 割り込み機能

A/DコンバータにはA/D変換終了時に割り込みを発生させる機能があります。

アップダウンカウンタTC0～TC15のカウントダウンが進み"0000H"になった時点で双方のカウンタのカウント動作が停止し、次のクロックの立下りエッジで割り込み要因フラグIADが"1"にセットされます。アップダウンカウンタTC0～TC15がアップカウント中にオーバーフローした場合は、カウンタが"0000H"になった直後のクロックの立上りエッジで割り込み要因フラグIADが"1"にセットされます。

この割り込み要因は割り込みマスクレジスタEIADによるマスクが可能で、EIADを"1"に設定している場合にCPUに対して割り込みが発生します。EIADを"0"に設定している場合、割り込み要因フラグは"1"にセットされますが、CPUに対する割り込みは発生しません。なお、割り込み要因フラグは読み出しにより"0"にリセットされます。

図4.8.3.1にA/Dコンバータの割り込みタイミングを示します。

図4.8.3.1 A/Dコンバータの割り込みタイミング

#### 4.8.4 A/Dコンバータの使用例

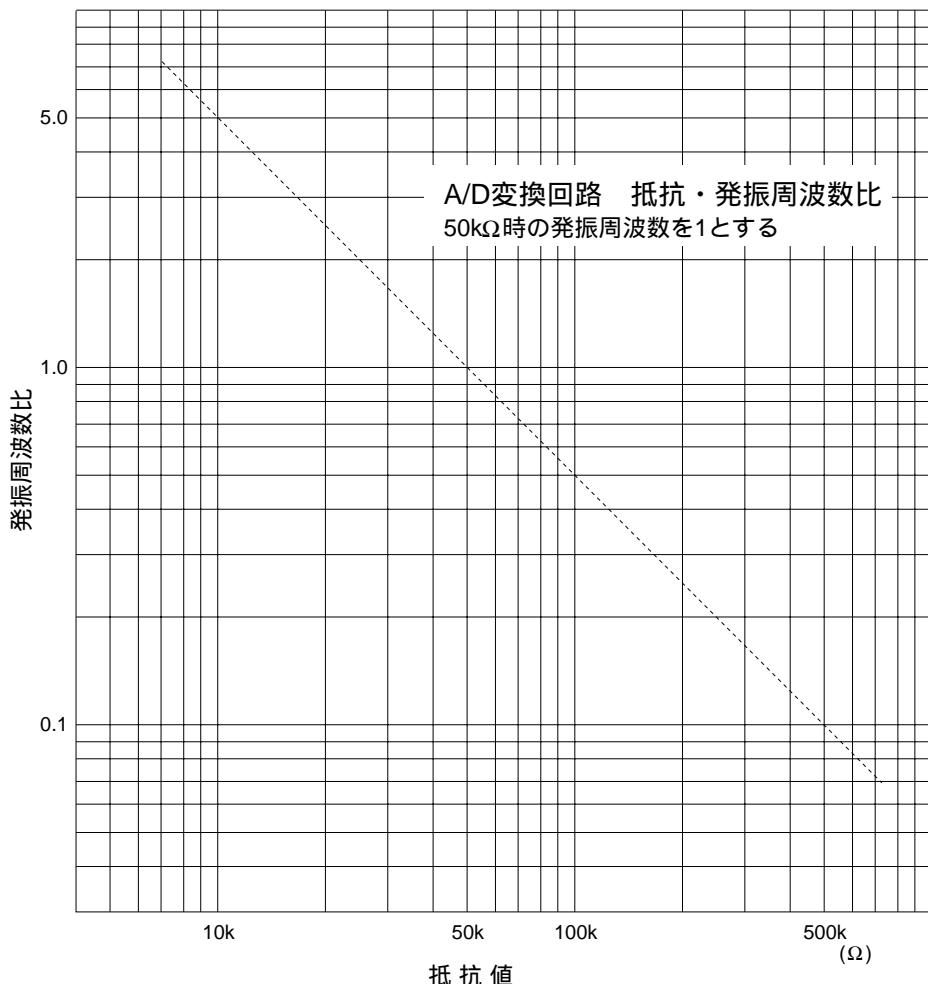

本A/Dコンバータはセンサにサーミスタを用いることにより温度測定を行うことができます。以下に、この温度測定を行う場合を例に、接続する素子およびカウンタの設定を示します。

- 例: -20 ~ 70 の温度測定

基準抵抗 ..... 49.8kΩ

サーミスタ ..... 50kΩ

発振用コンデンサ .... 2,200pF

以上の素子を接続することにより、基準抵抗による発振周波数が約10kHz、サーミスタによる発振周波数は-20 ~ 70 で約1kHz ~ 50kHzに変化します。

基準抵抗は温度が25 におけるサーミスタの抵抗値に合わせてあります。

なお、図4.8.4.1にA/D変換時の抵抗・発振周波数比TYPを示します。

図4.8.4.1 抵抗・発振周波数比

### 4.8.5 A/Dコンバータの制御

表4.8.5.1にA/Dコンバータの制御レジスタを示します。

表4.8.5.1 I/Oメモリ (A/Dコンバータ)

| アドレス | レジスタ |      |      |       | Name | Init <sup>*1</sup> | 注釈    |                               |

|------|------|------|------|-------|------|--------------------|-------|-------------------------------|

|      | D3   | D2   | D1   | D0    |      |                    | 1     | 0                             |

| 0E4H | TC3  | TC2  | TC1  | TC0   | TC3  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC3        |

|      |      |      |      | R/W   | TC2  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC2        |

|      |      |      |      |       | TC1  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC1        |

|      |      |      |      |       | TC0  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC0 (LSB)  |

| 0E5H | TC7  | TC6  | TC5  | TC4   | TC7  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC7        |

|      |      |      |      | R/W   | TC6  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC6        |

|      |      |      |      |       | TC5  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC5        |

|      |      |      |      |       | TC4  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC4        |

| 0E6H | TC11 | TC10 | TC9  | TC8   | TC11 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC11       |

|      |      |      |      | R/W   | TC10 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC10       |

|      |      |      |      |       | TC9  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC9        |

|      |      |      |      |       | TC8  | - *3               | 1     | 0<br>アップダウンカウンタデータ TC8        |

| 0E7H | TC15 | TC14 | TC13 | TC12  | TC15 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC15 (MSB) |

|      |      |      |      | R/W   | TC14 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC14       |

|      |      |      |      |       | TC13 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC13       |

|      |      |      |      |       | TC12 | - *3               | 1     | 0<br>アップダウンカウンタデータ TC12       |

| 0F5H | C3   | C2   | C1   | C0    | C3   | - *3               | 1     | 0<br>アップカウンタデータ C3            |

|      |      |      |      | R/W   | C2   | - *3               | 1     | 0<br>アップカウンタデータ C2            |

|      |      |      |      |       | C1   | - *3               | 1     | 0<br>アップカウンタデータ C1            |

|      |      |      |      |       | C0   | - *3               | 1     | 0<br>アップカウンタデータ C0 (LSB)      |

| 0F6H | C7   | C6   | C5   | C4    | C7   | - *3               | 1     | 0<br>アップカウンタデータ C7            |

|      |      |      |      | R/W   | C6   | - *3               | 1     | 0<br>アップカウンタデータ C6            |

|      |      |      |      |       | C5   | - *3               | 1     | 0<br>アップカウンタデータ C5            |

|      |      |      |      |       | C4   | - *3               | 1     | 0<br>アップカウンタデータ C4            |

| 0F7H | C11  | C10  | C9   | C8    | C11  | - *3               | 1     | 0<br>アップカウンタデータ C11           |

|      |      |      |      | R/W   | C10  | - *3               | 1     | 0<br>アップカウンタデータ C10           |

|      |      |      |      |       | C9   | - *3               | 1     | 0<br>アップカウンタデータ C9            |

|      |      |      |      |       | C8   | - *3               | 1     | 0<br>アップカウンタデータ C8            |

| 0F8H | C15  | C14  | C13  | C12   | C15  | - *3               | 1     | 0<br>アップカウンタデータ C15 (MSB)     |

|      |      |      |      | R/W   | C14  | - *3               | 1     | 0<br>アップカウンタデータ C14           |

|      |      |      |      |       | C13  | - *3               | 1     | 0<br>アップカウンタデータ C13           |

|      |      |      |      |       | C12  | - *3               | 1     | 0<br>アップカウンタデータ C12           |

| 0F1H | CHTH | 0    | 0    | ADRUN | CHTH | 0                  | TH2   | A/Dチャンネル選択                    |

|      |      |      |      | R/W   | 0    |                    |       | *5                            |

|      |      |      |      |       | 0    | Start              | Stop  | A/D変換 Start/Stop              |

| 0FEH | 0    | 0    | 0    | ADCLK | 0    |                    |       | *5                            |

|      |      |      |      | R/W   | 0    |                    |       | *5                            |

|      |      |      |      |       | 0    | 65kHz              | 32kHz | A/Dクロック選択 65kHz/32kHz         |

| 0ECH | 0    | 0    | 0    | EIAD  | 0    |                    |       | *5                            |

|      |      |      |      | R/W   | 0    |                    |       | *5                            |

|      |      |      |      |       | 0    | Enable             | Mask  | 割り込みマスクレジスタ(A/D)              |

| 0FOH | 0    | 0    | 0    | IAD   | 0    |                    |       | *5                            |

|      |      |      |      | R     | 0    |                    |       | *5                            |

|      |      |      |      |       | 0    | Yes                | No    | 割り込み要因フラグ(A/D)                |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

**TC0 ~ TC15: アップダウンカウンタ (0E4H ~ 0E7H)**

基準抵抗と可変抵抗素子のCR発振時間を合わせるためのアップダウンカウンタで、4ビット単位で書き込み/読み出しが可能です。

基準抵抗による発振時はアップカウントを行い、センサによる発振時は基準抵抗の発振によりカウントアップされた値から"0000H"までのダウンカウントを行います。

双方のカウント時間を合わせるため、A/D変換を開始する前にこのカウンタに"0000H"を書き込んでおく必要があります。

イニシャルリセット時、このカウンタの内容は不定となります。

**C0 ~ C15: アップカウンタ (0F5H ~ 0F8H)**

CR発振クロックによりカウントアップするカウンタで、4ビット単位で書き込み/読み出しが可能です。

このカウンタには、基準抵抗による発振でカウントするクロック数の補数をA/D変換を開始させる前に書き込んでおきます。

A/D変換を開始させると、はじめに基準抵抗による発振クロックによって、設定した初期値からアップカウントを行います。カウンタがオーバーフローしカウント値が"0000H"になった時点で発振がセンサ側に切り換わり、そのクロックによりカウントを継続します。基準抵抗の発振によるカウント時間はアップダウンカウンタTC0 ~ TC15で計数されており、それと同じ時間でアップカウンタC0 ~ C15のカウントが停止するようになっています。停止したカウンタの値を読み出すことによって基準抵抗との差が得られますので、それをプログラムで処理して目的の数値を算出してください。

なお、A/D変換前に書き込む初期値は、測定範囲およびアップダウンカウンタTC0 ~ TC15のオーバーフローに注意して設定してください。

イニシャルリセット時、このカウンタの内容は不定となります。

**ADCLK: 入力クロック選択 (0FEH D0)**

アップダウンカウンタTC0 ~ TC15の入力クロックを選択します。

"1"書き込み: 65kHz

"0"書き込み: 32kHz

読み出し: 可能

アップダウンカウンタTC0 ~ TC15のカウントを行う、遅倍回路の出力クロックを選択します。

ADCLKに"1"を書き込むことによりOSC1クロックを遅倍した65kHzが選択されます。"0"を書き込んだ場合はOSC1クロックの周波数32kHzが選択されます。

65kHzを選択した場合、A/D変換の精度が上がります。ただし、CR発振のカウント中にアップダウンカウンタTC0 ~ TC15がオーバーフローしないように、アップカウンタC0 ~ C15に設定する初期値に注意してください。

イニシャルリセット時、このレジスタは"0"に設定されます。

**ADRUN: A/D変換START/STOP (0F1H D0)**

A/D変換を開始させます。

"1"書き込み: A/D変換START

"0"書き込み: A/D変換STOP

読み出し: 可能

ADRUNに"1"を書き込むことによりA/D変換を開始します。A/D変換中はこのレジスタに"1"が保持され、A/D変換が終了した時点で"0"に設定されます。

A/D変換中にADRUNに"0"を書き込んだ場合は、その時点でA/D変換を中止します。

イニシャルリセット時、アップダウンカウンタのオーバーフロー時および測定終了時はこのレジスタが"0"に設定されます。

#### CHTH: A/Dチャンネル選択 (0F1H D3)

A/Dコンバータのチャンネルを選択します。

"1"書き込み: TH2

"0"書き込み: TH1

読み出し: 可能

A/D変換を開始する前に、TH1またはTH2のどちらのセンサの変換を行うかについてCHTHで選択しておく必要があります。

イニシャルリセット時、このレジスタは"0"に設定されます。

#### EIAD: 割り込みマスクレジスタ (0ECH D0)

A/Dコンバータの割り込みについてマスクするかしないかを選択します。

"1"書き込み: 割り込み許可

"0"書き込み: 割り込みマスク

読み出し: 可能

EIADに"1"を書き込むことによりA/Dコンバータ割り込みが許可され、"0"を書き込むことにより割り込みがマスクされます。

イニシャルリセット時、このレジスタは"0"に設定されます。

#### IAD: 割り込み要因フラグ (0F0H D0)

A/Dコンバータ割り込みの発生状態を示すフラグです。

"1"読み出し: 割り込みあり

"0"読み出し: 割り込みなし

書き込み: 無効

IADはA/D変換の終了(アップダウンカウンタがカウントダウン/アップにより"0000H"になった時点)によって"1"にセットされます。このフラグによりA/Dコンバータ割り込みの有無をソフトウェアで判断することができます。なお、このフラグは割り込みマスクレジスタの設定にかかわらず、A/D変換の終了によってセットされます。

このフラグはソフトウェアで読み出すことによってリセットされます。

EI時、割り込み要因フラグの読み込みは可能ですが、以下の場合には注意が必要です。

読み込もうとする割り込み要因フラグに対応する割り込みマスクレジスタの値が"1"にセットされている(マスクされていない)場合、割り込み要因フラグが"1"にセットされるタイミングにより、CPUに対し割り込み要求を発生する場合と、割り込み要因フラグが読み込みによりクリアされ、割り込み要求が発生しない場合があります。

イニシャルリセット時、このフラグは"0"に設定されます。

## 4.9 重負荷保護機能

### 4.9.1 重負荷保護機能の動作

S1C60N05シリーズはブザー出力時や外付けランプ点灯時などのように、電池の負荷が重くなり電源電圧が低下した場合に備えて重負荷保護機能を持っています。この重負荷保護機能が働いているモードを重負荷保護モードと呼びます。

通常の動作モードから重負荷保護モードへは次の場合に移行します。

- ・ソフトウェア(HLMODを"1"にセット)により重負荷保護モードに移した場合

重負荷保護モードでは、LCD系定電圧回路を低消費電流モードから高安定モードに切り換えます。このため、重負荷保護モードでは通常モードより消費電流が多くなります。したがって、必要なとき以外はソフトウェアで重負荷保護モードに設定しないように注意してください。

### 4.9.2 重負荷保護機能の制御

表4.9.2.1に重負荷保護機能の制御レジスタを示します。

表4.9.2.1 I/Oメモリ(重負荷保護機能)

| アドレス | レジスタ  |    |    |    | Name  | Init <sup>*1</sup> | 1     | 0      | 注釈            |

|------|-------|----|----|----|-------|--------------------|-------|--------|---------------|

|      | D3    | D2 | D1 | D0 |       |                    |       |        |               |

| 0FAH | HLMOD | 0  | 0  | 0  | HLMOD | 0                  | Heavy | Normal | 重負荷保護モード      |

|      | R/W   | R  |    |    | 0     |                    |       |        | <sup>*5</sup> |

|      |       |    |    |    | 0     |                    |       |        | <sup>*5</sup> |

|      |       |    |    |    | 0     |                    |       |        | <sup>*5</sup> |

\*1 イニシャルリセット時の初期値

\*4 読み出し直後、リセット(0)

\*2 回路上設定されない

\*5 読み出し時は常時"0"

\*3 不定

\*6 本編参照

HLMOD: 重負荷保護モード ON/OFF (0FAH D3)

重負荷保護モードのON/OFFを制御します。

"1"書き込み: 重負荷保護モードON

"0"書き込み: 重負荷保護モードOFF

読み出し: 可能

HLMODに"1"を書き込むことによりICの動作状態を重負荷保護モードにします。

重負荷保護モードでは消費電流が大きくなりますので、必要なとき以外はソフトウェアにより重負荷保護モードに設定しないでください。

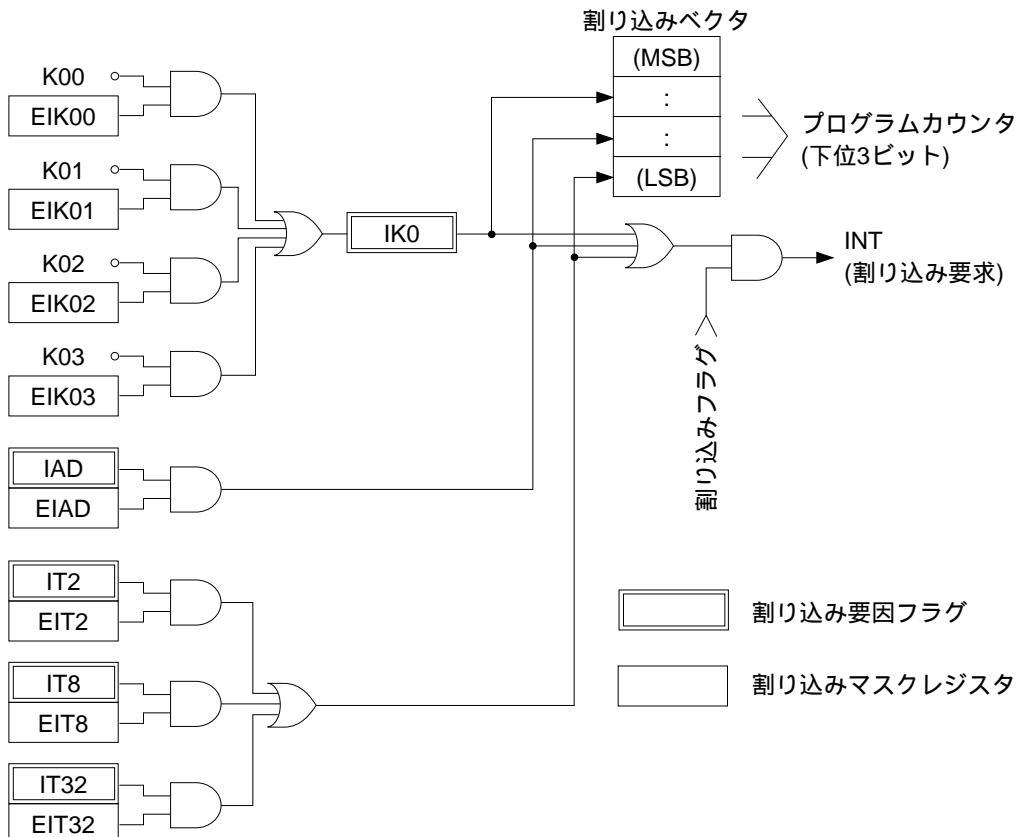

## 4.10 割り込みとHALT

S1C60N05シリーズには以下の割り込みが設定されており、それぞれマスクが可能です。

- 外部割り込み:    • 入力割り込み (1系統)

- 内部割り込み:    • タイマ割り込み (1系統)

• A/Dコンバータ割り込み (1系統)

割り込みを許可するためには割り込みフラグを"1"(EI)にセットし、あわせて必要な割り込みマスクレジスタも"1"(許可)にセットする必要があります。

割り込みが発生すると割り込みフラグは自動的に"0"(DI)にリセットされ、以後の割り込みは禁止されます。

CPUはHALT命令が入力されるとCPU動作クロックを停止し、HALT状態になります。

CPUのHALT状態からの再起動は割り込み要求が発生することにより行われます。

図4.10.1に割り込み回路の構成を示します。

図4.10.1 割り込み回路の構成

#### 4.10.1 割り込み要因

割り込みが発生する要因を表4.10.1.1に示します。

それぞれの割り込み要因により、対応する割り込み要因フラグは"1"にセットされます。

CPUに対する割り込みは次の2つの条件が成立している場合に、割り込み要因フラグが"1"になると発生します。

- 対応する割り込みマスクレジスタが"1" (指定の割り込みを許可)

- 割り込みフラグが"1" (EI状態)

割り込み要因フラグは読み出し専用のレジスタですが、フラグを読み出すことにより"0"にリセットされます。

イニシャルリセット時、割り込み要因フラグは"0"にリセットされます。

**注:** EI時、割り込み要因フラグの読み込みは可能ですが、以下の場合には注意が必要です。

読み込もうとする割り込み要因フラグに対応する割り込みマスクレジスタの値が"1"にセットされている(マスクされていない)場合、割り込み要因フラグが"1"にセットされるタイミングにより、CPUに対し割り込み要求を発生する場合と、割り込み要因フラグが読み込みによりクリアされ、割り込み要求が発生しない場合があります。

特に、同一アドレスに複数の割り込み要因フラグがある場合には、細心の注意が必要です。

表4.10.1.1 割り込み要因

| 割り込み要因                      | 割り込み要因フラグ      |

|-----------------------------|----------------|

| 計時タイマ2Hz立下りエッジ              | IT2 (0EFH D2)  |

| 計時タイマ8Hz立下りエッジ              | IT8 (0EFH D1)  |

| 計時タイマ32Hz立下りエッジ             | IT32 (0EFH D0) |

| A/Dコンバータ A/D変換終了            | IAD (0F0H D0)  |

| 入力データ (K00 ~ K03)<br>立上りエッジ | IK0 (0EDH D0)  |

#### 4.10.2 割り込みの個別マスク

割り込み要因フラグは対応する割り込みマスクレジスタによってマスクできます。

割り込みマスクレジスタはリード/ライト可能なレジスタで、"1"書き込みでイネーブル(割り込み許可)、"0"書き込みでマスク(割り込み禁止)となります。

イニシャルリセット時、割り込みマスクレジスタは"0"にリセットされます。

表4.10.2.1 割り込みマスクレジスタと割り込み要因フラグ

| 割り込みマスクレジスタ       | 割り込み要因フラグ      |

|-------------------|----------------|

| EIT2 (0EBH D2)    | IT2 (0EFH D2)  |

| EIT8 (0EBH D1)    | IT8 (0EFH D1)  |

| EIT32 (0EBH D0)   | IT32 (0EFH D0) |

| EIAD (0ECH D0)    | IAD (0F0H D0)  |

| EIK03 * (0E8H D3) | IK0 (0EDH D0)  |

| EIK02 * (0E8H D2) |                |

| EIK01 * (0E8H D1) |                |

| EIK00 * (0E8H D0) |                |

\* 入力ポートは端子ごとに割り込みマスクレジスタがあります。

#### 4.10.3 割り込みベクタ

CPUに対して割り込みが発生すると、CPUは割り込み処理を開始します。

割り込み処理は実行中の命令を終了後、以下の手順で行われます。

- ① 次に実行すべきプログラムのアドレスデータ(プログラムカウンタの値)をスタック領域に退避

- ② 割り込み要求による割り込みベクタの値(1ページ、01H ~ 07H)をプログラムカウンタにセット

- ③ 指定されたアドレスのプログラムを実行(ソフトウェアによる割り込み処理ルーチンの実行)

注: ①、②の処理にCPUシステムクロックの12周期分の時間を要します。

#### 4.10.4 割り込みの制御

表4.10.4.1に割り込みの制御レジスタを示します。

表4.10.4.1 I/Oメモリ(割り込み)

| アドレス | レジスタ  |       |       |       | Name  | Init <sup>*1</sup> | 1      | 0    | 注釈                                    |

|------|-------|-------|-------|-------|-------|--------------------|--------|------|---------------------------------------|

|      | D3    | D2    | D1    | D0    |       |                    |        |      |                                       |

| 0E8H | EIK03 | EIK02 | EIK01 | EIK00 | EIK03 | 0                  | Enable | Mask | 割り込みマスクレジスタ K03                       |

|      |       |       |       | R/W   | EIK02 | 0                  | Enable | Mask | 割り込みマスクレジスタ K02                       |

|      |       |       |       |       | EIK01 | 0                  | Enable | Mask | 割り込みマスクレジスタ K01                       |

|      |       |       |       |       | EIK00 | 0                  | Enable | Mask | 割り込みマスクレジスタ K00                       |

| 0EBH | 0     | EIT2  | EIT8  | EIT32 | 0     |                    |        |      | <sup>*5</sup>                         |

|      |       |       |       | R/W   | EIT2  | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 2Hz                  |

|      |       |       |       |       | EIT8  | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 8Hz                  |

|      |       |       |       |       | EIT32 | 0                  | Enable | Mask | 割り込みマスクレジスタ(タイマ) 32Hz                 |

| 0ECH | 0     | 0     | 0     | EIAD  | 0     |                    |        |      | <sup>*5</sup>                         |

|      |       |       |       | R/W   | 0     |                    |        |      | <sup>*5</sup>                         |

|      |       |       |       |       | EIAD  | 0                  | Enable | Mask | 割り込みマスクレジスタ(A/D)                      |

|      |       |       |       |       |       |                    |        |      | <sup>*5</sup>                         |

| 0EDH | 0     | 0     | 0     | IK0   | 0     |                    |        |      | <sup>*5</sup>                         |

|      |       |       |       | R     | 0     |                    |        |      | <sup>*5</sup>                         |

|      |       |       |       |       | IK0   | 0                  | Yes    | No   | 割り込み要因フラグ(K00 ~ K03)<br><sup>*4</sup> |

|      |       |       |       |       |       |                    |        |      | <sup>*5</sup>                         |

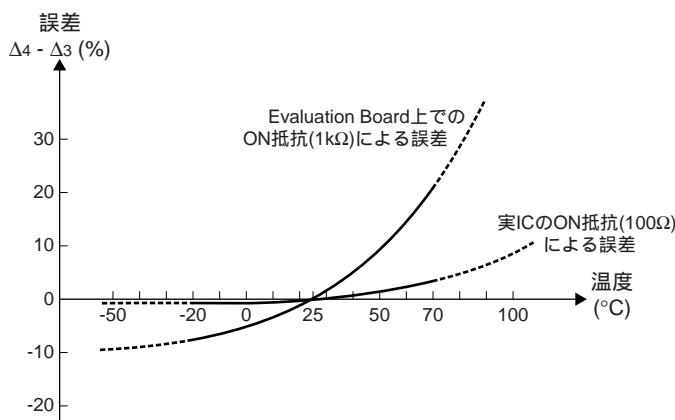

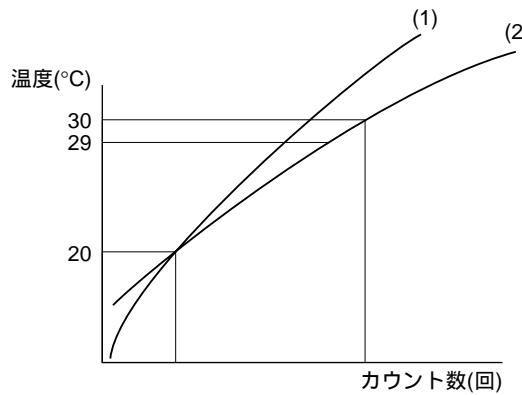

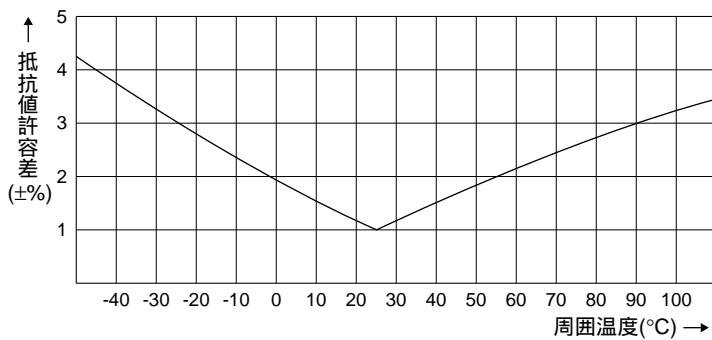

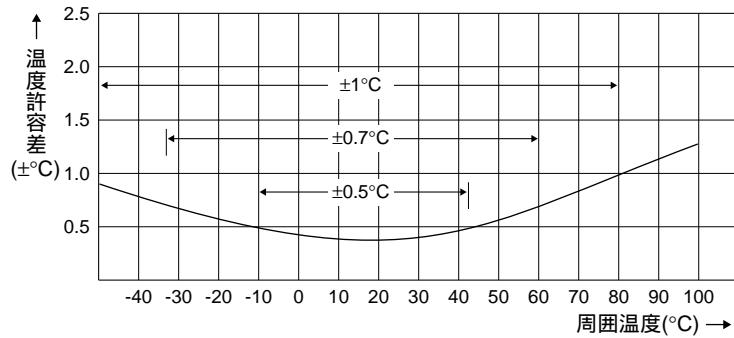

| 0EFH | 0     | IT2   | IT8   | IT32  | 0     |                    |        |      | <sup>*5</sup>                         |